# **Evolution of the MOS Transistor—From Conception to VLSI**

CHIH-TANG SAH, FELLOW, IEEE

Invited Paper

Historical developments of the metal-oxide-semiconductor fieldeffect-transistor (MOSFET) during the last sixty years are reviewed, from the 1928 patent disclosures of the field-effect conductivity modulation concept and the semiconductor triodes structures proposed by Lilienfeld to the 1947 Shockley-originated efforts which led to the laboratory demonstration of the modern silicon MOSFET thirty years later in 1960. A survey is then made of the milestones of the past thirty years leading to the latest submicron silicon logic CMOS (Complementary MOS) and BICMOS (Bipolar-Junction-Transistor CMOS combined) arrays and the three-dimensional and ferroelectric extensions of Dennard's one-transistor dynamic random access memory (DRAM) cell. Status of the submicron lithographic technologies (deep ultra-violet light, X-ray, electron-beam) are summarized. Future trends of memory cell density and logic gate speed are projected. Comparisons of the switching speed of the silicon MOSFET with that of silicon bipolar and GaAs field-effect transistors are reviewed. Use of high-temperature superconducting wires and GaAs-on-Si monolithic semiconductor optical clocks to break the interconnect-wiring delay barrier is discussed. Further needs in basic research and mathematical modeling on the failure mechanisms in submicron silicon transistors at high electric fields (hot electron effects) and in interconnection conductors at high current densities and low as well as high electric fields (electromigration) are indicated.

## I. Introduction

Some of the geometrics and basic concepts underlying the MOS transistor or the metal-oxide-semiconductor field-effect transistor (MOSFET) were described sixty years ago by Julius Edgar Lilienfeld of Brooklyn and Cedarhurst, NY, in the first two of his three patents [1]–[3]. (A list of acronyms and abbreviations follows.) Applications of Lilienfeld's three patents were filed with the United States Patent Office on October 8, 1926 [1], March 28, 1928 [2], and December 8, 1928

Manuscript received August 1, 1986; revised July 14, 1988. The research was supported in part by two sequential grants from the U.S. National Science Foundation, three sequential and ongoing contracts with the Semiconductor Research Corporation concerning silicon MOS aging and failure mechanisms as well as reliability physics, chemistry, and modeling, and an unrestricted Intel grant for the author's stipend of the summer of 1988.

The author was with the Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, IL. He is now with the Department of Electrical Engineering, University of Florida, Gainesville, FL 32611, USA.

IEEE Log Number 8823837.

[3]. They were granted in 1930, 1933 and 1932, respectively. Lilienfeld was born in Poland in 1882 and was a professor of physics at the University of Leipzig from 1910 to 1926. He immigrated to the United States in 1926 and was the director of research of the Ergon Research Laboratory at Malden, MA. He became a naturalized U.S. citizen in 1935, retired to the Virgin Islands soon after with his American-born wife, the former Beatrice Ginsberg, and died on August 28, 1963, at the age of 81 [4].

In order to see how Lilienfeld arrived at his MOS transistor concepts and structures, we first give a summary of the analyses of the patents, using modern semiconductor terminology and the semiconductor device theory of Shockley. My description is helped by the modern knowledge of basic transistor theory developments since 1947. As we shall see, field-effect transistor structures and several other transistors were described by Lilienfeld's first two patents and a later (1935) patent by Heil [5], except the p-n junction field-effect and minority-carrier injection bipolar transistors which were invented and experimentally demonstrated by Bardeen, Brattain, Shockley and their colleagues at the Bell Telephone Laboratories during 1947-1952 [6]. My analyses show that there are five transistor structures in the three Lilienfeld patents. We have no evidence, however, if any of the transistors proposed by Lilienfeld were built and worked.

The first Lilienfeld patent [1] gives the **MESFET** (Metal/Semiconductor FET).

The second Lilienfeld patent gives two transistor structures [2]. They are derived from the MESFET of the first patent by inserting an insulator layer between the metal gate and the semiconductor film resulting in the depletion-mode MOSFET and the GMSR (Gated Metal/Semiconductor Rectifier Transistor or GMSRT). I call the GMSR a transistor instead of just a gated diode, a term I used in 1962 (Surface Controlled Diode or Surface Controlled Tetrode) since it is a three-terminal device although it may not give power amplification except under certain conditions as demonstrated by the first confirmed amplification in a solid state device in Brattain's December 4, 1947 experiment. (See Fig. 13 on p. 609 and text on pp. 609 and 611 of Shockley's review [6].) I use the term 'transistor' in this paper as a generic name

0018-9219/88/1000-1280\$01.00 © 1988 IEEE

for solid-state electron devices with three or more terminals. The technical definition used by Bell Lab researchers and IEEE is that it must have a power gain greater than unity. Brattain's experiment was on p-type silicon with a thin surface p-n junction from an n-type surface inversion layer, suggested by Bardeen and Shockley in the first transistor patent filed by Bell Labs in 1948 [7], described in Bardeen's Nobel lecture, and reviewed in 1976 by Shockley on the invention of the bipolar junction transistor [6]. The gated p-n junction diode structure I used in 1962 was given as Fig. 1 of Shockley's June 26, 1948 bipolar transistor patent [8], and also Brattain's December 4, 1947 notebook figure, part II, given in Fig. 13 of Schockley's review [6], unknown to me in 1962. I will discuss the recent results later.

The third Lilienfeld patent [3] gives two more transistor structures, the Metal Base Transistor or the Semiconductor/Metal/Semiconductor Transistor (SMST), and the Schottky-Barrier-Emitter/Schottky-Barrier-Collector Transistor or the Metal/Semiconductor/Metal Transistor (MSMT). These two transistors do not operate on the conductivity modulation or field-effect principle as do the three transistors of the first two patents.

In addition, several integrated amplifier structures consisting of different intergrated configurations of these five basic transistor structures were also given by Lilienfeld. For examples, the second patent gives two integrated structures, the first containing three transistors (MESFET, MOSFET, GMSR), and the second containing a GMSR transistor and a metal-semiconductor rectifier (MSR) diode with a distributed and voltage dependent resistor, and the third patent gives a five-layer MPMPM transistor where M is Metal and P (p-type semiconductor) is  $Cu_2S$ .

Circuit diagrams with dc bias voltages are also given by Lilienfeld with the correct polarities for proper operation as an amplifier although he was limited to batteries with negative common. He even gives a complete receiver circuit in the first patent using four MESFETs as RF and AF amplifiers and a MSR as the detector.

The patents describe in considerable detail methods for making the thin-film transistor structures and Lilienfeld's experiences on how the transistor characteristics are affected by varying the fabrication conditions, as well as such characteristics as the magnitude of the breakdown voltage, the reproducibility of the Schottky barrier or metalsemiconductor rectifier diode and the goodness of the ohmic contacts. Copper sulfide is mentioned as the 'compound' or semiconductor film in the first (1926) patent, which also gives two methods each on deposition of the copper film (by spattering or thermal evaporation in vacuum and by deposition from a colloidal suspension) and sulphuration of the film (in sulfur vapor or in carbon bisulphide liquid). In the first patent, which gives the MES-FET, the 0.0001" or 2.5-μm-long aluminum gate is very ingeniously made by squeezing together an aluminum foil between the two edges of a broken glass slide on which the copper film is then deposited and sulphurized. Copper sulfide, copper oxide, and lead oxide are specifically mentioned in the second patent as possible candidates for the semiconductor compound film by sulfuration or oxidation. The second patent also gives the chemical formulae explicitly,  $Cu_2S$ ,  $Cu_2O$  and  $PbO_2$  and describes  $Cu_2S$  as copper disulphide while the modern names are cuprous sulfide and cuprous oxide. They are known today to be p-type semiconductors due to the copper vacancy produced during sulfuration and oxidation and have a rather low hole mobility, about 1 cm<sup>2</sup>/V-s in Cu<sub>2</sub>S.

My foregoing description of Lilienfeld's transistors relies on an analysis of his transistor structures using the concepts of hole, p-type semiconductor and energy bands. These concepts were not used by Lilienfeld, which prevented him from developing the basic physics of these transistors. They were not used probably because they were just developed by A. H. Wilson in 1931 [9], [10] after Lilienfeld's patent applications were filed in 1926 and 1928. However, Lilienfeld understands well a key concept, conductivity modulation by a transverse electric field, which he repeatedly uses to describe signal amplification of the transistors in the patents. He uses this concept to explain the operation of both the MESFET in the first patent and MOS-FET in the second patent. In addition, he knows well where to place the rectifying junctions and the ohmic junctions for contacts to the external circuits. The proliferation of transistor structures in Lilienfeld's patents further indicates his grasp of the conductivity modulation principle and his ability to apply it in combination with ohmic and nonrectifying contacts. However, we still do not know and have no evidence if Lilienfeld made a working, amplifying transistor.

In February 1964, after Lilienfeld had died the previous year, Bottom [11] published a suggestion that the transistor in Lilienfeld's first patent is the bipolar (minority carrier injection) junction transistor. Bottom's erroneous conclusion was made under the false assumption that the compound semiconductor film, Cu<sub>2</sub>S, is n-type and that aluminum had diffused through the thin film to form a p-type region during the pulsed 'forming' operation while making the transistor. This was corrected by Johnson [12], the discoverer of the Johnson Noise. Johnson pointed out that Cu<sub>2</sub>S is p-type and that the Al/Cu<sub>2</sub>S Schottky diode was known in the 1930s as a rectifier with high resistance when Al is biased positively relative to Cu<sub>2</sub>S. Johnson also reported that he had tried to duplicate the structure but could not get amplification or even modulation. He attributed the failure to the low mobility of holes (1 cm<sup>2</sup>/V-s) and the trapping of holes at the surface states and further stated that Lilienfeld's receiver could not have worked due to the transistor's frequency limitation. But, Lilienfeld stated a gate length of 0.0001" or  $2.5 \,\mu\mathrm{m}$  which would have given a hole transit time of 62 ns or a cutoff frequency of 2.5 MHz at a drain-to-source voltage of 1 V for a mobility of 1 cm<sup>2</sup>/V-s. Even high trap density would not have increased the transit time since the traps are already mostly filled by the trapped holes. Thus, Johnson proved it was not a bipolar transistor. It is uncertain if the MESFET nature of Lilienfeld's first transistor would have made Johnson's experiments successful since the impurity ion density in the Cu<sub>2</sub>S film and the surface state density at the glass-substrate|Cu<sub>2</sub>S-film interface could also be too

A patent application, filed by Oskar Heil, a native of Germany, with the British Patent Office on March 4, 1935 and granted on December 6, 1935 [5] provides the first description of the MOSFET operation using modern semiconductor concepts of electrons and holes. Both n-type and p-type semiconductor films were specified with Te, I, Cu<sub>2</sub>O and  $V_2O_5$  as explicit examples. The MOSFET structure described by Heil is a long thin semiconductor film whose two ends

are covered by a metal stripe, to serve as the drain and the source contacts. It also has a gate metal electrode overlapping but insulated from the semiconductor film and the drain and source metal stripes to modulate the conductance of the semiconductor film. Both the single gate over one surface of the semiconductor film and two gates over both surfaces of the semiconductor film are given. Heil's Metal/n-film/Metal (M/n/M) structure using an n-type semiconductor film is the modern depletion mode MOSFET just like Lilienfeld's Au/p/Au which uses ohmic metal (Au) contact to the p-Cu<sub>2</sub>S. Heils' M/p/M structure, using a p-type semiconductor film, would be the modern inversion-channel or enhancement-mode MOSFET since its souce and drain contacts are metal/p-semiconductor rectifying junctions. The enhancement-mode MOSFET is not contained in Lilienfeld's three patents whose transistor structures have at most one rectifying junction. However, Heil did not explain how his M/p/M inversion-channel transistor would work. Thus, I conclude that he did not recognize the necessity of having a gate-voltage induced surface inversion  $channel\,(n\text{-}channel\,for\,the\,M/p/M\,transistor)\,in\,order\,to\,have$ amplification. The inversion channel idea was first recognized by Bardeen in 1947 [6], [7]. It led to the invention of several inversion channel field-effect transistors, including a predecessor of the bipolar point-contact transistor by Bardeen and Brattain in 1948 [13] and the modern MOSFET with diffused source and drain junctions, all of which we will discuss later.

One is curious about what motivated Lilienfeld and provided him the precedents that led him to so many transistor structures. It seems that Lilienfeld's earlier research on electron emission in vacuum, published in a 1920 Leipzig university journal [12], and his experimental expertise in vacuum tube electronics must have led him to invent the solid state devices. More recent examples of transistor inventions [7], [8] based on previous or related knowledge in vacuum tubes were those of Bardeen, Brattain, and Shockley, as described by Bardeens's Nobel lecture [7] and by Shockley, whom I quote: "accidents (inventions) favor the prepared mind" [6].

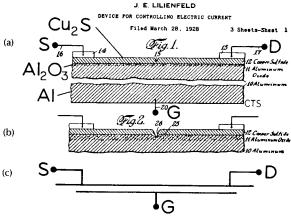

To visualize Lilienfeld's MOSFET inventions, I make use of several figures from his first two patents in the following descriptions.

The first figure of Lilienfeld's first (1926) patent [1] is reproduced in Fig. 1(a) with modern symbols added, D = Drain, S =Source, and G =Gate. An enlarged view of the Al/p- $Cu_2S\,contact\,region\,is\,given\,in\,Fig.\,1(b)\,which\,helps\,to\,ascer$ tain that it is a MESFET or Schottky-gate FET and that Lilienfeld has the proper reverse bias (positive voltage) applied to the gate and (negative voltage) to the drain. One can readily see that the amplifier circuit is a source follower although the placements of the power supplies are somewhat unconventional, probably dictated by having only positive power supplies. Lilienfeld's understanding of the MESFET operation principle is clearly indicated by his patent descriptions on lines 84-86 and 92-96 on page 1 [1]. Some explanations are given in brackets, { }, in the following quote: "the metal foil electrode {14 in Fig. 1(a) where 10 is a broken glass slide} and the compound  $\{p-Cu_2S \text{ film labeled } 15\}$ form an element of unidirectional conductivity {Schottky barrier or metal-semiconductor rectifier} and the thickness of the film is minute {he stated elsewhere in the patent it is 0.0001 inch or 2.5  $\mu$ m $\}$  and that the electrical conductivity

# UNITED STATES PATENT

Fig. 1. (a) Amplifier circuit and dc bias polarity of Lilienfeld's 1926 patent [1] which apparently described the Schottky-barrier gate or metal-semiconductor gate field-effect transistor (MESFET) structure. (b) The enlarged view of the active gate and channel regions of transistor in (a).

is influenced by the electrostatic force applied across the metal foil compound film contact."

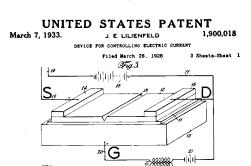

The first two figures of Lilienfeld's second patent [2], the MOSFET patent, are reproduced in Fig. 2(a) and (b). The modern circuit symbol is given in Fig. 2(c). Lilienfeld has all the ingredients of the modern depletion-mode MOSFET. He has an aluminum substrate as the gate electrode, the aluminum oxide as the gate insulator and p-type cuprous sulfide (Cu<sub>2</sub>S) as the semiconductor. His two structures in Fig. 2 are in fact the thin film version of the MOSFET. It is

Patented Mar. 7, 1933 1,900,018

# UNITED STATES PATENT OFFICE

JULIUS EDGAR LILIENFELD, OF BROOKLYN, NEW YORK

DEVICE FOR CONTROLLING ELECTRIC CURRENT

Application flet March 28, 1928. Serial No. 285,372.

Fig. 2. (a), (b) The first two figures in Lilienfeld's 1933 patent [2] giving two structures of the metal-oxide-semiconductor field-effect transistor (MOSFET) he proposed. (c) The modern circuit symbol of the MOSFET.

also a facsimile of the modern depletion mode MOSFET which is now made with a doped conduction channel produced by diffusion, epitaxial growth or ion implantation on the surface of a silicon substrate. It finds applications as an amplifier as well as a "pinched" resistor load in modern silicon integrated circuits. In the thin film version, the conducting film is made by recrystallization of a deposited polycrystalline silicon thin film. This depletion MOSFET has no rectifying junction for the drain and the source in contrast to the enhancement or inversion channel MOSFET. Stability and reproducibility problems have prevented experimental CdS and silicon thin-film transistors from reaching the marketplace so far. However, significant recent development efforts have continued on growing low-defect silicon film by recrystallization of polycrystalline Si films deposited on oxide covered silicon substrate, known today as SOI (Silicon On Insulator). These efforts are motivated by the potential of denser integrated circuits using the third and vertical dimension.

Lilienfeld's understanding of the MOS field-effect transistor operation principle is further demonstrated by the descriptions in his second patent. He states that a high gate electric field is required to operate the transistor, about  $10^7$  V/cm computed from the 100 V and  $10^{-4}$  mm numbers given in the patent. However, the transistor operation voltages he states are about 10 V so that the field is about  $10^6$  V/cm which falls right in the range of modern silicon MOSFET operation. The circuit given in Fig. 3 again shows that Lilienfeld gives the correct bias polarities to operate the transistor as a source-follower amplifier.

An intense electrostatic field is thus set up, or rather rendered available, at the depressed portion 13 of coating 12 throughout its full volume and controls the conductivity of the coating at said portion. Incoming oscillations delivered through the circuit 23 and transformer 22 into the amplifier unit will affect this field to cause thereby changes in said conductivity of the conducting layer, more particularly at its said depressed portion or portion of molecular thickness 13, which changes in conductivity effect variations in the current delivered to the output circuit 19, in manner well understood.

**Fig. 3.** Amplifier circuit, dc bias polarity, and description of the device operation physics given in Lilienfeld's 1933 patent [2] of the metal-oxide-semiconductor field-effect transistor.

A most important feature of Lilienfeld's invention was that he understood the conductivity modulation principle of the transistor, based on electrostatics, at a time when quantum mechanics was in its infancy and semiconducting hole concepts had been just developed by A. H. Wilson in

1931 [9], [10], which Lilienfeld was probably not aware of or did not use. His description in the patent is reproduced in the lower part of Fig. 3, which explicitly states that the conductivity of the thin semiconductor channel region (portion 13) is modulated by the input signal applied to the gate (labeled 20) through the input transformer.

The foregoing analyses of Lilienfeld's three patents and Heil's one patent led me to conclude that Lilienfeld proposed five transistor structures: the MESFET in 1926; and the depletion-mode MOSFET, the gated metal-semiconductor transistor, the metal-base transistor, and the metal-semiconductor-metal transistor, all in 1928. And Heil proposed three transistor structures: the single-gate inversionchannel or enhancement-mode MOSFET, the dual-gate enhancement-mode MOSFET, and the dual-gate depletionmode MOSFET. We must also concede that Lilienfeld understood the conductivity modulation principle and how the depletion-mode MESFET and MOSFET work as is evident by the proliferation of integrated device structures given by him in the patents. However, it is clear that neither Lilienfeld nor Heil recognized the necessity of the surface inversion channel for the operation of the enhancementmode MOSFET proposed by Heil or the gated metal-semiconductor rectifier transistor GMSRT proposed by Lilienfeld. It is also clear that the MESFET and MOSFETs proposed by these two inventors are field-effect devices depending on conductivity modulation, and not on minority-carrier injection. The minority-carrier injection phenomena underlying the basis of the bipolar junction transistor was proposed by Shockley on January 23, 1948 [6], [8], demonstrated by Shive experimentally on February 18, 1948 [6], and suggested in the point-contact transistor patent of Bardeen and Brattain [13] filed on June 17, 1948. The minority carrier injection principle was not known or recognized by Lilienfeld and Heil.

# II. Organization of This Review

In the remaining review, I would like to focus on the highlights of the evolution of the modern silicon MOS transistor by pointing out some of the important milestones in the development and manufacturing technology of the transistor as well as its integrated circuits, by describing some recent advances of the silicon MOS integrated circuit technology, by reviewing some comparative studies on the performance of the silicon MOSFET relative to silicon bipolar junction transistor (BJT) and the compound semiconductor (GaAs) field-effect transistors (FETs), and finally, by indicating some of the current material and technology problems which must be solved to realize the full potential of the Si MOSFET.

The chronological advances of the MOSFET can be divided into three phases: a discovery phase during the first thirty years from 1928 to 1958, a technology development and new device structure invention phase during the next ten years from 1959 to 1968, and the MOS transistor integration and integrated circuit manufacturing phase from 1968 to today. This choice is based on the two singularly most important contributions which affected and started the feverish development efforts in the second and third phases. The choice is clearly unequivocal. Phase I might be thought to have started when Lilienfeld applied for his patents during 1926–1928. The first phase really began around

1947 at Bell Laboratories by Bardeen, Brattain, and Shockley when the basic transistor physics was clearly understood and applied to the new transistor structures. Atalla, Tannenbaum, and Scheibner started the second phase by successfully completing a Bell Laboratory project in 1959 which had the specific objective of finding a passivation method to stabilize the silicon surface using the thermally grown silicon dioxide. And finally, Noyce and Moore started the third phase in 1968, by first inventing the monolithic integrated circuit concept in 1960 and then starting a silicon MOS integrated circuit manufacturing company (Intel) in 1968, resulting in volume delivery in 1970.

These three phases will be discussed in the next three Sections (III, IV, and V). Some anticipations of future advances are then made in the next three Sections (VI, VII, and VIII). Performance trends of the silicon MOSFET are described in Section VI. Comparisons of silicon with gallium arsenide transistors are summarized in Section VII. Research needs to achieve higher speed and density are discussed in Section VIII. A summary is given in Section IX.

In this review of history, I do not explicitly distinguish the invention of a transistor structure or technology from the discovery of a fundamental transistor principle since this distinction is hopefully self-evident in my presentation. However, I want to reiterate two commonly held convictions: i) Recent inventions and new ideas have mostly come directly or indirectly from expanding and improving old ideas and previous knowledge. Even Lilienfeld's 1926-1928 transistor inventions were probably influenced by his earlier (1920) and others' experiences in vacuum tube research. The use of previous knowledge by a prepared mind was amply described and illustrated by Shockley in his descriptions of the invention of the bipolar junction transistor during 1947 [6]. ii) It was not enough just to have invented a new device or apparatus. It takes the ingenuity, persistency, and basic hard work of many dedicated engineers and technicians to put the inventors' ideas into practice in order to produce inexpensive, high performance and reliable integrated circuit chips, systems and consumer products. In the limited space available, I cannot include the many reported and untold dedications, efforts, foresights, and interesting stories, but their importance in propelling the electronics industry to the present state of the art cannot be more recognized and appreciated.

## III. DISCOVERY PHASE (1928-1957)

A milestone chart of the first phase is given in Table 1. There are about fifty important contributions and events during the first phase of thirty years on transistor inventions, new technology demonstrations, discovery of new device principles as well as the founding of two companies, the Shockley Semiconductor Laboratory—Shockley Transistor Corporation in 1955 and the Fairchild Semiconductor Laboratory in 1957 which seeded and initiated the thriving growth of the integrated circuit companies around Palo Alto, CA.

Included also in Table 1 are historical events on the discoveries and developments of the metal-semiconductor rectifier [14]–[16], known today as the Schottky barrier diode, which led to Lilienfeld's MESFET [1] and MOSFET [2]. It includes Shockley's MESFET [6], as well as Bardeen-Brattain's [13] and Shockley's junction-gate FET (JGFET) [6]. It

also includes the Shockley invention of the minority carrier injection concept, the bipolar junction transistor [8], and Bardeen-Brattain's suggestion [13] of the minority-carrier-injection point-contact transistor. These ideas and developments have significantly influenced and impacted the advances of the silicon MOSFET. References are given in the right column of this and later tables. This review will highlight selected events.

# A. Early Transistor Inventions and Working Transistors

The next wave of transistor inventions after Lilienfeld's three patents of 1926-1928 and Heil's patent in 1935 started about 1939 when Shockley, after three years at Bell Telephone Laboratories in search of a solid-state amplifier, was asked to get involved with Brattain's copper-oxide rectifier research [6]. This was interrupted by World War II but Shockley came up with two transistor proposals in 1939 before leaving for the war. The first was the analog transistor made of a grid of oxidized copper wire-screen imbedded into a semiconductor [6] instead of alkali halide crystal, which had been proposed and built a year earlier by Hilsch and Pohl [15] and had a cut-off frequency of about 1 Hz owing to its size of about 1 cm. The second idea from Shockley was the MESFET [6] which was not influenced by Lilienfeld's 1926 patent [1] since it had not been recognized that one of Lilienfeld's 1926 patent disclosures is indeed the MESFET until my analysis made during the preparation of this review.

The transistor innovations started anew after the war when Shockley returned to **BTL** in mid-1945 [6] and Bardeen joined BTL later that year and began a basic study of surface states [17] after Shockley showed him the experimental results by Pearson of very low conductivity modulation of silicon and germanium films in their field-effect experiments [18]. In the following year, 1946, Bardeen completed the basic theory of surface states which accounted for this lack of conductivity modulation.

The thin-film field-effect transistor experiment was reported in detail by Shockley and Pearson in 1948 [18] after initial trials in 1945 [6]. They observed conductivity modulation on p-type germanium, p-type cuprous oxide (Cu<sub>2</sub>O), and n-type silicon. However, the conductivity modulation they measured was a thousand times smaller than expected. They attributed this deficiency to trapping of the modulated charges by surface states according to Bardeen's theory of surface states [17] since low mobility of the deposited film cannot account for such a small conductivity modulation. Their tabulated data gave a surface state density of  $5\times 10^{13}$  states/cm²-eV. This is almost one surface state or dangling silicon bond per ten silicon surface atoms. It is 10000 times higher than that on the oxidized silicon of today's MOS VLSI circuit chips.

At the same time, experiments on Bardeen's gated surface inversion layer [7] was carried out by Brattain with suggestions from Bardeen and Shockley [6]. An electrode insulated by a drop of electrolyte or an insulating film was placed around or next to a point contact over the n-type surface layer of p-type silicon in the first experiment and the p-type surface layer of a n-type Ge block in the second experiment. This structure is similar to the GMST structure described in Lilienfeld's second patent [2] which has a metal/p-Cu<sub>2</sub>S rectifying junction and a Al<sub>2</sub>O<sub>3</sub> dielectric film in place of the

Table 1 Milestones During the Discovery Phase of MOSFET (1926-1957)

| Disclo<br>Date |      | Authors-Inventors           | Institutions              | Device and                                                  | Reduction to |            |

|----------------|------|-----------------------------|---------------------------|-------------------------------------------------------------|--------------|------------|

| Subm.          | Pub. | Development Team            | or Locations <sup>b</sup> | Technology                                                  | Practice     | Ref.       |

| 1926           | 1930 | Lilienfeld                  | NYC                       | MESFET Al/Cu <sup>2</sup> S                                 | ?            | [1]        |

| 1928           | 1933 | Lilienfeld                  | NYC                       | MOSFET Al/Al <sub>2</sub> O <sub>3</sub> /Cu <sub>2</sub> S | ?            | [2]        |

| 1928           | 1933 | Lilienfeld                  | NYC                       | n+-n & p+-p Ohmic Contacts                                  | ?            | [2]        |

| 1928           | 1933 | Lilienfeld                  | NYC                       | GMST Gated MS Junction Diode                                | ?            | [2]        |

| 1928           | 1932 | Lilienfeld                  | NYC                       | SMST, MSMT, MpMpM                                           | ;            | [3]        |

|                | 1931 | Wilson                      | GB                        | Holes and Semiconductor Theory                              |              | [9], [10]  |

| 1934           | 1935 | Heil                        | GER                       | MOSFET Inversion Channel                                    | ?            | [5]        |

|                | 1938 | Davydov                     | USSR                      | P-N Junction Minority Carrier                               |              | [15]       |

|                | 1938 | Hilsch, Pohl                | GER                       | Analog Transistor Ionic                                     |              | [15]       |

|                | 1939 | Davydov                     | USSR                      | M/S Rectifier Diffusion Theory                              |              | [15]       |

|                | 1939 | Schottky                    | GER                       | M/S Rectifier Diffusion Theory                              |              | [15], [16] |

|                | 1939 | Mott                        | GB                        | M/S Rectifier Diffusion Theory                              |              | [15], [16] |

| 1939           | 1976 | Shockley                    | BTL                       | Analog Transistor Semiconductor                             |              | [6]        |

| 1939           | 1976 | Shockley                    | BTL                       | MESFET Proposal                                             |              | [6]        |

| 1940           | 1942 | Scaff, Theuerer, Ohl        | BTL                       | p-n Junction Fabricated                                     |              | [15]       |

|                | 1942 | Bethe                       | MIT                       | M/S Rectifier Thermionic Theory                             |              | [14]       |

|                | 1942 | Bethe                       | MIT                       | Diffused M/S Rectifier Proposal                             |              | [14]       |

|                | 1946 | Serin, Stephens             | MIT                       | Diffused M/S Rectifier                                      | Lab          | [14]       |

| 19MAR          | 1946 | Bardeen                     | BTL                       | Surface State Theory                                        |              | [6], [17]  |

| 24APR          | 1947 | Shockley                    | BTL                       | Minority Carrier Injection Theory                           |              | [6]        |

| 04DEC          | 1947 | Bardeen, Brattain           | BTL                       | Sourceless MOSFET                                           | Lab          | [7]        |

| 1947           | 1948 | Bardeen, Brattain           | BTL                       | Point Contact Transistor                                    | Lab          | [13], [19] |

| 18FEB          | 1948 | Shive                       | BTL                       | BIT First Demonstrated                                      | Lab          | [21]       |

|                | 1948 | Shockley, Pearson           | BTL                       | Conductivity Modulation                                     | Lab          | [18]       |

| 1948           | 1951 | Shockley                    | BTL                       | BJT Diffused Base                                           |              | [8]        |

| 1948           | 1951 | Shockley                    | BTL                       | BJT Grown Junction                                          |              | [8]        |

| 1948           | 1951 | Shockley                    | BTL                       | BJT Integrated pnpnp                                        |              | [8]        |

| 1948           | 1951 | Shockley                    | BTL                       | High/Low n+-n & p+-p Contact                                |              | [8]        |

| 1948           | 1951 | Shockley                    | BTL                       | Negative Resistance Diode                                   |              | [8]        |

|                | 1949 | Shockley                    | BTL                       | BJT and Junction Theory                                     |              | [22]       |

|                | 1950 | Teal, Little                | BTL                       | Grown Ge Crystal                                            | Lab          | [15]       |

|                | 1950 | Hall, Dunlap                | GE                        | Alloy-Diffusion p-n Junction                                | Lab          | [35]       |

|                | 1951 | Scaff, Theuerer             | BTL                       | Gas-Diffusion p-n Junction                                  | Lab          | [36]       |

|                | 1951 | Teal, Spark, Buehlor        | BTL                       | BJT Grown GE Junction                                       | Lab          | [33]       |

|                | 1951 | Shockley                    | BTL                       | Hot Electron Theory                                         |              | [56]       |

|                | 1952 | Teal, Buehler               | BTL                       | Grown Si Crystal                                            | Lab          | [15]       |

|                | 1952 | Shockley, Read, Hall        | BTL-GE                    | Recombination Kinetics Theory                               |              | [51], [52] |

|                | 1952 | Theuerer, Pfann             | BTL                       | Zone Refining of Material                                   | Lab          | [42]       |

|                | 1952 | Shockley                    | BTL                       | Junction FET Theory                                         |              | [30]       |

| 1952           | 1953 | Brattain, Bardeen, Shockley | BTL.                      | Surface State Concepts                                      | Lab          | [23]       |

| 1953           | 1953 | Brown                       | BTL                       | Surface Inversion Channel                                   | Lab          | [31]       |

|                | 1953 | Decay, Ross                 | BTL                       | Junction FET. Built                                         | Lab          | [34]       |

| 1954           | 1958 | Shockley                    | BTL                       | Ion Implanted Junction                                      | Lab          | [47]       |

|                | 1954 | Fuller, Ditzenberger        | BTL.                      | Gas-Diffusion p-n Junction                                  | Lab          | [37]       |

|                | 1954 | Kleinknecht, Seiler         | Siemens                   | Generation Current in Si                                    | Lab          | [53]       |

|                | 1955 | Pell, Roe                   | GE                        | Generation Current in Ge                                    | Lab          | [54]       |

|                | 1955 | Shockley                    | SSL                       | Shockley Semiconductor Founded                              |              |            |

| 1954           | 1957 | Frosch, Derrick             | BTL                       | Oxide Diffusion Mask                                        | Lab          | [39]       |

| 1955           | 1957 | Ross                        | BTL                       | MOSFET Ferroelectric Gate                                   | Lab          | [32]       |

| .,,,,          | 1956 | Tanenbaum, Thomas           | BTL                       | Diffused Diodes & BJT                                       | Lab          | [38]       |

| 1956           | 1957 | Sah, Noyce, Shockley        | STC                       | Recombination Current in Si                                 | Lab          | [55]       |

|                | 1957 | Noyce, Moore + six          | FSC                       | Fairchild Semiconductor Founded                             |              |            |

<sup>&</sup>lt;sup>a</sup>Subm. = Submission or first disclosure date. Pub. = Publication date.

electrolyte. A voltage amplification of 2 and power amplification of 330 was observed on December 8, 1947 [6] and current amplification of 1000 was stated in Shockley's transistor patent [8]. Shockley stated (see p. 613, second paragraph in the left column of [6]) that this was probably the only transistor that had amplified when his bipolar junction transistor patent was filed on June 26, 1948 [8], one week before the public announcement of the point-contact transistor [19], [20]. The point contact transistor has a different structure than the above Bardeen-Brattain surface fieldeffect transistor [13]. (See also Bardeen's Nobel lecture [7].) It consists of two closely-spaced point-contact electrodes made of phosphorus bronze wires or metal stripes from an evaporated gold film. These electrodes contact a p-type surface inversion layer on an n-type germanium, through a thin oxide film.

bNYC = New York City; GER = Germany; BTL = Bell Telephone Laboratories; GE = General Electrical Research and Development Laboratory; STC = Shockley Transistor Corp.; SSL = Shockley Semiconductor Laboratory; FSC = Fairchild Semiconductor Lab.; MIT = M.I.T. Radiation Lab.; USSR = Could be a support of the s Soviet Union; GB = England.

Earlier (around November 17, 1947), Brattain was also doing other surface state and conductivity modulation experiments with Bardeen using the two point contacts on an n-type Ge [6]. These experiments led to the invention and experimental proof of the bipolar junction transistor in the following three events: i) minority carrier injection and junction transistor structure proposed by Shockley on January 23, 1948 [6], [8]; ii) experimental demonstration of the bipolar transistor by Shive on February 18, 1948 [21], [6] using a double-surface Ge point-contact transistor which had the emitter and collector contacts on the opposite surfaces of a thin n-Ge slice to eliminate the surface inversion path of the hole current; and iii) Bardeen and Brattain's explanation of the bipolar point-contact transistor action in the patent they filed on June 17, 1948 [13], [19], [20].

The key features of the bipolar transistor invention were: i) exponential dependence of the injected minority carrier current upon emitter junction voltage, and ii) the high impedance of the collector junction [6].

# B. Surface Inversion Layer and Channel

Modulation of the conductance of a surface inversion layer was suggested by Bardeen in his first transistor patent [7]. He stated that the modulation of the surface conductance can be obtained by reverse biasing either an insulated or a Schottky barrier gate over the surface of the surface inversion layer. In fact, Bardeen-Brattain's experiments [7] on the point-contact transistor [13] also gave the first working junction-gate field-effect transistor based on the modulation of the conductance of a surface inversion channel. As pointed out by Bardeen and Brattain in their 1948 analysis of the current-voltage characteristics of the point-contact transistor [19], [20], there are two 'minority' carrier (hole) current components in the emitter and collect leads of their point-contact transistor through two paths: i) the hole current flowing along the p-type surface inversion channel to the collector which is really a majority carrier current, and ii) the current from holes injected into the n-type Ge base (and hence a minority carrier current) by the forward biased p-n junction under the emitter point contact and these holes transverse laterally through the n-type base between the two point contacts and reach the collector. They stated that in their first experiments the majority carrier (hole) current in the p-type surface channel on the n-type Ge, i), probably dominated the current-voltage characteristics of the pointcontact transistor, and not the minority carrier injection current along the longer path through the base, ii). The cross-sectional view of a surface channel junction-gate fieldeffect transistor appeared in Figures 10 and 11 of the Bardeen-Brattain 1948 point-contact transistor patent [13] and these two figures also gave the biasing circuits as an amplifier with power gain using the base as the input.

# C. Surface States (Interface States) Fundamentals

A fundamental concept of surface states was introduced by Bardeen in 1947 [17] to explain the lack of metal-workfunction-dependence of the metal/semiconductor or Schottky barrier diode as well as the lack of conductivity modulation of the field-effect experiments performed by Pearson and Shockley at BTL [17], [18]. In a later experimental paper by Brattain and Bardeen on germanium surfaces [23] they and Shockley introduced three important fundamental concepts of surface states which have been the foundation of all subsequent research on the surface properties of semiconductors and surface effects on transistor characteristics. These are: i) the surface recombination velocity; ii) a two-surface-state model having a donor level near the conduction band and an acceptor level near the valence band; and iii) the equivalent circuit model of resistors to represent the surface recombination losses at these surface states.

It is now known that the two-level surface state model, ii), corresponds to **extrinsic** traps due to impurities at the semiconductor surface. For the **intrinsic** traps due to the dangling bonds on the host atoms (Ge in the Brattain and Bardeen experiment) the sign of the charge of the two levels is just the opposite to that of the impurity surface states: the positively charged or neutral donor level is near the valence band edge and the negatively charged or neutral acceptor level is near the conduction band edge.

The third concept, iii), was extended by Shockley in 1958 who developed a comprehensive equilibrium equivalent circuit model for electron-hole recombination and generation at bulk and surface traps which included also the diffusion and drift currents [24]. Shockley's extension and influence-at-a-distance led me to complete the circuit model development to include the arbitrary nonequilibrium situation in 1961 [25]–[27]. The equivalent circuit model has not only provided a most familiar tool to teach the physics of electrons and holes in transistors to undergraduate electrical engineering students who thrive on circuits but has also given a systematic means to solve the Shockley semiconductor equations numerically to obtain accurate solutions of the highly nonlinear characteristics of the transistor [28].

# D. Surface State (Interface State) Terminology

The terminology used in semiconductor surface research has been confusing probably because surface effects on transistor characteristics are complex, irreproducible, and unstable. Thus, the catch-all term 'surface states' has been used for many years to denote all the traps on and near the surface of a semicondutor covered by a fabricated (thermally grown or deposited) insulator or native oxide. A recent survey made by Bruce E. Deal led to a consensus on the notation and nomenclature to replace the catch-all term, surface states. It is now accepted and adhered to by most transistor researchers and integrated circuit engineers to call the surface states "interface traps" in transistor device and integrated circuit work. The term, interface traps, is most appropriate since no practical surfaces are bare. They are interfaces resulting from the coverage of the surface by a layer of native or fabricated oxide or other materials, such as an evaporated metal layer or an epitaxially grown semiconductor layer. The term "trap," as used by Bardeen, Brattain, and Shockley, is also the most appropriate to indicate that the electronic states under consideration are electronic bound states whose bound electron wave functions are localized in all three space dimensions at these trapping centers. Modifications, extensions, and concise definitions of these surface state phenomena occuring at today's oxidized VLSI silicon surface have been given by this author in a recent British IEE data review handbook, Properties of Silicon [29]. For example, the Deal committee also introduced the term 'oxide fixed charge' as the second component of the old 'surface states' observed on oxidized silicon. This term has been discarded and replaced by 'oxide traps' and 'oxide charges' without the word 'fixed' since it has been well known that charges in the oxide are not fixed but can change by diffusion, drift, capture or emission of an electron or a hole, and by creation via bond breaking or destruction via recombination with hydrogen or with adjacent dangling bonds. In fact, the change of the density of charges trapped on the oxide traps is the very cause that degrades the performance and reduces the operating life of the transistors and hence the integrated circuit chip.

#### E. Shockley's Minority Carrier Injection and Field-Effect Transistors in the Bulk of a Semiconductor

Surface states, or the interface and oxide traps, in the point contact experiments and the unsuccessful conductivity modulation experiments hindered the reproducibility. Shockley invented the bipolar junction transistor (BJT) theory in 1949 which depends solely on minority carrier injection [22] and the junction-gate field-effect transistor (JGFET) and published the theory in 1952 [30]. Both of these transistors in Shockley's device structures have their electrically active regions away from the surface in the bulk of the semiconductor. Surface effects should not be important, which has largely been realized in modern silicon transistors. Residual deleterious surface effects still require careful transistor design and clean fabrication processing in today's VLSI circuit chips to minimize and eliminate surface related electrical instabilities. The two basic surface phenomena first described by Bardeen, Brattain, and Shockley during 1947 to 1951-the surface inversion channel and surface recombination-are the basic causes of degradation of the transistor characteristics. The temporal changes of the oxide charge density will change the size of the surface channel because it is induced or modulated by the oxide charge. The temporal changes of the oxide charge density will also change the rate of recombination of electrons and holes in the surface states because of the change of the induced electron and hole densities at the interface by the oxide charge. These temporal changes give rise to electrical instabilities and aging of the transistor characteristics and cause integrated circuits to fail.

The key concept for the bipolar junction transistor is minority carrier injection over a potential barrier, such as the potential barrier of the p-n junction or the surface inversion layer which gives the exponential dependence of the injected minority carrier current upon the emitter junction voltage. The second key feature is the high impedance of the collector junction. The mathematical theory was first developed by Shockley on April 24, 1947 for the reverse biased p-n junction [6]. It was then extended to forward bias when he developed the p-n junction transistor theory [22] on January 23, 1948 [6]. Experimental proof of minority carrier injection was first given by Shive's double-surface transistor [21]. Detailed studies of minority carrier injection were carried out by Haynes, Ryder, and Shockley [6] during 1948.

## F. Tracing the Origin of the Modern Surface-Inversion Insulated-Gate Field-Effect Transistors

The n-type surface inversion layer on p-type Si and the p-type surface inversion layer on an n-type Ge were the

principal reason for the successful operation of the fieldeffect point contact transistors invented by Bardeen and Brattain in 1947 [7]. The strong influence of the surface inversion channel on the bipolar transistor current-voltage characteristics was also noted by Bardeen and Brattain in 1947 [13]. This influence was further demonstrated by Walter L. Brown [31] in 1953 who gave experimental proofs of conduction in an n-type surface inversion channel across the surface of the p-type base layer of a Ge n-p-n bipolar transistor. Brown's conclusion is unequivocal in spite of the highly unstable surface conditions in his experiments. The instability was because there was no gate electrode and the surface channel was induced by surface charge from the ambient gas. Ian M. Ross was the first to describe the modern p-n junction or enhancement MOSFET structure in a 1957 patent disclosure using Brown's observations [32]. Instead of depending on the ambient to control the surface channel conductance as in Brown's experiment, Ross placed a ferroelectric crystal over the surface of the p-type base layer of the n-p-n transistor and covered the ferroelectric with a silver paste as the gate electrode. He then applied a voltage to the silver gate to control the polarization of the ferroelectric and the conductance of the n-type surface channel over the p-type base. The n-type channel over the p-type base extends from the n-type emitter to the n-type collector. Ross's intention was to use the ferroelectric polarization as a memory mechanism. But his transistor structure is precisely also the modern inversion-channel MOSFET, that is, it has the mandatory ingredient: two rectifying junctions one at each of the two ends of the surface inversion channel, which is also a structure given by Heil in 1935 [5] without knowing the surface inversion principle. The modern version of the MOSFET uses a thermally grown oxide film in place of a ferroelectric film for the gate insulator.

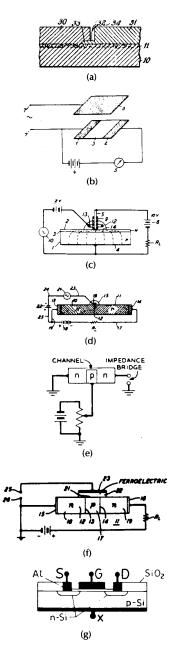

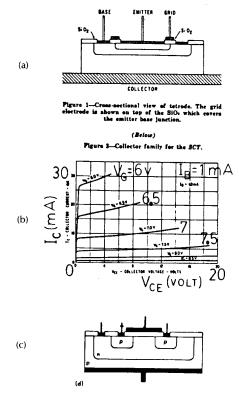

The evolution of the inversion channel MOSFET is illustrated in Fig. 4 using figures taken from the various patents and articles just cited. Fig. 4(a) is the one-rectifying-junction (sourceless or drainless) MOSFET proposed in Lilienfeld's second patent in 1928 [2]. Fig. 4(b) is the two-rectifying-junction surface inversion MOSFET described in Heil's 1935 patent [6]. Fig. 4(c) is Bardeen's single-rectifying-junction electrolyte-insulated-gate FET which gave the first recorded power gain in a solid-sate amplifier [6], [7]. Fig. 4(d) is Shockley's p-n junction diode with an insulated gate and it is the inversion channel MOSFET without the source (or drain) junction. Fig. 4 (e) is Brown's two junctions structure without a gate, used in his surface channel experiments [31]. Fig. 4(f) is Ross's inversion channel MOSFET using a ferroelectric gate insulator as memory site [32]. Fig. 4(g) is the modern inversion-channel MOSFET. It is evident that the chronological sequence depicted in this figure illustrates that new ideas and innovations can evolve directly or indirectly from previous knowledge. I was told that the transistor inventions at Bell Labs during 1947 and 1948 were not influenced by the patents of Lilienfeld and Heil. (See also Shockley's 1976 review [6] and Bardeen's Nobel lecture text and 1987 review [7].)

## G. Transistor Technology

There were a number of laboratory demonstrations of new methods of transistor fabrication during 1950 to 1956. They contributed directly or indirectly but all very signif-

Fig. 4. An evolutionary chronology of the inversion-channel MOSFET. (a) Fig. 4 of Lilienfeld's second (1928) patent [2] showing a gated metal/p-Cu<sub>2</sub>S junction. (b) Fig. 4 of Heil's 1935 patent [5] showing the inversion n-channel MOSFET which has the two mandatory rectifying junctions between the p-type semiconductor film (3) and the metal source and drain (1 and 2). (c) Fig. 3 of the first modern transistor patent (Bardeen's 1948 [7]) showing an insulated gate modulating an n-type surface layer in series with a reverse-biased bulk n-p junction. It is a sourceless MOSFET. (d) Fig. 1 of Shockley's 1948 transistor patent [8] showing a gated p-n junction which is a sourceless modern inversion-channel MOSFET. (e) Fig. 2(c) of Walter Brown's 1953 surface inversion channel experiment [31]. (f) Fig. 1 of lan Ross's 1955 ferroelectric MOSFET [32] showing the **two mandatory rectifying junctions**. This must be credited as the first written disclosure of the modern surface-inversion-channel MOSFET. (g) The cross-sectional view of a modern Si surface-inversion-channel n-channel MOSFET.

icantly to the eventual successes in the realization of the silicon MOS transistor and integrated circuits. They are also listed in Table 1 and briefly discussed next.

The first BJT was built by Teal, Spark, and Buehlor in 1951 [33] from alternatively doping the germanium melt with n-type and p-type dopant impurities during the growth of a germanium single crystal using the single-crystal growth technique developed by Teal and Little [15]. The first JGFET in the semiconductor bulk was built by Dacey and Ross in 1953 [34]. Solid state diffusion to improve diode characteristics was suggested by Bethe in 1942 [14] and reported by Serin and Stephens in 1946 [14] in order to improve the uniformity of silicon crystal rectifiers for radar and microwave detectors. A very thin diffused Ge p-n junction layer was introduced by Hall and Dunlap in 1950 [35] using impurities from an alloy source. The gaseous diffusion technology used in the production of silicon integrated circuit today was invented by Scaff and Theuerer in 1951 [36] and further developed by Fuller and Ditzenberger in 1954 [37] which led to the fabrication of the first high frequency diffused bipolar junction transistors by Tannenbaum and Thomas in 1956 [38] and also the Ge p-n-p transistor by C. A. Lee et al. The technique of using an oxide mask against impurity penetration during impurity diffusion into the silicon wafer was introduced by Frosch and Derrick in 1957 [39], [40]. The first quantitative kinetic and process modeling of the oxide masking technique of Frosch and Derrick was given by Sah, Sello, and Tremere in 1958 [41] for oxide masking against phosphorus donor impurity diffusing into silicon. The masking data (oxide thickness required to mask or prevent phosphorous from penetrating into the silicon surface versus the temperature and time of exposure to the phosphorus vapor) obtained by Sah, Sello, and Tremere was used by Hoerni to produce the oxide stabilized planar silicon transistor (personal communication from Jean Hoerni, 1959) and these data and their extensions are used in today's VLSI production.

Other transistor fabrication technologies introduced or proposed during this period included the principle of zone refining (float-zone had been used to give high purity silicon) of semiconductor single crystal developed by Theuerer and Pfann in 1952 [42]–[46], the ion implantation technique proposed by Shockley in 1954 [47], [48], the first epitaxial transistor demonstrated by Theurerer, Kleimack, Loar, and Christenson in 1959 [49] which was directed by Ross [50], and simultaneous epitaxial Ge transistor work by Tannenbaum et al. These technologies took another decade to develop into effective production processes.

## H. Transistor Material and Device Physics

Research on the effects of electronic traps or recombination centers on diode and transistor characteristics began during the 1950s. Electronic traps arise from atomic imperfections in the crystalline lattice of the semiconductor. Electrons and holes can recombine and be generated at high rates at the electronic traps. The studies have been based on the electron-hole recombination rate theory developed by Shockley and Read [51] and Hall [52] in 1952, known today as the Shockley-Read-Hall (SRH) or Hall-Shockley-Read (HSR) recombination statistics. ('Recombination kinetics' is the correct term.) Generation of electrons and holes by thermally exciting them out of the electronic traps in the

space charge layer of a p-n junction in the bulk of a semiconductor was shown to be an important mechanism of the reverse leakage current in silicon diodes by Kleinknecht and Seiler in 1954 [53] and in germanium by Pell and Roe in 1955 [54]. Recombination of electrons and holes in these traps in a forward biased silicon junction space charge layer was shown by Sah, Noyce, and Shockley [55] to control the silicon bipolar transistor gain at low currents and the switching voltage and holding current of the silicon p-n-p-n four-layer diodes and silicon controlled rectifiers. The generation-recombination current gradually discharges the stored charge on the capacitance and is the reason that the MOSFET dynamic random access memory (DRAM) cell has to be refreshed every millisecond.

Another transistor related basic concept of singular importance today is the theory of hot electrons advanced by Shockley in 1951 [56], [57]. It predicts the observed reduction of electron mobility at increasing electric field and the observed saturation of the electron drift velocity to about 10<sup>7</sup> cm/s at very high electric field. These effects are due to electron energy loss during collision with the vibrating silicon atoms resulting in the generation of optical phonons or silicon vibrations at infrared frequencies. These hot electron effects pose a fundamental limit on the speed of today's silicon as well as GaAs field-effect transistors. All the fundamental ideas and zeroth order theory of the hot electron effects are contained in this Shockley paper [56] but they have only been gradually rediscovered by the current generation of semiconductor researchers and engineers who are investigating transistor reliability and oxide failure in high electric fields such as the maximum dielectric breakdown field of the gate oxide of MOSFET which limits its ultimate performance. This will be discussed later.

## I. Birth and Growth of the Silicon Valley

Toward the end of this first phase (1957), accelerated development and manufacturing of silicon transistors and integrated circuits began in the Silicon Valley which has grown to cover an area of about fifty miles in length extending from San Francisco south to Stanford and then to San Jose, now heavily populated by electronics and biotechnology related companies. The predecessor of the Silicon Valley was started by F. E. Terman, engineering dean at Stanford, when his students, Hewlett, Packard, and the Varian brothers formed the companies bearing their names around World War II. The rapid growth of the Silicon Valley began when Shockley left Bell Laboratories to start his own silicon transistor manufacturing company in 1955 and obtained the financial backing of fellow Caltech alumnus, Arnold Beckman. Shockley Semiconductor Laboratory began operation in the fall of 1955 as a division of the Beckman Instruments, Inc. in an army barracks (some people call it army hut) at 391 South San Antonio Road in Palo Alto. Twelve technical persons were personally interviewed and hired by Shockley: Horseley, Noyce, Moore, Grinich, Roberts, Hoerni, Last, Jones, Kleiner, Blank, Knapic, and Sah. It was incorporated in 1957 as the Shockley Transistor Corporation.

Eight of these, Noyce, Moore, Grinich, Roberts, Hoerni, Last, Kleiner, and Blank were then recruited by Fairchild Camera and Instruments Corp. to start the Fairchild Semiconductor Corporation with \$2M when negotiation of the eight with A. O. Beckman to set up a separate \$1M silicon

transistor production facility faltered. The Fairchild laboratory and production line began operation at 844 Charleston Road in Palo Alto, about ten blocks east of the Shockley Laboratory, with the focused mission to mass-produce high performance silicon (bipolar) transistors. Among the many alternatives considered in a detailed 1957 plan of Noyce, the double diffused Si n-p-n mesa transistor was selected as the first product. It required only two photoresist steps to define the emitter and metal contacts.

Most of the early integrated circuit companies in the Silicon Valley were started or jointly started by Fairchild engineers, including four of the original eight, Noyce, Moore, Last, and Hoerni. One can say Shockley seeded the Silicon Valley and Fairchild was the first born that started its growth into the multi-billion dollar integrated circuit farm of today. A genealogy map has been prepared by the Semiconductor Equipment and Materials Institute in Mountain View, CA, and the first companies started by the Shockley line are listed in the map as follows. Last and Hoerni started Amelco in 1961, which was later renamed Teledyne Semiconductor. Hoerni went on to start Union Carbide Electronics in 1964, Intersil in 1967, and then moved to Europe to start several companies. Noyce and Moore started Intel in 1968. Other earlier and later Fairchild employees, who were not the original eight from Shockley Semiconductor, started more than twelve companies. These have since multiplied into slightly more than 100 companies by 1983, averaging about four startups per year during the twenty-five years since 1957 when Fairchild was founded. The entrepreneurship continues and fuels more startups. Most of the startups are not large companies, which reflects the opportunities created by the very many niche markets in integrated circuit applications based on the unique ideas of the founders of the startups. Most of the recent startups use silicon processing foundries to produce specialty integrated circuit chips. They have no in-house silicon wafer processing facility due to the very high cost of the processing equipment. The large number of so many new startups in the Silicon Valley also reflects the proximity of Stanford and (University of California at) Berkeley and their faculty's active involvement.

# IV. TECHNOLOGY DEVELOPMENT AND DEVICE INNOVATIONS (1958–1968)

Development of new silicon transistor fabrication technologies and invention of new transistor and circuit structures are highlights of the MOSFET evolution during the second phase which spans the decade from 1958 to 1968. These advances are tabulated in Table 2. It began when successful efforts to stabilize the surface of silicon p-n junction rectifiers and transistors were reported.

Stabilization of the MOSFET was the principle concern of researchers during 1958 to 1962. Headlines were made by a Berkeley professor during the 1961 **WESCON** (IRE-IEEE Western Convention and Show in August) and quoted by a San Francisco Chronical reporter who insisted that the MOSFET will never be practical due to electrical instabilities caused by surface states (interface and oxide traps). The bipolar junction transistor was predicted to continue to dominate. However, intensive research on stabilizing the surface of silicon rectifiers and transistors was going on at several laboratories, including Bell Telephone, IBM, and

Table 2 Basic Technology and Transistor Innovation Phase of MOSFET Evolution (1958–1968)

| Disclo |                   |                                |                           | Device                                   |              |                   |

|--------|-------------------|--------------------------------|---------------------------|------------------------------------------|--------------|-------------------|

| Date   |                   | Authors-Inventors              | Institutions              | and/or                                   | Reduction to |                   |

| Subm.  | Pub.              | Development Team               | or Locations <sup>b</sup> | Technology                               | Practice     | Ref. <sup>c</sup> |

| 1958   | 1959              | Atalla, Tannenbaum, Scheibner  | BTL                       | Oxide Surface Passivation                | Lab          | [58]              |

| 1958   | 1959              | Sah, Sello, Tremere            | STC-FSC                   | Oxide Diffusion Mask, PSG                | Lab          | [41]              |

| 1959   | 1959              | Moll                           | SEL                       | MOS Capacitor (MOSC Coined)              | Lab          | [59]              |

| 1960   | 1 <del>9</del> 60 | Hoerni                         | FSC                       | Si Planner BIT                           | Prod         | [63]              |

| 1960   | 1960              | Noyce                          | FSC                       | Si Monolithic IC                         | Prod         | [65]              |

| 1960   | 1960              | Kahng, Atalla                  | BTL                       | Si MOSFET                                | Lab          | [70]              |

|        | 1960              | Ross, Team                     | BTL                       | Si Epitaxial Transistor                  | Lab          | [49], [50]        |

| 1960   | 1961              | Terman, Moll                   | SEL                       | MOS CV Technique                         | Lab          | [60]              |

| 1961   | 1961              | Sah                            | FSC                       | BIMOS                                    | Lab          | [79], [80]        |

| 1961   | 1961              | Sah                            | FSC                       | Floating Gate Charge Storage             | Lab          | [85]              |

| 1961   | 1962              | Sah                            | FSC                       | Surface Channel and Recombination        | Lab          | [81]              |

| 1962   | 1963              | Wanlass, Sah, Moore            | FSC                       | CMOS                                     | Lab          | [90], [92]        |

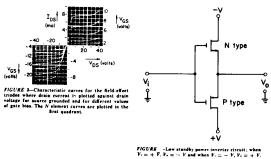

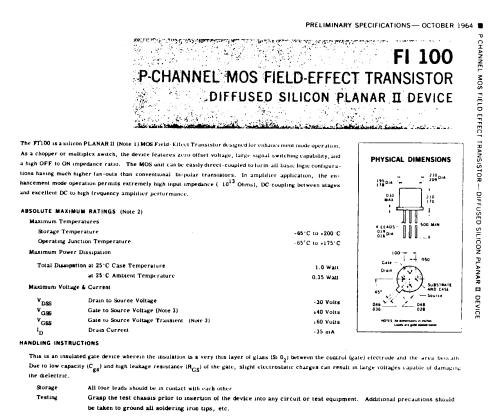

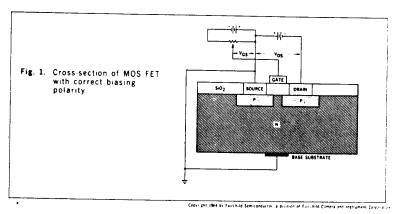

|        | 1962              | Engineering                    | FSC                       | FI-100 PMOS (MOSFET Coined)              | Prod         | FIG8              |

|        | 1962              | Engineering                    | RCA                       | 3N98 NMOS (Depletion Mode)               | Prod         | FIG9              |

|        | 1962              | Engineering                    | FSC                       | 5-Micron Channel                         | Lab          | [PR]              |

| 1962   | 1963              | Deal, Grove, Snow, Wanlass     | FSC                       | Expanding MOS Research                   | 240          | [PR]              |

|        | 1964              | Young, Seraphim, Team          | IBM                       | Expanding MOS Research                   |              | [88]              |

| 1964   | 1964              | Kerr, Young                    | IBM                       | PSG Stabilization                        | Lab          | [100]             |

| 1964   | 1965              | Snow, Deal, Grove, Sah         | FSC                       | Sodium Ion Drift Reduced                 | Lab          | [99]              |

| 1963   | 1966              | Heiman                         | RCA                       | Body Effect                              | Lab          | [117]             |

|        | 1965              | Balk                           | IBM                       | H <sub>2</sub> Anneal of Interface Traps | Lab          | [103], [10        |

|        | 1965              | Kooi                           | Philips                   | H <sub>2</sub> Anneal of Interface Traps | Lab          | [105], [10        |

|        | 1965              | Balk, Burkhardt, Gregor        | IBM                       | Oxide Charge 100 < 100 < 111             | Lab          | [106]             |

|        | 1965              | Delord, Hoffman, Stringer      | Reed                      | Oxide Charge 100 < 111                   | Lab          | [107]             |

|        | 1965              | Miura                          | NEC                       | Oxide Charge 100 < 110 < 211 < 111       | Lab          | [108]             |

|        | 1965              | Snow, Deal                     | FSC                       | PSG Polarization                         | Lab          | [102]             |

|        | 1966              | Mead                           | Caltech                   | MESFET Demonstrated                      | Lab          | [98]              |

| 1964   | 1967              | Miller, Barson                 | IBM                       | PSG Bulk Impurity Getter                 | Lab          | [140]             |

| 1967   | 1967              | Kahng                          | BTL                       | Floating Gate MOSFETs                    | Lab          | [121]             |

| 967    | 1967              | Kahng, Sze                     | BTL                       | Floating Gate Demonstrated               | Lab          | [120]             |

| 963    | 1967              | Kerwin, Klein, Sarace          | BTL                       | Poly Si Gate Self-Align                  | Lab          | [111]             |

|        | 1968              | Sarace, Kerwin, Klein, Edwards | BTL                       | Silicon Nitride Oxide Mask               | Lab          | [112]             |

|        | 1968              | Bower, Dill                    | Hughs                     | Ion-Implant Self-Align                   | Lab          | [113]             |

| 967    | 1968              | Dennard                        | IBM                       | One-Transistor DRAM Cell                 | Lab          | [118]             |

|        | 1969              | Chou, Eldridge                 | IBM                       | PSG Without Polarization                 | Lab          | [140], [14        |

|        | 1969              | Hatzakis                       | IBM                       | Liftoff Metallization                    | Lab          | [140], [14        |

|        | 1968              | Noyce, Moore                   | INTEL                     | Intel Corp. Founded                      | Lut          | [140], [14        |

<sup>a</sup>Subm. = Submission date. Pub. = Publication date.

<sup>c</sup>[PR] = Personal recollection or record.

Fairchild Semiconductor Laboratories. These projects were aimed at discovering the causes of the electrical instabilities and inventing practical ways to stabilize the silicon surface. The effort was motivated not only by the fabrication simplicity of MOSFETs that could result in volume production of inexpensive complex MOS integrated circuits with low power dissipation, but also by the need to stabilize the electrical characteristics of silicon bipolar transistors for operation at low currents or high voltages where performance deterioration (current gain and leakage current) due to surface instabilities had been severe.

# A. Surface Stabilization by Thermally Grown Oxide Film on Silicon

The first successful attempt to stabilize the silicon surface was reported by a group led by Atalla (Atalla, Tannenbaum, Scheibner) at Bell Telephone Laboratories during 1958 [58], while early attempts were made by Frosch also at Bell Telephone Laboratories around 1954 (private communication from J. Bardeen, Oct. 1, 1988). On the surface where the silicon p-n junction intercepts, they grew a thin layer of sil-

icon dioxide of 150 to 300 A in dry oxygen at 920°C for 10 to 30 minutes. They reported a ten to one hundred times reduction of the reverse leakage current of silicon n+-p diode rectifiers and a stabilization of leakage current in pn-p-n diode switches. Low frequency 1/f noise, due to random trapping of electrons and holes at the interface traps, was also reduced tremendously in the oxide passivated diode rectifiers as indicated by a reduction of the noise corner frequency from 10 000 Hz to less than 10 Hz. Those of us active in silicon material and device research during 1956-1960 considered this successful effort by the Bell Labs group led by Atalla to stabilize the silicon surface the most important and significant technology advance, which blazed the trail that led to silicon integrated circuit technology developments in the second phase and volume production in the third phase.

# B. Origin of the Acronym MOS

The acronym MOS (Metal-Oxide-Semiconductor or Metal-Oxide-Silicon) was coined by John Moll in 1959 [59] who moved to Stanford from Bell Telephone Laboratories

<sup>&</sup>lt;sup>b</sup>BTL = Bell Telephone Labs. or Bell Labs. or AT&T Bell Labs.; SEL = Stanford Electronics Labs.; FSC = Fairchild Semiconductor Corporation; NEC = Nippon Electric Corp.; Reed = Reed College.

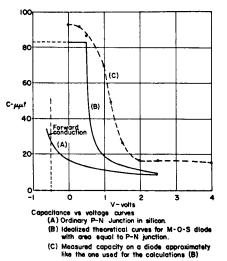

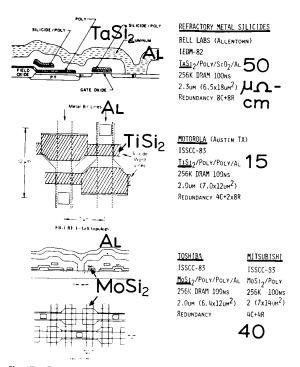

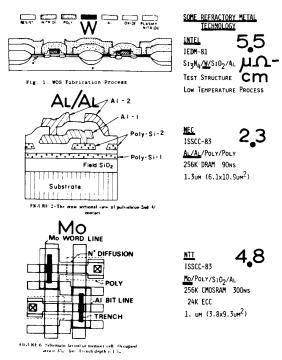

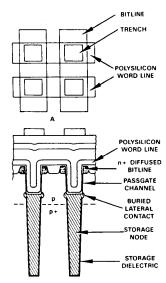

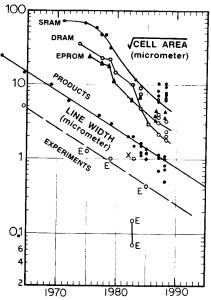

a year earlier. He gave a paper at WESCON on using the MOS capacitor (MOSC) as a voltage controlled variable capacitor. Fig. 5 shows Moll's experimental capacitance versus dc voltage (CV) curve (curve C) and his theoretical curve (curve B) based on a simple theory in which the electrons and holes are neglected in the surface space-charge layer, known as the carrier (or electron-hole) depletion theory.

# C. The MOS Capacitance Voltage Diagnostic Technique for Surface States

The use of the MOS capacitance-voltage (MOSCV) characteristics to monitor and measure the density of surface states (interface plus oxide traps) was suggested by Moll [59] and demonstrated by Lewis M. Terman [60] during 1959–1960 while doing his doctoral research under Moll at Stanford. Terman measured the frequency dependences of the MOSCV curves from 100 Hz to 5 MHz [60], similar to the experimental curve taken at one frequency given by Moll (see Fig. 5). He then extrapolated the experimental *CV* curves

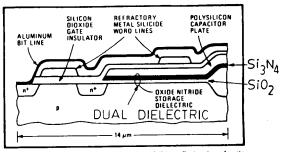

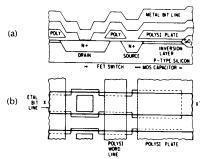

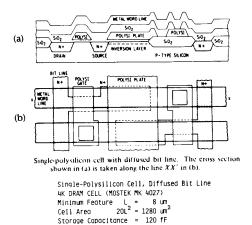

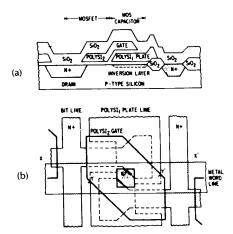

**Fig. 5.** The first experimental metal-oxide-silicon capacitance-voltage (dc) (MOSCV) characteristic given by John Moll and comparison with theory [59].