# Impact of Processing Technology on DRAM Sense Amplifier Design

by

#### Jeffrey Carl Gealow

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering and Computer Science at the Massachusetts Institute of Technology

June 1990

© Jeffrey Carl Gealow, 1990. All rights reserved.

The author hereby grants to M.I.T permission to reproduce and to distribute copies of this thesis document in whole or in part.

| Signature of Author   | Department of       | Electrical Engineering and | Computer Science<br>May 1990                               |

|-----------------------|---------------------|----------------------------|------------------------------------------------------------|

| Certified by <u> </u> | ociate Professor of | Electrical Engineering and | Charles G. Sodini<br>Computer Science<br>Thesis Supervisor |

| Certified by          |                     | Senior Technical Staff     | Howard L. Kalter, IBM Corporation                          |

| Accepted by           | Chairman            | Department Committee on    | Arthur C. Smith<br>Graduate Students                       |

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

AUG 10 1990

LIBRARIES

ADDITION

# Impact of Processing Technology on DRAM Sense Amplifier Design

by

#### Jeffrey Carl Gealow

Submitted to the

Department of Electrical Engineering and Computer Science

May 1990

In Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering and Computer Science

#### **Abstract**

Sense amplifier design is critical to DRAM performance. As DRAM chip capacity has increased, different sensing schemes have been employed. The purpose of this work is to explain impacts of processing technology on DRAM sense amplifier design and to identify design strategies suitable for 64M DRAM sense amplifiers. DRAM performance and processing technology evolution are reviewed. Sense amplifier operation is examined analytically. Sense amplifiers used in 4K and higher density DRAMs are studied. 64M DRAM processing technology features and performance specifications are projected. Finally, alternative design approaches for 64M DRAM sense amplifiers are compared and evaluated.

Thesis Supervisor: Charles G. Sodini

Title: Associate Professor of Electrical Engineering and Computer Science

Company Supervisor: Howard L. Kalter

Title: Senior Technical Staff, IBM Corporation

This material is based upon work supported in part under a National Science Foundation Graduate Fellowship.

#### Acknowledgements

I have completed three MIT VI-A Internship Program assignments at the IBM General Technology Division in Essex Junction, Vermont. This research was conducted during my third assignment. I am grateful to past and present members of Department A23 for their help. John Nickel served as my mentor during my first assignment, patiently teaching me CMOS circuit design. Jim Yankosky, John Barth, and John Nickel all provided invaluable computer assistance. Scott Lewis and John Fifield contributed very useful sense amplifier design insights. Chuck Drake graciously shared his computer with me. Outside of Department A23, Paul Smith supplied DRAM trend information and provided graphics software guidance.

I thank Howard Kalter, my manager and thesis supervisor at IBM, for making my assignments both interesting and educational, for sharing his technical wisdom, and for reviewing drafts of this thesis.

I am grateful to Charles Sodini for supervising this thesis.

I thank my fiancée, Mary Condello, for helping me manage my bibliography, for proofreading this thesis, for her support and encouragement, and for enduring several long bus rides in order to visit me in Vermont.

Finally, I thank my parents, Jon and Rita Gealow, for their love and support.

## Contents

| 1 | Intr | oducti                         | ion                                           |

|---|------|--------------------------------|-----------------------------------------------|

|   | 1.1  | $\operatorname{Divid}\epsilon$ | ed Bitline Architecture                       |

|   |      | 1.1.1                          | Signal Loss Due to Incomplete Charge Transfer |

|   |      | 1.1.2                          | Dummy Storage Cells                           |

|   | 1.2  | Noise                          | Sources                                       |

|   | 1.3  | Folded                         | Bitline Architecture                          |

|   | 1.4  | Balane                         | ced Flip-Flop Sense Amplifier                 |

|   | 1.5  | DRAN                           | M Evolution                                   |

| 2 | The  | eoretic                        | al Analysis of Sense Amplifier Operation      |

|   | 2.1  |                                | ing Pulse Optimization                        |

|   | 2.2  | Sensit                         | ivity                                         |

|   |      | 2.2.1                          | Sense Amplifier Circuit Mismatches            |

|   |      | 2.2.2                          | Published Sensitivity Analyses                |

|   |      | 2.2.3                          | Source-Coupled Pair Offset                    |

|   |      | 2.2.4                          | Design Impacts                                |

| 3 | Sen  | se Am                          | plifier Design Evolution                      |

| • | 3.1  |                                | RAM Generation                                |

|   | 0.12 | 3.1.1                          | Texas Instruments                             |

|   |      | 3.1.2                          | Microsystems International                    |

|   | 3.2  |                                | ORAM Generation                               |

|   | ٠.ــ | 3.2.1                          | Intel                                         |

|   |      | 3.2.2                          | Mostek                                        |

|   | 3.3  | =                              | ORAM Generation                               |

|   | 0.0  | 3.3.1                          | IBM                                           |

|   |      | 3.3.2                          | Texas Instruments                             |

|   |      | 3.3.3                          | Fairchild                                     |

|   | 3.4  |                                | DRAM Generation                               |

|   | 0.1  | 3.4.1                          | Hitachi                                       |

|   |      | 3.4.2                          | Intel                                         |

|   | 3.5  | -                              | RAM Generation                                |

|   | J.0  | 3.5.1                          | Toshiba                                       |

|   |      | 3.5.2                          | Texas Instruments                             |

|    | 3.6   | 4M DRAM Generation                                | 73  |

|----|-------|---------------------------------------------------|-----|

|    |       | 3.6.1 Toshiba                                     | 73  |

|    | 3.7   | 16M DRAM Generation                               | 75  |

|    |       | 3.7.1 Twisted Bitline Architecture                | 75  |

|    |       | 3.7.2 $V_T$ -Derived Bitline Precharge Potentials | 79  |

|    |       | 3.7.3 Sense Amplifier Pitch Doubling              | 82  |

| 4  | 64N   | I DRAM Technology and Performance Projections     | 83  |

| 5  | 64N   | I DRAM Sense Amplifier Design                     | 89  |

|    | 5.1   | Bitline Power Considerations                      | 90  |

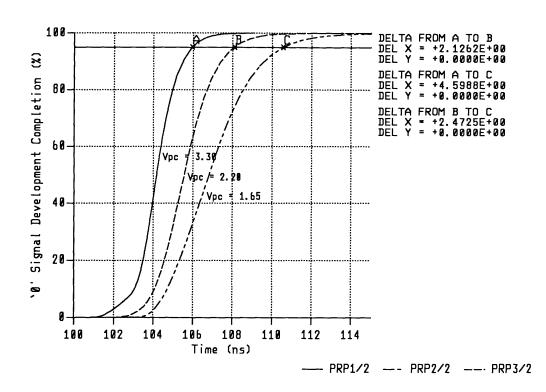

|    | 5.2   | Signal Development Considerations                 | 93  |

|    | 5.3   | Bitline Precharge Potential                       | 98  |

|    |       | 5.3.1 $V_{DD}$ Sense Amplifier                    | 98  |

|    |       | 5.3.2 $1/2 V_{DD}$ Sense Amplifier                | 102 |

|    |       | 5.3.3 $2/3 V_{DD}$ Sense Amplifier                | 105 |

|    |       | 5.3.4 Design Impacts                              | 109 |

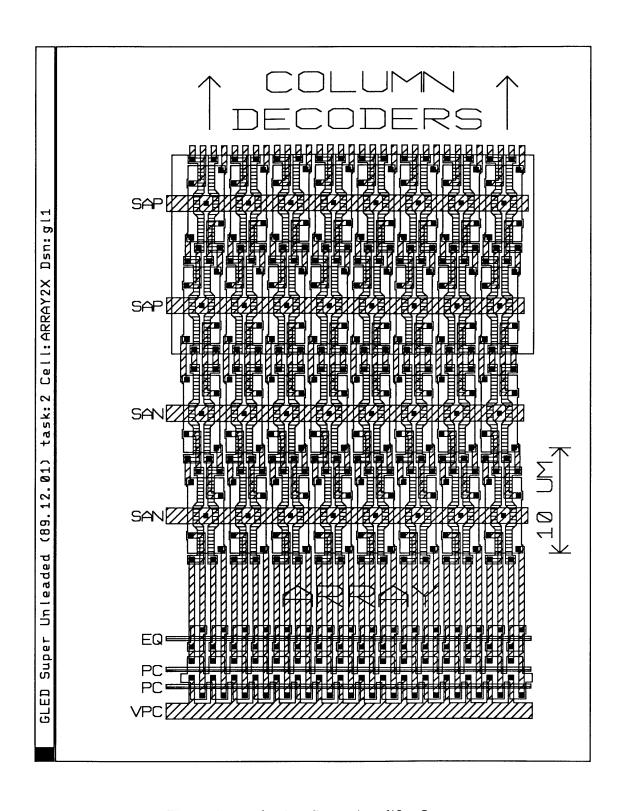

|    | 5.4   | Layout Considerations                             | 112 |

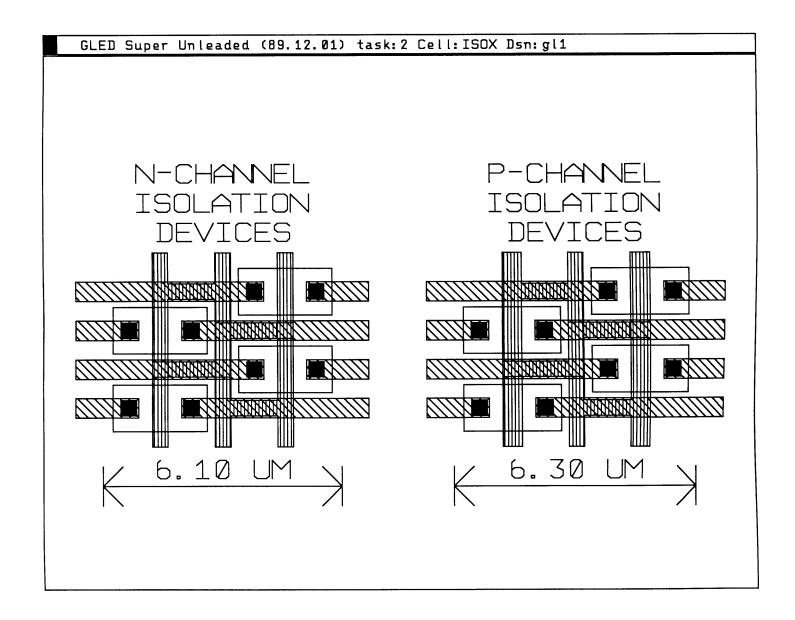

|    | 5.5   | Isolation Devices                                 | 113 |

|    | 5.6   | Sensitivity Analysis                              | 116 |

| 6  | Con   | clusion                                           | 125 |

|    | 6.1   | Major Accomplishments                             | 125 |

|    | 6.2   | Future Work                                       | 126 |

| Re | efere | nces                                              | 127 |

| A  | DR.   | AM Chip Data                                      | 149 |

|    | A.1   | 2K, 4K, and 8K DRAM Chip Data                     | 150 |

|    | A.2   | 16K DRAM Chip Data                                | 151 |

|    | A.3   | 64K DRAM Chip Data                                | 153 |

|    | A.4   | 256K DRAM Chip Data                               | 156 |

|    | A.5   | 1M DRAM Chip Data                                 | 159 |

|    | A.6   | 4M DRAM Chip Data                                 | 162 |

|    | A.7   | 16M DRAM Chip Data                                | 165 |

| В  | Sen   | se Amplifier Layouts                              | 167 |

## List of Figures

| 1.1  | DRAM Array                                                |

|------|-----------------------------------------------------------|

| 1.2  | Divided Bit Line Architecture                             |

| 1.3  | Required Tolerance versus Number of Occurrences           |

| 1.4  | Folded Bit Line Architecture                              |

| 1.5  | Stein et al. Balanced Flip-Flop Sense Amplifier           |

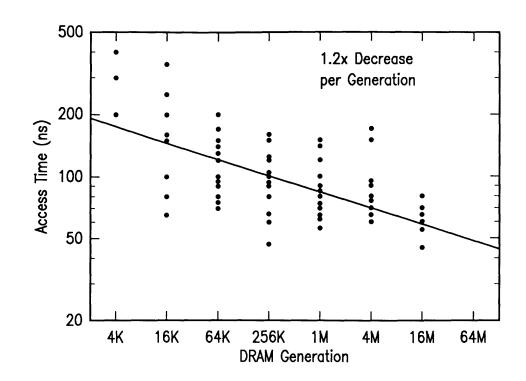

| 1.6  | Access Time versus DRAM Generation                        |

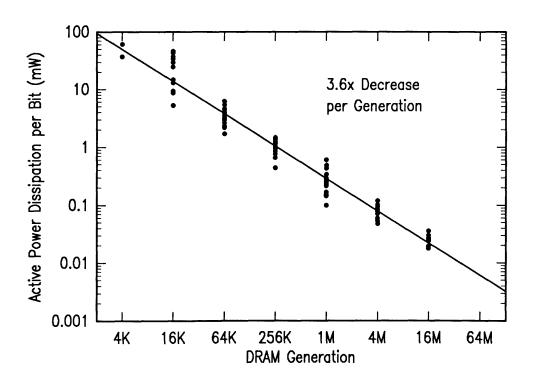

| 1.7  | Power per Bit versus DRAM Generation                      |

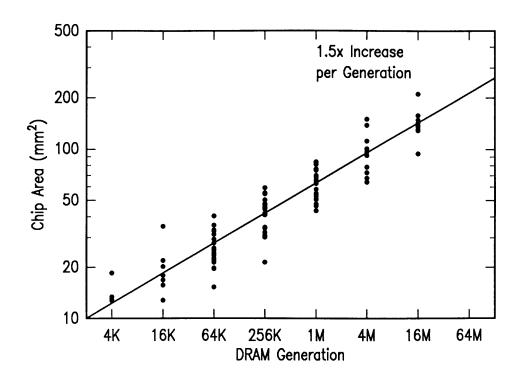

| 1.8  | Chip Area versus DRAM Generation                          |

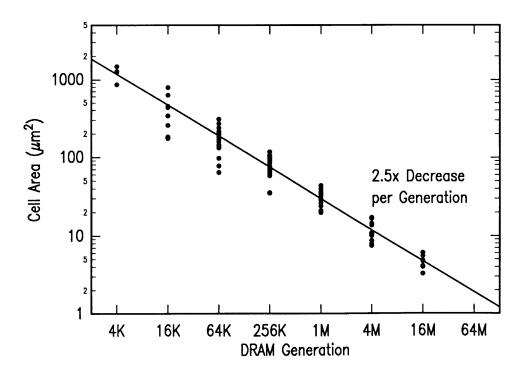

| 1.9  | Cell Area versus DRAM Generation                          |

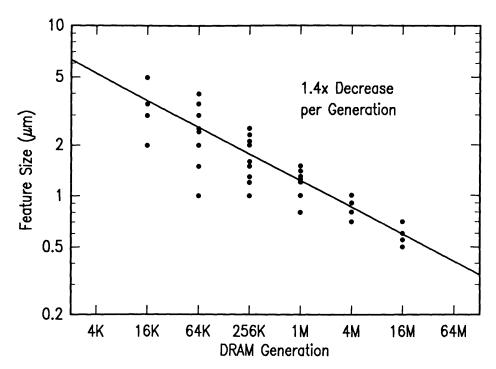

| 1.10 | Feature Sizes versus DRAM Generation                      |

| 0.1  | Cross-Coupled n-channel MOSFET Sense Amplifier Circuit 29 |

| 2.1  | Cross Coupled womanner 112001 21 Some Timp                |

| 2.2  | Optimal Latching Pulse Waveforms                          |

| 2.3  | Source-Coupled MOSFET Pair                                |

| 3.1  | TI 4K DRAM Sense Amplifier                                |

| 3.2  | Microsystems International 4K DRAM Sense Amplifier 49     |

| 3.3  | Intel 16K DRAM Sense Amplifier                            |

| 3.4  | Mostek 16K DRAM Sense Amplifier                           |

| 3.5  | IBM 64K DRAM Sense Amplifier                              |

| 3.6  | TI 64K DRAM Sense Amplifier                               |

| 3.7  | Fairchild 64K DRAM Sense Amplifier 62                     |

| 3.8  | Hitachi 256K DRAM Sense Amplifier                         |

| 3.9  | Intel 256K DRAM Sense Amplifier                           |

| 3.10 | Toshiba 1M DRAM Sense Amplifier                           |

| 3.11 | TI 1M DRAM Sense Amplifier                                |

| 3.12 |                                                           |

| 3.13 | Folded Bitline Model                                      |

| 3.14 | Twisted Bitline Model                                     |

|      | NTT 16M DRAM Sense Amplifier                              |

|      | $2/3 V_{DD}$ Sense Amplifier Circuit                      |

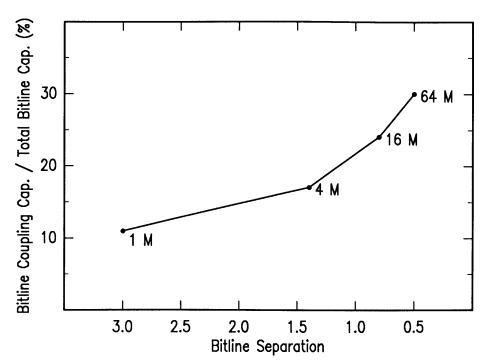

| 4.1  | Bitline Coupling Capacitance                              |

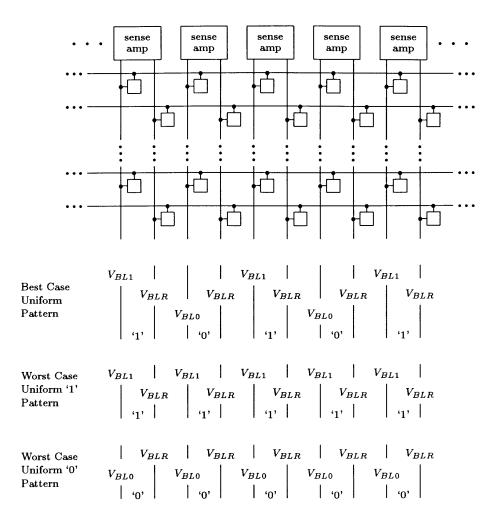

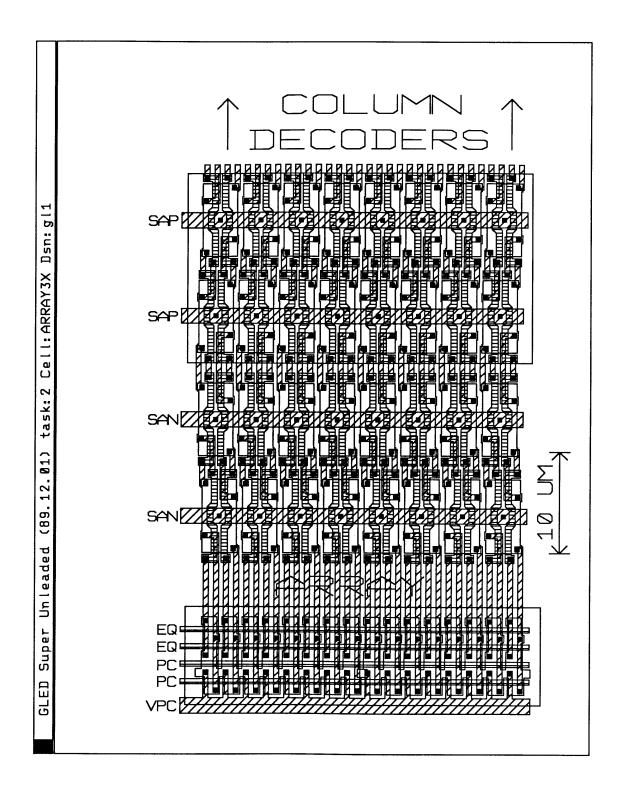

| 5.1  | Uniform Array Patterns                                                    | 91  |

|------|---------------------------------------------------------------------------|-----|

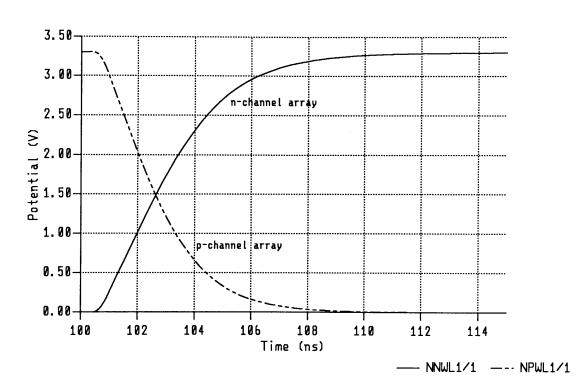

| 5.2  | Wordline Waveforms for Signal Development Analysis                        | 95  |

| 5.3  | p-channel Array Signal Development                                        | 96  |

| 5.4  | n-channel Array Signal Development                                        | 97  |

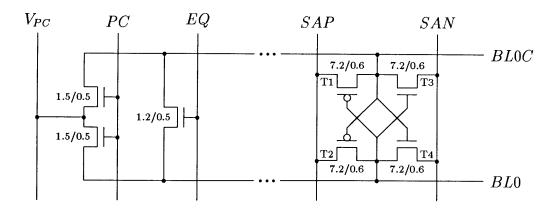

| 5.5  | $V_{DD}$ Sense Amplifier Circuit                                          | 99  |

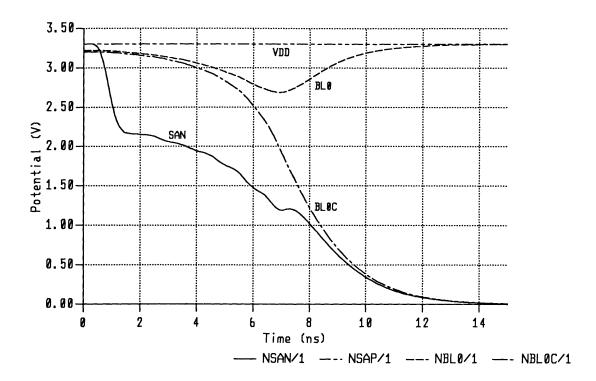

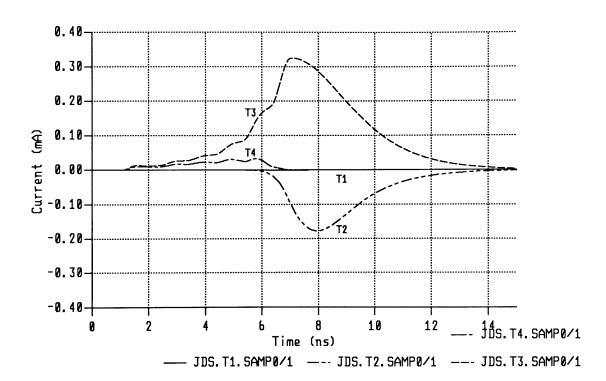

| 5.6  | $V_{DD}$ Sense Amplifier Waveforms                                        | 100 |

| 5.7  | $V_{DD}$ Sense Amplifier Device Currents                                  | 101 |

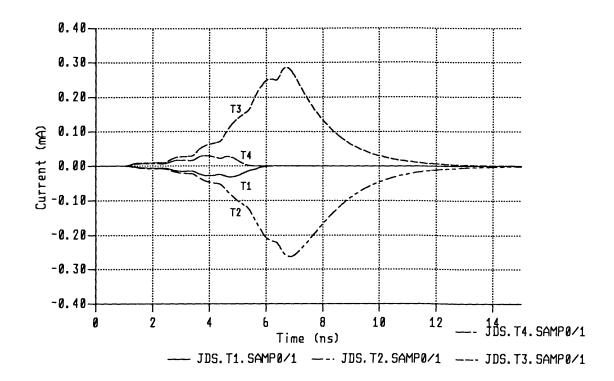

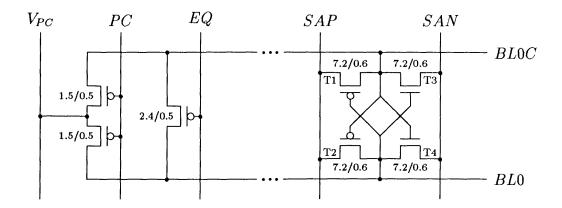

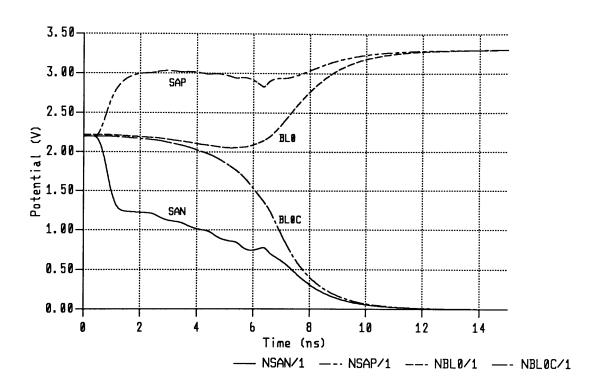

| 5.8  | $1/2 V_{DD}$ Sense Amplifier Circuit                                      | 102 |

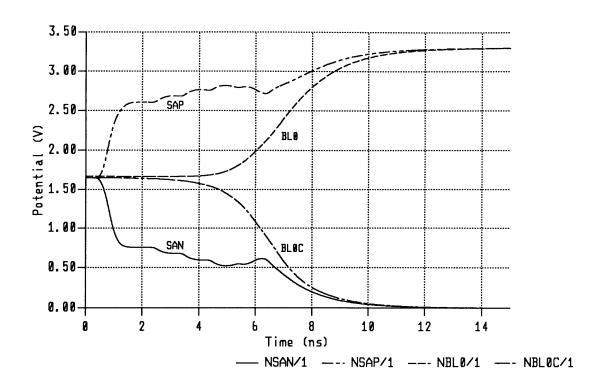

| 5.9  | $1/2 V_{DD}$ Sense Amplifier Waveforms                                    | 103 |

| 5.10 | $1/2 V_{DD}$ Sense Amplifier Device Currents                              | 104 |

| 5.11 | $2/3 V_{DD}$ Sense Amplifier Circuit                                      | 106 |

| 5.12 | $2/3 V_{DD}$ Sense Amplifier Waveforms                                    | 107 |

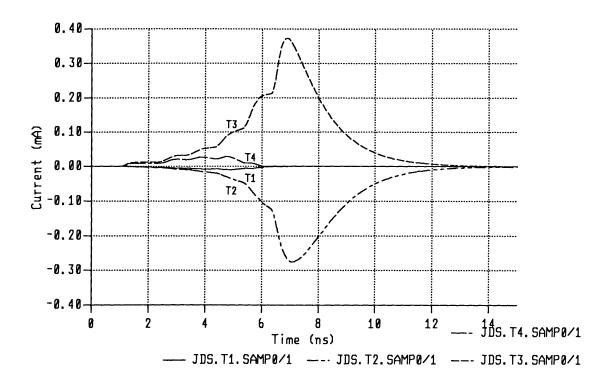

| 5.13 | $2/3 V_{DD}$ Sense Amplifier Device Currents                              | 108 |

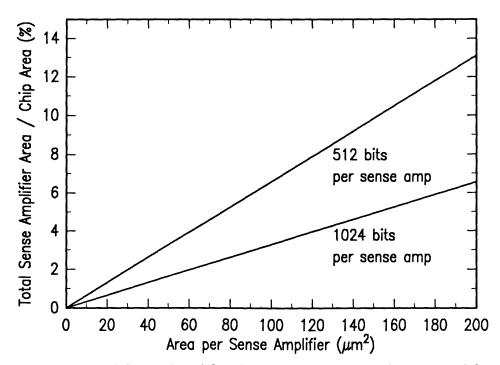

|      | Total Sense Amplifier Area versus Area per Sense Amplifier                | 112 |

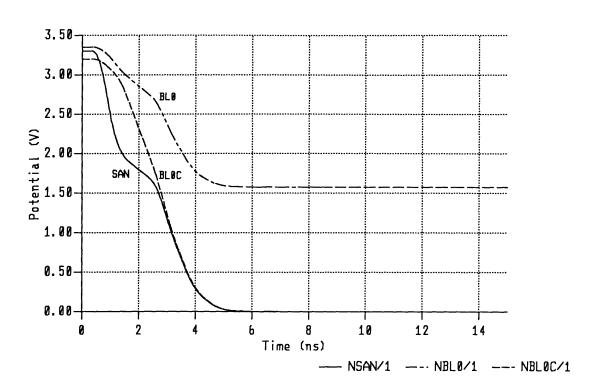

|      | Isolated n-channel Cross-Coupled Pair Waveforms                           | 118 |

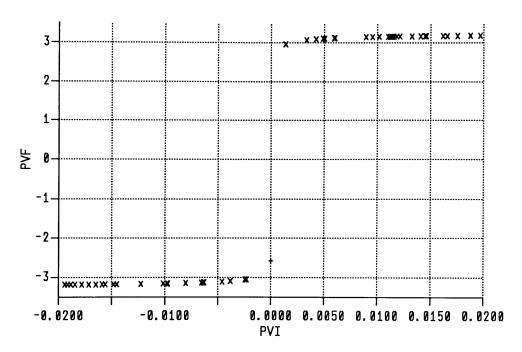

|      | $V_{DD}$ Sense Amplifier Signal After Sensing Operation v. Initial Signal | 119 |

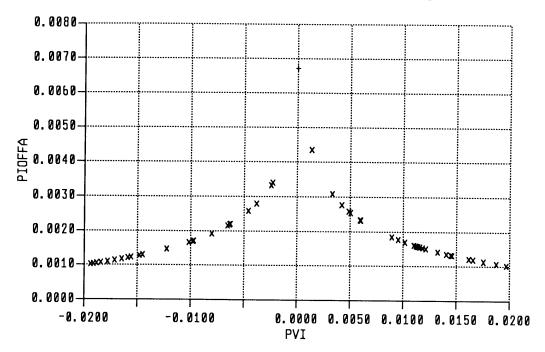

|      | $V_{DD}$ Sense Amplifier Average Off-Side Current v. Initial Signal       | 120 |

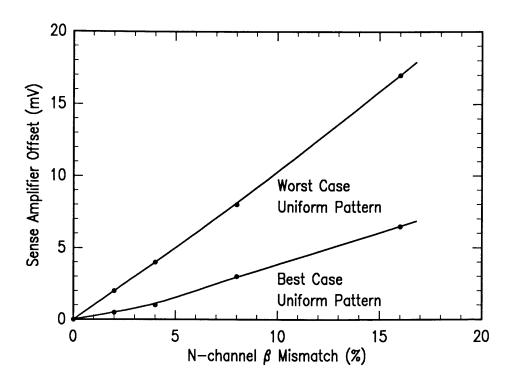

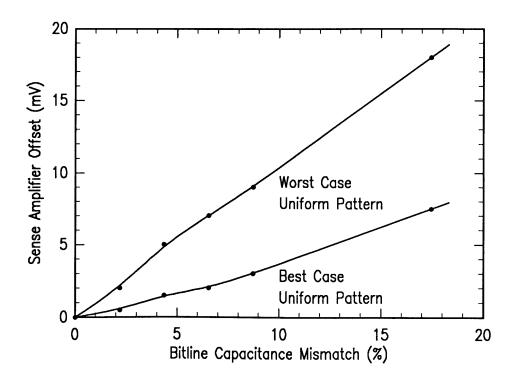

|      | $V_{DD}$ Sense Amplifier Offset due to Transistor Gain Mismatch           | 121 |

|      | $V_{DD}$ Sense Amplifier Offset due to Bitline Capacitance Mismatch       | 121 |

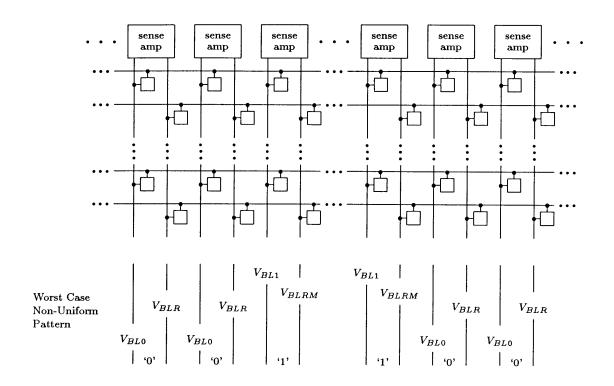

| 5.20 | Non-Uniform Patterns for Process Variation Induced Offset Charac-         |     |

|      | terization                                                                | 122 |

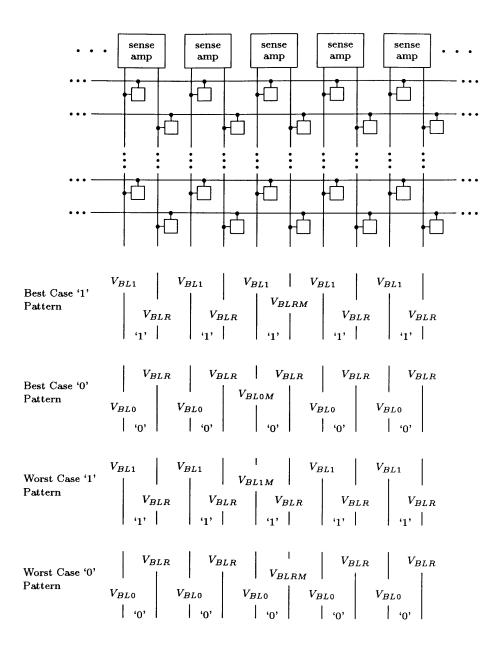

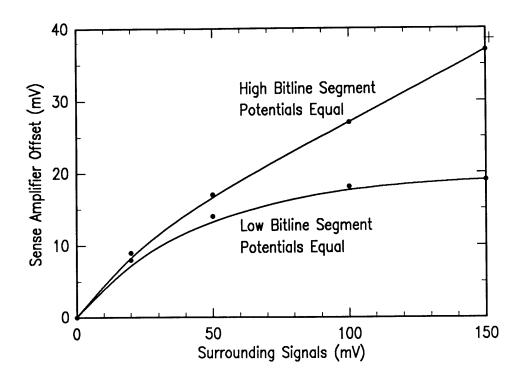

|      | Patterns for Bitline Coupling Induced Offset Characterization             | 123 |

| 5.22 | $V_{DD}$ Sense Amplifier Offset due to Bitline-to-Bitline Coupling        | 124 |

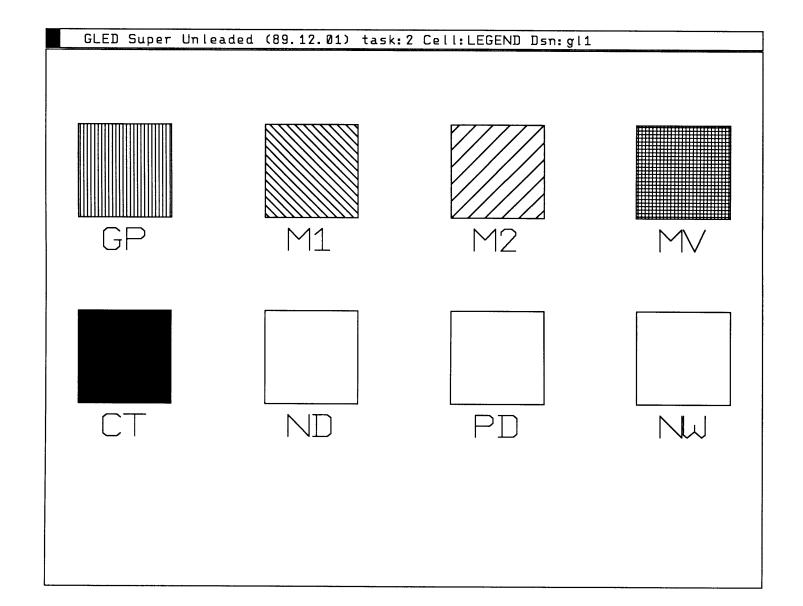

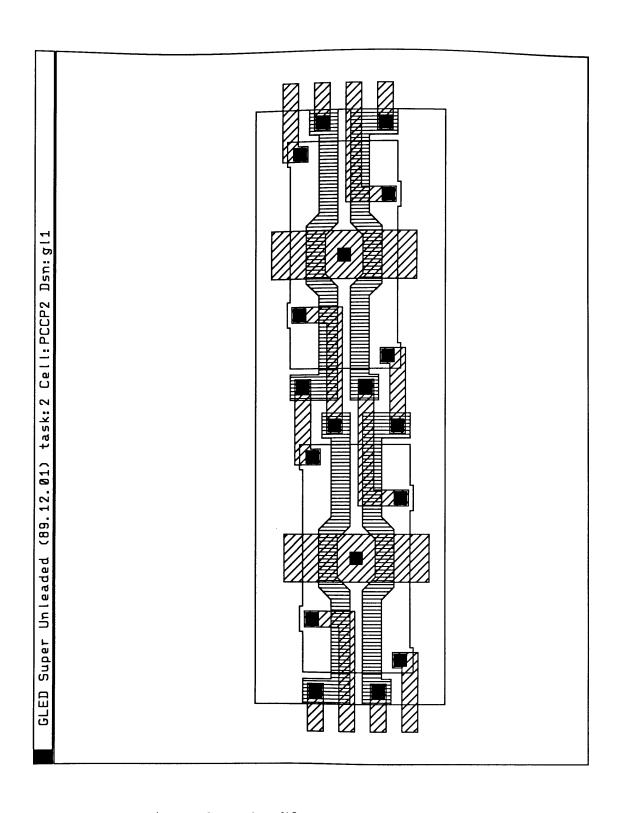

| B.1  | Layout Legend                                                             | 168 |

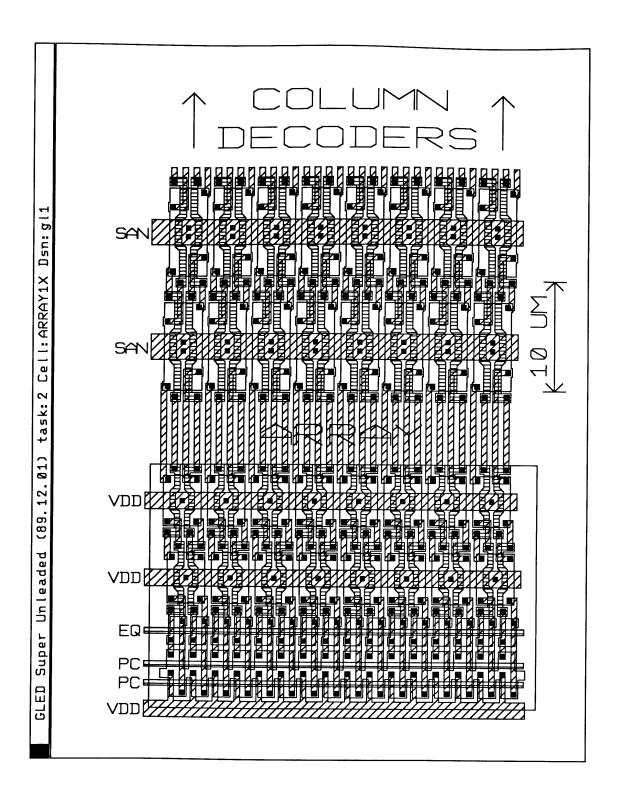

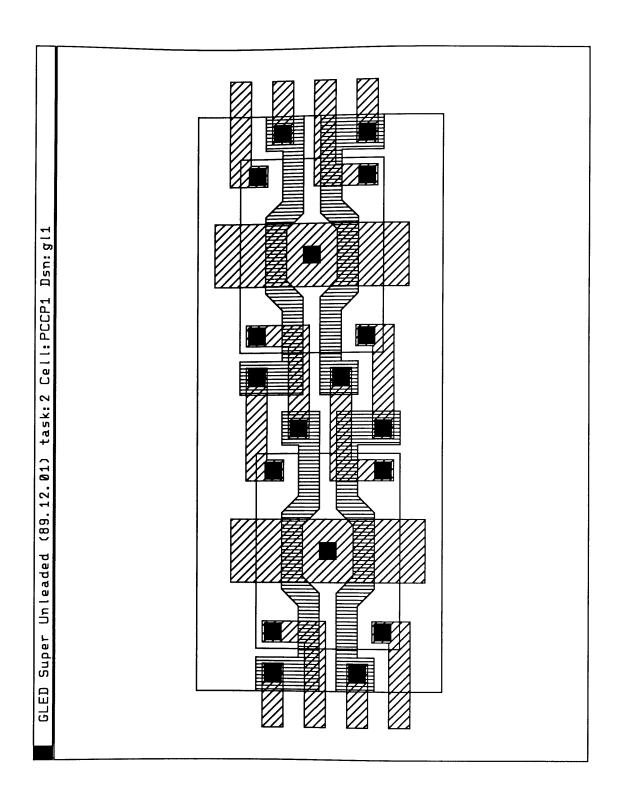

| B.2  | $V_{DD}$ Sense Amplifier Layout                                           | 169 |

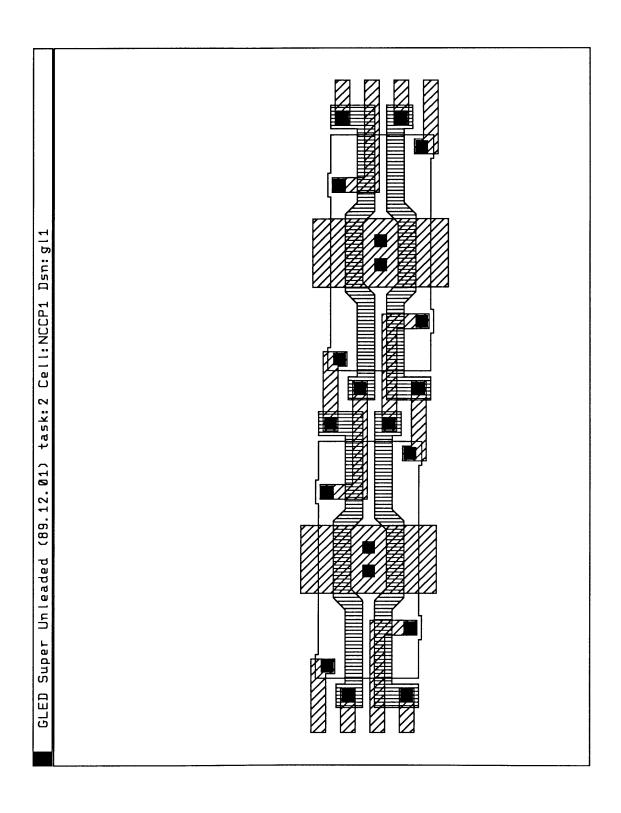

| B.3  | $V_{DD}$ Sense Amplifier <i>n</i> -channel Cross-Coupled Pair Layout      | 170 |

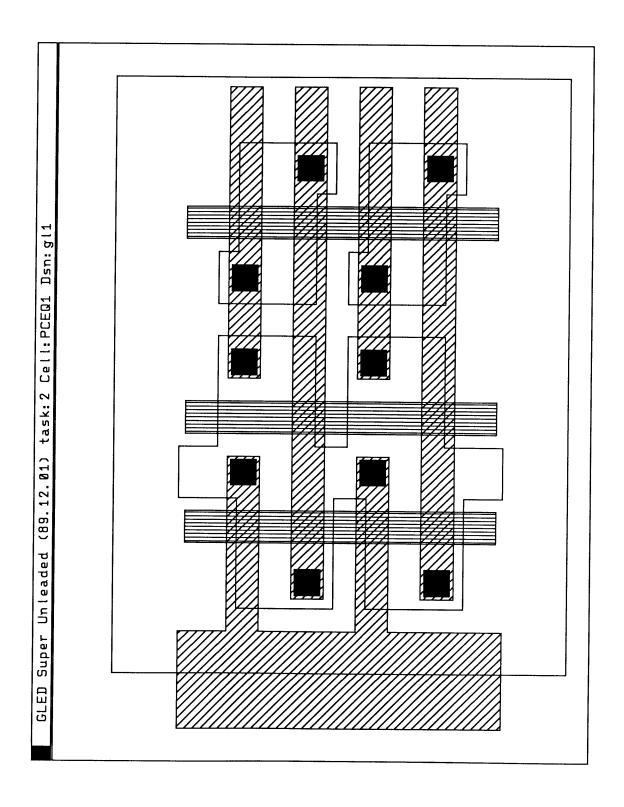

| B.4  | $V_{DD}$ Sense Amplifier p-channel Cross-Coupled Pair Layout              | 171 |

| B.5  | $V_{DD}$ Sense Amplifier Precharge and Equalization Device Layout         | 172 |

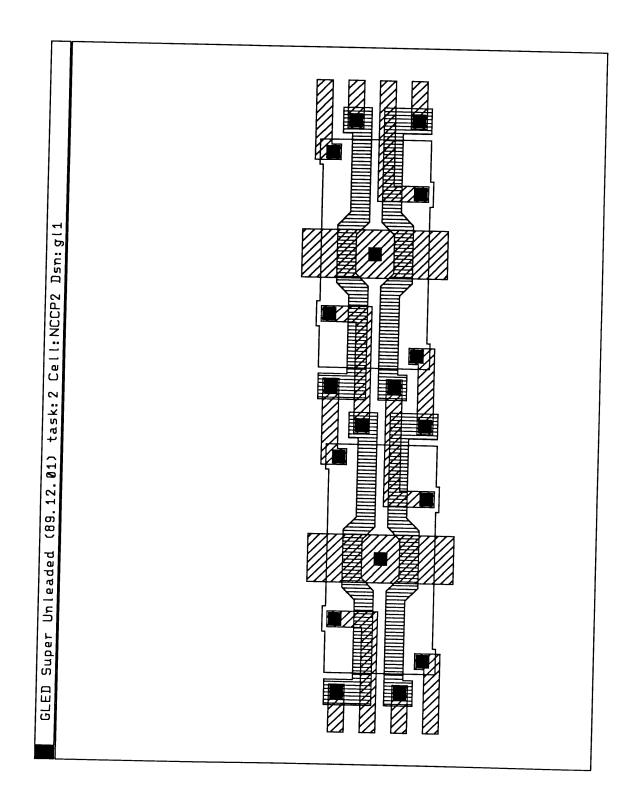

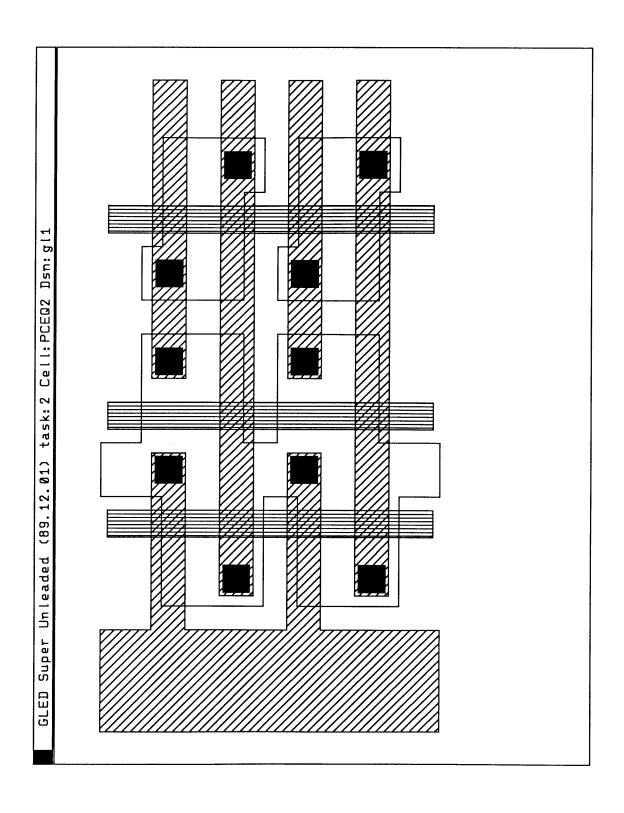

| B.6  | $1/2 V_{DD}$ Sense Amplifier Layout                                       | 173 |

| B.7  | $1/2 V_{DD}$ Sense Amplifier <i>n</i> -channel Cross-Coupled Pair Layout  | 174 |

| B.8  | $1/2 V_{DD}$ Sense Amplifier p-channel Cross-Coupled Pair Layout          | 175 |

| B.9  | $1/2 V_{DD}$ Sense Amplifier Precharge and Equalization Device Layout .   | 176 |

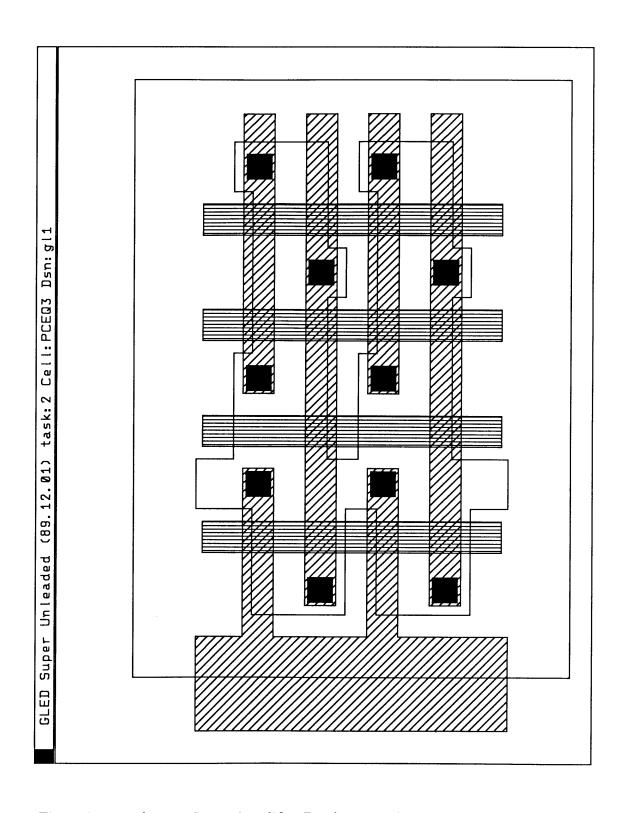

| B.10 | $2/3 V_{DD}$ Sense Amplifier Layout                                       | 177 |

| B.11 | $2/3 V_{DD}$ Sense Amplifier Precharge and Equalization Device Layout .   | 178 |

|      | Isolation Device Layout                                                   | 179 |

## List of Tables

| DRAM Cell Evolution                            |

|------------------------------------------------|

| Projected 64M DRAM Technology Parameters       |

| Projected 64M DRAM Performance Parameters      |

| 64M DRAM Design Rules                          |

| 64M DRAM Intrinsic Bitline Power Dissipation   |

| 2K, 4K, and 8K DRAM Performance Specifications |

| 2K, 4K, and 8K DRAM Process Technologies       |

| 2K, 4K, and 8K DRAM Features                   |

| 16K DRAM Performance Specifications            |

| 16K DRAM Process Technologies                  |

| 16K DRAM Features                              |

| 64K DRAM Performance Specifications            |

| 64K DRAM Process Technologies                  |

| 64K DRAM Features                              |

| 256K DRAM Performance Specifications           |

| 256K DRAM Process Technologies                 |

| 256K DRAM Features                             |

| 3 1M DRAM Performance Specifications           |

| 1M DRAM Process Technologies                   |

| 51M DRAM Features                              |

| 34M DRAM Performance Specifications            |

| '4M DRAM Process Technologies                  |

| 34M DRAM Features                              |

| 16M DRAM Performance Specifications            |

| 16M DRAM Process Technologies                  |

| 16M DRAM Features                              |

|                                                |

## Chapter 1

### Introduction

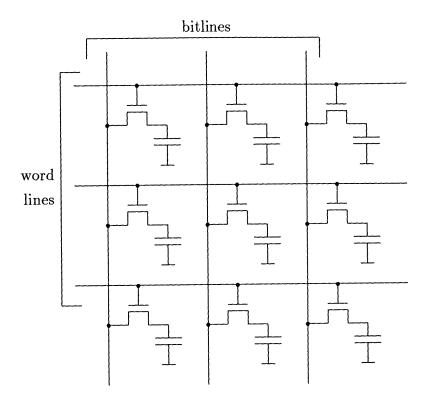

Since the early 1970's, high density dynamic random access memory (DRAM) chips have been based on the one-transistor cell array, patented by Dennard in 1968 [1]. As shown in Figure 1.1, each cell comprises a single access transistor and a single storage capacitor. Binary information is represented by the state of the storage capacitors. Each cell holds a single bit. Typically, a high stored potential represents a '1' and a low stored potential represents a '0'. Cells must be periodically refreshed to prevent loss of data due to charge leakage.

Wordlines connect the access transistor gates of each cell row. Activating a wordline turns on the access transistors, connecting the cell storage capacitors to bitlines. Data may then be read from or written to the cells through the bitlines. Each bitline serves a column of cells. Deactivating the wordline isolates the storage capacitors from the bitlines.

Before activating a wordline to read or refresh a cell row, the bitlines are precharged to a common potential. Activation of the wordline causes charge sharing to occur between cell storage capacitors and bitlines. Small signals reflecting cell states are produced on each bitline. The signals must be amplified, and the original state of the storage capacitors must be restored. These functions are performed by sense amplifiers.

Figure 1.1: DRAM Array

Sense amplifier design is critical to DRAM performance. Key DRAM characteristics, including speed, power dissipation, and error rate depend on sense amplifier features. The goal of this research is to identify the impact of processing technology parameters on sense amplifier design and to propose designs suitable for 64 Megabit DRAMs.

#### 1.1 Divided Bitline Architecture

The 2K DRAM introduced by Cohen et al. in 1971 [2] was the first published DRAM using a single-transistor cell. This chip, and a few early 4K DRAMs, employed continuous bitlines and single-ended sense amplifiers. Singe-ended sensing involved either precharging the bitlines to the switching threshold of an inverter [3],[4], or sampling the bitline voltages just before activating the wordline [5]. The former approach incurs static power dissipation through the amplifier during the precharge interval. The latter approach requires several sensitive clock signals and is susceptible to common mode noise introduced after bitline voltage sampling.

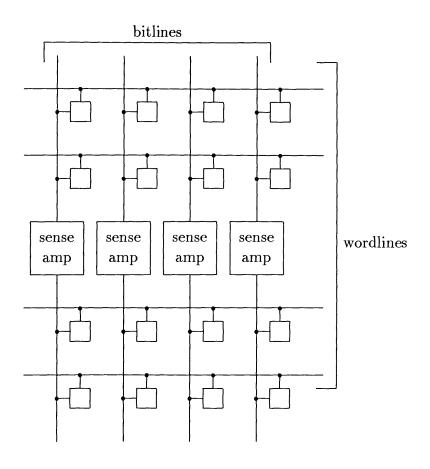

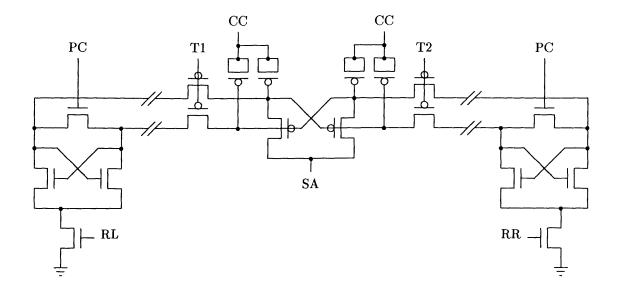

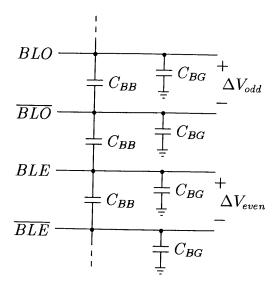

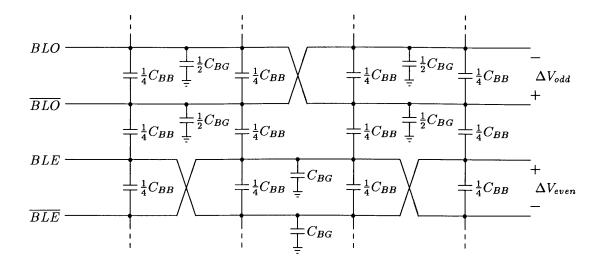

In 1972, Stein et al. proposed the divided bitline architecture [6],[7]. As shown in Figure 1.2, each bitline is split into two matched segments, one on each side of the sense amplifier. Differential sense amplifiers are employed, avoiding many of the difficulties of single-ended sensing. Using this architecture, Hoffman and Kalter achieved quantity production on an 8K DRAM in 1973 [8],[9]. 16K and higher density DRAMs have been based on the divided bitline architecture.

Read and refresh cycles of DRAMs using the divided bitline architecture proceed as follows. First, the bitline segments are precharged to a common potential,  $V_{PC}$ . Next, the selected wordline is activated. Bitline segments on the same side of the sense amplifiers as the wordline are connected to cell storage capacitors. Assuming the activated wordline is driven sufficiently high, the potentials of the selected cell storage

Figure 1.2: Divided Bit Line Architecture

capacitors and their corresponding bitline segments are equalized. The potential of bitline segments connected to cells storing a '1' is

$$V_{BL1} = \frac{V_{PC}C_{BT} + V_{S1}C_S}{C_{BT} + C_S},\tag{1.1}$$

while the potential of bitline segments connected to cells storing a '0' is

$$V_{BL0} = \frac{V_{PC}C_{BT} + V_{S0}C_S}{C_{BT} + C_S}. (1.2)$$

$V_{S1}$  and  $V_{S0}$  are the stored '1' and '0' potentials. Commonly  $V_{S1} = V_{DD}$  and  $V_{S0} = 0$  (ground).  $C_{BT}$  is the total effective bitline segment capacitance, excluding storage cell capacitance.  $C_S$  is the storage cell capacitance.

On the opposite bitline segments, a reference potential, midway between  $V_{BL1}$  and  $V_{BL0}$ , must be present. This can be accomplished either by setting the precharge potential,  $V_{PC}$ , midway between  $V_{S1}$  and  $V_{S0}$  or by employing dummy cells as suggested by Stein *et al.* [6], [7]. The sense circuitry amplifies the potential differences between the two bitline segments in each column and recharges the storage capacitors to full '1' and '0' potentials.

The initial sense amplifier signal magnitude is limited by the ratio of the bitline capacitance to the storage cell capacitance. The raw signal developed across the sense amplifiers is

$$\Delta V = \frac{V_{BL1} - V_{BL0}}{2} = \frac{1}{2} \frac{(V_{S1} - V_{S0})}{(C_{BT}/C_S + 1)}.$$

(1.3)

Typically the transfer ratio,  $C_{BT}/C_S$ , is in the 5-20 range. As the number of cells per bitline increases, maintaining a constant transfer ratio requires decreasing the bitline capacitance per bit and/or increasing the storage cell capacitance.

#### 1.1.1 Signal Loss Due to Incomplete Charge Transfer

The above analysis assumed the activated wordline is driven sufficiently high to equalize the potentials of the selected cell storage capacitors and their corresponding bit-

line segments. In some DRAM designs, this assumption is invalid. For example, if  $V_{S0} = 0$ ,  $V_{PC} = V_{DD}$  and the wordline is not driven above  $V_{DD}$  during signal development, n-channel transfer devices accessing a stored '0' will shut off when the storage cell potential reaches  $V_{DD} - V_T$ , where  $V_T$  is the transfer device threshold voltage.

Equations (1.1), (1.2), and (1.3) can be modified to encompass cases involving incomplete equalization. After signal development is complete, the potential of bitline segments connected to cells storing a '1' is

$$V_{BL1} = \frac{V_{PC}C_{BT} + V_{S1}C_S - (V_{C1} - V_{BL1})C_S}{C_{BT} + C_S},$$

(1.4)

where  $V_{C1}$  is the final potential of the '1' storage cells. The potential of bitline segments connected to cells storing a '0' is

$$V_{BL0} = \frac{V_{PC}C_{BT} + V_{S0}C_S - (V_{C0} - V_{BL0})C_S}{C_{BT} + C_S},$$

(1.5)

where  $V_{C0}$  is the final potential of the '0' storage cells. Thus, the raw signal developed across the sense amplifiers is

$$\Delta V = \frac{1}{2} \frac{(V_{S1} - V_{S0}) - (V_{C1} - V_{BL1}) - (V_{BL0} - V_{C0})}{(C_{BT}/C_S + 1)}.$$

(1.6)

#### 1.1.2 Dummy Storage Cells

Unless the bitline precharge potential is midway between  $V_{BL1}$  and  $V_{BL0}$ , dummy cells must be used. A single row of dummy cells is placed on each side of the sense amplifier. The basic structure of the dummy cells is identical to the normal storage cell structure. Dummy wordlines connect the access transistor gates of each dummy cell row. The dummy storage capacitors are precharged to a common potential. When the selected wordline is activated, the dummy wordline on the opposite side of the sense amplifier is also activated.

The dummy storage capacitor precharge potential and capacitance are designed to produce the proper bitline segment reference potential. Two schemes are common. In the first scheme, the dummy cell capacitance is equal to the normal storage cell capacitance. The dummy storage capacitors are precharged to a potential midway between  $V_{S1}$  and  $V_{S0}$ . In the other arrangement, the bitlines are precharged to  $V_{S1}$ . The dummy cell capacitors, with about one-half the capacitance of the normal storage cell capacitors, are precharged to  $V_{S0}$ . When the wordline and dummy wordline are activated, the potentials of bitline segments connected to cells storing a '1' remain at  $V_{S1}$ . The potentials of segments connected to cells storing a '0' drop to  $V_{S1}C_{BT}/(C_{BT} + C_S)$ . The potentials of segments connected to dummy cells drop to

The first scheme allows use of any bitline precharge potential but requires precharging the dummy storage cell capacitors to an intermediate potential. A dummy cell precharge voltage generator may be needed. The second scheme constrains the bitline precharge potential and requires a unique dummy storage cell capacitance. It also creates an imbalance in the bitline segment node capacitances during sensing.

#### 1.2 Noise Sources

A wide variety of phenomena, commonly referred to as "noise sources," may degrade signals presented to the sense amplifiers. Equations (1.3) and (1.6) do not account for these phenomena. Yet the noises produced are often of such magnitude that they may not be safely neglected.

Bitline, storage cell, and dummy cell capacitance variations alter the bitline potentials produced by signal development. Process tolerances and mismatches must both be considered. Capacitances may vary both globally, from chip to chip, and locally, from cell to cell or bitline to bitline.

Figure 1.3: Required Tolerance versus Number of Occurrences. 95%, 99%, and 99.9% Chances of All Occurrences Falling Within Tolerance.

As DRAM chip capacity grows, the number of cell and sense amplifier related structures increases. As a result, to maintain constant yield, process tolerances related to these structures must be increased. Figure 1.3 illustrates this relationship. A Gaussian distribution is assumed.

Voltages which are ideally constant may vary, resulting in signal loss. Fluctuations in the storage capacitor plate potential may result from supply voltage skew, wordline-plate coupling, or bitline-plate coupling. Stored '0' and '1' and dummy storage capacitor potential variations may be caused by incomplete charge storage, supply voltage skew, storage capacitor leakage, or subthreshold transfer device leakage. If a dummy storage capacitor precharge voltage generator is used, non-ideal operation of the voltage generator may also cause precharge voltage variations. Local differences in bitline segment precharge potentials may result from incomplete precharge, supply voltage skew, or bitline charge leakage. Global precharge potential variations,

important in designs not employing dummy cells, may be caused by supply voltage skew or, if a bitline precharge voltage generator is employed, non-ideal operation of the voltage generator.

Injection of minority carriers into the bulk region of the array may cause signal loss. Charge injection can occur as a result of alpha particle radiation or chip input undershoot or overshoot. Injected charge collected by cell storage capacitors may alter the stored potentials. In addition, during signal development injected charge may be collected by the bitline segments, altering the bitline potentials.

Electrical coupling within the array affects signal development. Changes in word-line potential can result in storage cell state-dependent changes in bitline and storage capacitor potentials. Bitline to bitline coupling results in pattern-dependent effective bitline capacitance changes. Bitline potential changes during signal development may induce changes in wordline, bulk, or plate potentials. These changes may, in turn, alter the bitline potentials.

#### 1.3 Folded Bitline Architecture

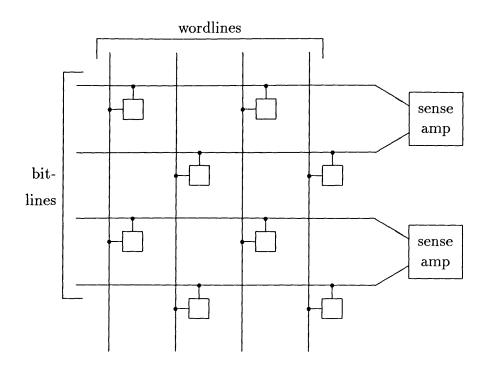

In the conventional divided bitline arrangement shown in Figure 1.2, matched bitline segments extend from opposite sides of the sense amplifiers. This arrangement is used in most 16K DRAMs. The folded bitline architecture, shown in Figure 1.4, is used in many 64K and higher density DRAMs. It requires a more complex cell structure, but offers several advantages over the conventional open bitline architecture.

With open bitlines, differential column I/O sensing requires placement of column decode circuits between the sense amplifiers and the array. Use of folded bitlines allows placement of column decode circuitry at the ends of the bitlines, reducing bitline capacitance and eliminating coupling between the bitlines and the column address lines [10], [11], [12].

Figure 1.4: Folded Bit Line Architecture

The folded bitline architecture reduces the sense amplifier pitch constraint from one bitline segment pitch to two bitline segment pitches. In many cases, this may allow more efficient sense amplifier layout [13].

Employing folded bitlines may help improve noise rejection. Some mechanisms which introduce differential mode noise in open bitline designs may produce only common mode noise in folded bitline configurations [14], [15].

The folded bitline architecture reduces the physical distance between paired bitline segments. Thus folded arrays are, in general, less sensitive to spatial bulk and plate potential variations. In addition, during signal development, roughly equal amounts of injected charge may be collected by neighboring bitline segments. Thus, charge injection during signal development may produce smaller changes in potential between paired bitline segments in a folded bitline arrangement.

In open bitline configurations, the average bitline potential change in each storage cell array is highly dependent on the stored pattern. In most folded configurations, the average bitline potential change is independent of the stored pattern. Thus, in a folded bitline architecture, differential plate, bulk, and wordline potential changes resulting from coupling to bitlines may be reduced.

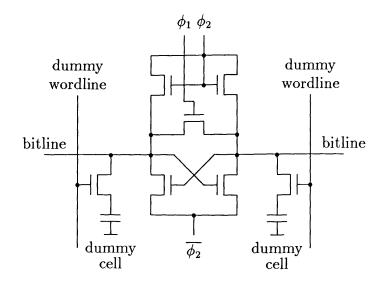

#### 1.4 Balanced Flip-Flop Sense Amplifier

The differential sense amplifiers used in modern DRAMs are variations of the balanced flip-flop sense amplifier presented by Stein et al. in 1972 [6],[7]. The circuit is shown in Figure 1.5. During the precharge period  $\phi_1$  and  $\phi_2$  are high,  $\overline{\phi_2}$  is low, and both dummy wordlines are activated. The bitline and dummy cell potentials are set to the switching threshold of the flip-flop. After the precharge voltage is established,  $\phi_1$  and  $\phi_2$  go low,  $\overline{\phi_2}$  goes high, and the dummy wordlines are deactivated. When a wordline is activated, the dummy wordline on the opposite side of the sense amplifier is also activated. Offset introduced by capacitive coupling of bitline segments to the active wordline is compensated by coupling of the opposite segments to the active dummy wordline. Driving  $\phi_2$  high and  $\overline{\phi_2}$  low activates the flip-flop, initiating sense signal amplification. The lower potential bitline segment is discharged through one of the cross-coupled transistors. The higher potential segment is pulled up through one of the load transistors.

In 16K and higher density DRAMs, sense amplifier performance is improved by keeping static load transistors off during signal amplification and by driving the source of the cross-coupled pair slowly during initial sensing as suggested by Lynch and Boll [16]. If static load transistors are activated at the same time as the cross-coupled device pair, current flows through a load device into the lower potential bitline segment, unproductively dissipating power. In addition, the load device current going into the

Figure 1.5: Stein et al. Balanced Flip-Flop Sense Amplifier

lower potential bitline is greater than the current going into the higher potential bitline. This difference hinders signal amplification. Keeping the load devices off until amplification of the sense signal through the cross-coupled pair is complete reduces power dissipation, speeds amplification, and eliminates offset due to load transistor mismatch. Driving the cross-coupled pair source node slowly during initial sensing reduces and can even eliminate current flow from the higher potential bitline segment through the flip-flop. As a result, power dissipation is lower, and a greater potential difference between the bitline segments can be developed. In addition, sense amplifier operation will be less sensitive to bitline capacitance imbalances and to geometry mismatches between the cross-coupled transistors [17], [18], [19].

#### 1.5 DRAM Evolution

Over the last two decades, DRAM chip capabilities have dramatically improved. Advances in circuit and processing technology have produced a new DRAM generation,

with 4x greater chip capacity, every 2-4 years. 4M DRAMs are now in production. As shown in Figure 1.6, access time has gradually improved. Large decreases in power dissipation per bit, shown in Figure 1.7, have limited increases in chip power.

Increased chip capacity has been achieved primarily by decreasing cell size and increasing chip area. As shown in Figure 1.8, chip area has increased approximately 1.5x per generation. Cell area decreased by approximately 2.5x per generation as shown in Figure 1.9. Together, these two trends account for over 90% of the increase in chip capacity with each generation.

The decrease in cell area has been obtained by reducing feature sizes and by employing new cell structures. As shown in Figure 1.10, feature sizes have been reduced by about 1.4x per generation. This reduction accounts for a 2.1x reduction in cell area per generation. The remaining 1.2x cell area reduction has been produced through cell structure innovation.

The need to preserve charge capacity constrains cell evolution. Charge capacity is the difference in stored charge between '0' and '1' cell capacitor states, and is given by

$$Q_C \equiv \int_{V_{S0}}^{V_{S1}} C_S(V_S) \, dV_S \sim C_S \Delta V_S \tag{1.7}$$

where  $\Delta V_S$  is the potential difference between stored '0' and '1' levels. Maximum sense signal magnitude is related to charge capacity by

$$\Delta V = \frac{1}{2} \frac{Q_C}{C_{BT} + C_S} \simeq \frac{1}{2} \frac{Q_C}{C_{BT}} \tag{1.8}$$

As chip capacity increases, decreases in bitline capacitance per bit are generally accompanied by increases in the number of cells per bitline. As a result, bitline segment capacitance remains roughly constant. Thus, charge capacity must be conserved in order to maintain adequate sense signal magnitude.

Particle-induced soft error rate considerations also discourage charge capacity re-

Figure 1.6: Access Time versus DRAM Generation

Figure 1.7: Power per Bit versus DRAM Generation

Figure 1.8: Chip Area versus DRAM Generation

Figure 1.9: Cell Area versus DRAM Generation

Figure 1.10: Feature Sizes versus DRAM Generation

duction. Soft errors occur when energetic particles upset stored data. Soft error sensitivity depends on the critical charge, the amount of charge needed to change the state of a cell. Critical charge is equal to the difference between the cell charge capacity and the amount of charge needed to guarantee proper sense amplifier operation, assuming nominal noise levels. For a given sense amplifier latch requirement and nominal noise level, decreasing cell charge capacity decreases critical charge. Soft error rates increase exponentially with decreasing critical charge [20].

Insulator properties limit charge capacity per unit capacitor storage area. For storage capacitors formed using MOS structures, charge capacity is related to cell design by

$$Q_C \sim \frac{\epsilon A_S}{d} \Delta V_S \tag{1.9}$$

where  $\epsilon$  is the insulator dielectric constant,  $A_S$  is the capacitor storage area and d is the insulator thickness.  $\Delta V_S/d$  must be restricted to avoid excessive leakage current

| 4K                     | 16K                    |

|------------------------|------------------------|

| planar cell            | planar cell            |

| metal wordlines        | metal wordlines        |

| diffused bitlines      | diffused bitlines      |

| single-level poly      | double-level poly      |

|                        |                        |

| 64K                    | 256K                   |

| planar cell            | Hi-C planar cell       |

| poly Si wordlines      | polycide wordlines     |

| metal bitlines         | metal bitlines         |

| double-level poly      | double-level poly      |

|                        |                        |

| 1M                     | 4M,16M                 |

| Hi-C planar cell       | trench or stacked      |

| $1/2 V_{DD}$ plate     | capacitor cell         |

| poly Si wordlines      | poly Si wordlines      |

| metal bypass wordlines | metal bypass wordlines |

| polycide bitlines      | polycide bitlines      |

| triple-level poly      |                        |

Table 1.1: DRAM Cell Evolution

and insulator breakdown due to high electric fields. Thus, charge capacity per unit storage area,  $Q_C/A_S$ , is limited by the product of the dielectric constant and the maximum electric field,  $\epsilon \mathcal{E}_{max}$ .

Design advances have increased cell charge capacity per unit cell area, enabling cell area to be reduced with each new DRAM generation. Table 1.1 shows the evolution of typical cell structures. Rideout [21] has provided an excellent review of cell structures used in 4K and 16K DRAMs. Asai [22] and Sunami [23], [24] have published overviews of cell design trends. Noble [25] has examined cell design constraints. Stacked capacitor and trench capacitor cells suitable for high-density DRAMs have been reviewed by Lu [26] and Maes [27].

Table 1.2 shows the development of typical DRAM process features. Device length,

|                    | 4K    | 16K   | 64K  | 256K | 1M    | 4M   | 16M   |

|--------------------|-------|-------|------|------|-------|------|-------|

| Technology         | PMOS/ | NMOS  | NMOS | NMOS | NMOS/ | CMOS | CMOS  |

|                    | NMOS  |       |      |      | CMOS  |      |       |

| Internal Supply    | 12,5, | 12,5, | 5    | 5    | 5     | 5    | 3.3-4 |

| Voltage(s) (V)     | -3    | -5    |      |      |       |      |       |

| Device Length (µm) | 7     | 5-6   | 2-3  | 1.5  | 1.2   | 1.0  | 0.6   |

| Gate Oxide         | 1000  | 1000  | 500  | 350  | 250   | 200  | 150   |

| Thickness (Å)      |       |       |      |      |       |      |       |

Table 1.2: DRAM Process Evolution

gate oxide thickness, and internal supply voltages have been reduced as chip capacity increases. In addition, CMOS has supplanted NMOS as the dominant technology.

## Chapter 2

## Theoretical Analysis of Sense Amplifier Operation

Theoretical analysis of the sensing operation is useful for understanding circuit performance. While computer simulation may provide more precise results, theoretical analysis gives a much clearer picture of design and process parameter influences.

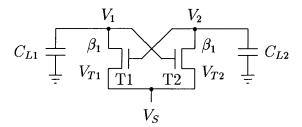

This chapter will focus on the operation of the cross-coupled MOS transistor pair. The circuit, shown in Figure 2.1, is the core of all modern DRAM sense amplifiers. Two issues will be addressed. First, given device parameters, what is the optimal latching pulse,  $V_S(t)$ ? Second, given device parameters and constraints on the latching pulse, what is the sensitivity of the amplifier circuit?

Figure 2.1: Cross-Coupled n-channel MOSFET Sense Amplifier Circuit

The following first-order MOS transistor current expressions will be used:

$$I_{DS} = \begin{cases} \beta(V_{GS} - V_T - \frac{1}{2}V_{DS})V_{DS}, & V_{DS} \le V_{GS} - V_T \\ \frac{1}{2}\beta(V_{GS} - V_T)^2. & V_{DS} > V_{GS} - V_T \end{cases}$$

(2.1)

$V_{GS}$  is the gate-source voltage,  $V_{DS}$  is the drain-source voltage, and  $V_T$  is the threshold voltage.  $\beta$  is the transistor gain factor and is given by

$$\beta \equiv \frac{W}{L} \mu_{eff} C_{ox} \tag{2.2}$$

where W and L are the transistor lengths and widths, respectively,  $\mu_{eff}$  is the effective channel mobility, and  $C_{ox}$  is the gate oxide capacitance per unit area.

#### 2.1 Latching Pulse Optimization

Sense amplifier performance depends on characteristics of the latching pulse,  $V_S(t)$ . Following the analysis of Lynch and Boll [16], the optimal latching pulse will be derived, given the constraint that no current may flow through the "off-side" (T2) of the flip-flop. Perfect matching will be assumed, giving

$$(W/L) = (W/L)_1 = (W/L)_2,$$

$\beta = \beta_1 = \beta_2,$   $V_T = V_{T1} = V_{T2},$   $C_L = C_{L1} = C_{L2}.$  (2.3)

Gate-source capacitances will be neglected for  $V_{GS} < V_T$ . They will be assumed constant for  $V_{GS} \ge V_T$ . A constant,  $C_C$ , will be used to model the capacitance between the two signal nodes. Variations in threshold voltages with device operating points will be ignored.

Prior to the start of the sensing operation,  $V_1 = V_0$  and  $V_2 = V_0 + v$ , where v is the magnitude of the signal presented to the amplifier.  $V_S > V_0 - V_T + v$ , keeping both T1 and T2 off. Amplification begins, at t = 0, when the latch node potential,  $V_S$ , is driven below  $V_0 - V_T + v$ , turning on T1.

To maximize sensing speed,  $V_S$  should decrease as quickly as possible. Preventing off-side conduction requires  $V_1 - V_S \leq V_T$ . Thus, maximum sensing speed without off-side conduction is achieved when

$$V_S(t) = V_1(t) - V_T. (2.4)$$

Initially, the optimal latching pulse is a negative step to  $V_0 - V_T$ . T1 will conduct, reducing  $V_1$ .  $V_S$  should decrease with  $V_1$ , always keeping T2 marginally off. As  $V_S$  decreases, the overdrive on T1 increases, and consequently  $V_1$  decreases more rapidly. Thus, after the initial step,  $V_S$  will decrease at a progressively increasing rate.

Though T2 is always kept off,  $V_2$  decreases as a result of capacitive coupling between the two signal nodes and T1 gate-source coupling. For  $V_2 - V_S \ge V_T$ , charge conservation requires

$$(V_0 + v)C_L + vC_C = V_2(t)C_L + [V_2(t) - V_1(t)]C_C + [V_2(t) - V_S(t) - V_T]C_{GS}$$

(2.5)

where  $C_{GS}$  is the gate-source capacitance. Using (2.4) in this expression gives an equation for  $V_2(t)$ :

$$V_2(t) = V_S(t) + V_T + f_1[V_0 - V_S(t) - V_T] + f_2v$$

(2.6)

where

$$f_1 \equiv \frac{C_L}{C_L + C_C + C_{GS}}$$

and  $f_2 \equiv \frac{C_L + C_C}{C_L + C_C + C_{GS}}$ . (2.7)

Assigning t = 0 at the instant immediately before  $V_S$  begins decreasing, the node potentials at  $t = 0^+$ , immediately after the negative  $V_S$  step, are given by

$$V_1(0^+) = V_0 V_2(0^+) = V_0 + f_2 v V_S(0^+) = V_0 - V_T.$$

(2.8)

While  $V_1 > V_2 - V_T$ , T1 operates in the saturation regime and

$$-C_L \frac{dV_1(t)}{dt} - C_C \left[ \frac{dV_1(t)}{dt} - \frac{dV_2(t)}{dt} \right] = \frac{\beta}{2} [V_2(t) - V_S(t) - V_T]^2.$$

(2.9)

Using (2.4) and (2.6) in (2.9) gives a differential equation for  $V_S(t)$ :

$$-(C_L + f_1 C_C) \frac{dV_S(t)}{dt} = \frac{\beta}{2} \{ f_1 [V_0 - V_S(t) - V_T] + f_2 v \}^2.$$

(2.10)

The solution to (2.10) with the initial condition given by (2.8) is

$$V_S(t) = V_0 - V_T - \frac{[\beta/2(C_L + f_1 C_C)]f_2^2 v^2 t}{1 - [\beta/2(C_L + f_1 C_C)]f_1 f_2 v t}.$$

(2.11)

Equation (2.11) is valid until, at  $t = t_{sat}$ , T1 goes into the linear operation regime.  $t_{sat}$  is defined by

$$V_1(t_{sat}) = V_2(t_{sat}) - V_T. (2.12)$$

Using (2.4), (2.6), and (2.11) in (2.12) gives

$$t_{sat} = \frac{2(C_L + f_1 C_C)}{\beta f_1 f_2 v} \frac{(V_T - f_2 v)}{V_T} = \frac{2(C_L + 2C_C + C_{GS})}{\beta f_2 v} \frac{(V_T - f_2 v)}{V_T}.$$

(2.13)

Substituting (2.13) in (2.11) gives

$$V_S(t_{sat}) = V_0 - V_T - \frac{1}{f_1}(V_T - f_2 v). \tag{2.14}$$

Once T1 is operating in the linear regime

$$-(C_L + f_1 C_C) \frac{dV_S(t)}{dt} = \beta \left\{ V_2(t) - V_S(t) - V_T - \left[ \frac{V_1(t) - V_S(t)}{2} \right] \right\} [V_1(t) - V_S(t)].$$

(2.15)

Using (2.4) and (2.6) in (2.15) gives a differential equation for  $V_S(t)$ :

$$-(C_L + f_1 C_C) \frac{dV_S(t)}{dt} = \beta V_T \left\{ f_1 [V_0 - V_S(t) - V_T] + f_2 v - \frac{V_T}{2} \right\}.$$

(2.16)

The solution to this equation with the initial condition given by (2.14) is

$$V_S(t) = V_0 - V_T - \frac{1}{f_1} (V_T - f_2 v) + \frac{V_T}{2f_1} \left\{ 1 - \exp\left[\frac{\beta f_1 V_T (t - t_{sat})}{C_L + f_1 C_C}\right] \right\}.$$

(2.17)

The latch node potential rapidly falls according to (2.17) until  $V_S$  reaches ground. At this point the sensing operation can be considered complete.  $V_2$  will remain constant while  $V_1$  decreases towards ground. The length of the sensing operation,  $t_{sense}$ , is defined by

$$V_S(t_{sense}) = 0. (2.18)$$

Substituting (2.17) in (2.18) gives

$$t_{sense} - t_{sat} = \frac{C_L + f_1 C_C}{\beta f_1 V_T} \ln \left[ \frac{2f_1 (V_0 - V_T) - V_T + 2f_2 v}{V_T} \right]. \tag{2.19}$$

After  $V_S$  reaches ground, conduction through T1 continues pulling  $V_1$  towards ground. The final node potentials are given by

$$V_1(\text{final}) = 0$$

$V_2(\text{final}) = f_1 V_0 + f_2 v + (1 - f_2) V_T$  (2.20)

$V_S(\text{final}) = 0$ .

The total reduction of the high signal node potential,  $V_2$ , resulting from the sensing operation is given by

$$\Delta V_2[\text{coupling}] = \frac{C_C + C_{GS}}{C_L + C_C + C_{GS}} V_0 - \frac{C_{GS}}{C_L + C_C + C_{GS}} (V_T - v)$$

(2.21)

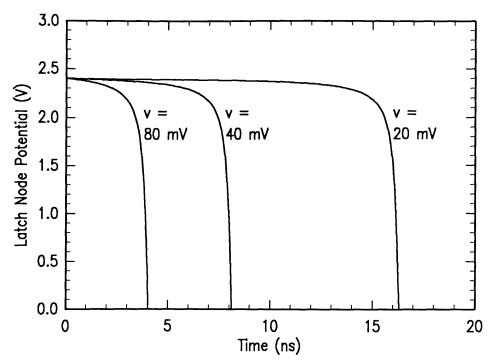

Examples of optimal  $V_S(t)$  waveforms are shown in Figure 2.2. Since, for practical parameter values,  $t_{sense} \approx t_{sat}$ , several conclusions may be drawn from (2.13) and (2.21):

- for  $C_{GS} \ll C_L + C_C$ ,  $t_{sense}$  is approximately proportional to  $(C_L + 2C_C + C_{GS})$ ;

- $t_{sense}$  is approximately inversely proportional to the transistor gain factor,  $\beta$ ;

- for  $v \ll V_T/f_2$ ,  $t_{sense}$  is approximately inversely proportional to the initial signal, v; and

- for  $V_0 \gg (V_T v)$ ,  $\Delta V_2/V_2$  (initial) is approximately equal to  $(C_C + C_{GS})/(C_L + C_C + C_{GS})$ .

Figure 2.2: Optimal Latching Pulse Waveforms

Sensing speed can be increased by allowing off-side conduction. The consequence of off-side conduction is a reduction of the final voltage of the higher potential signal node,  $V_2$ . Lynch and Boll [16] derived expressions for the optimal latching pulse assuming constant off-side current. Their analysis shows that  $t_{sat}$  is given by

$$t_{sat} = \frac{C_L}{\beta f V_C} \ln \left[ \frac{V_T}{V_T + 2V_C} \frac{fv + 2V_C}{fv} \right]$$

(2.22)

where

$$f \equiv \frac{C_L}{C_L + C_{GS}}. (2.23)$$

$V_C$  is the constant gate-source overdrive of transistor T2. Signal node coupling was neglected.

If  $V_C < 5fv$  and  $V_C \ll V_T$

$$\ln\left[\frac{V_T}{V_T + 2V_C} \frac{fv + 2V_C}{fv}\right] \approx 2 \left[\frac{\frac{fv + 2V_C}{fv} - 1}{\frac{fv + 2V_C}{fv} + 1}\right] = 2 \frac{2V_C}{2fv + 2V_C}.$$

(2.24)

Using this equation in (2.22) gives

$$t_{sat} \approx \frac{2C_L}{\beta f(fv + V_C)}$$

for  $V_C < 5fv$  and  $V_C \ll V_T$ . (2.25)

Comparing this equation and (2.13) shows that for small off-side conduction levels, the effect of increasing  $V_C$  on the length of the optimal latching pulse is similar to the effect of increasing the initial signal v. The reduction in the final voltage of the higher signal node potential due to off-side conduction is given by

$$\Delta V_2[\text{conduction}] = \frac{\beta V_C^2 t_{sense}}{2(C_L + C_{GS})} \approx \frac{\beta f V_C^2 t_{sat}}{2C_L}.$$

(2.26)

Substitution of (2.25) into (2.26) gives

$$\Delta V_2[\text{conduction}] \approx \frac{{V_C}^2}{(fv + V_C)}$$

for  $V_C < 5fv$  and  $V_C \ll V_T$ . (2.27)

For low conduction levels, the reduction in the final high signal potential is less than the "off" transistor overdrive,  $V_C$ . Thus, significant increases in sensing speed can be achieved with only small reductions in the final high signal potential. For example, sensing with  $V_C = v$  is approximately two times faster than sensing without off-side conduction. Yet the additional drop in the final high signal potential is less than v.

#### 2.2 Sensitivity

One of the most important sense amplifier performance characteristics is sensitivity. Loosely defined, the sensitivity is the minimum detectable signal presented to the sense amplifier. Natori [28] more precisely defines the sensitivity as the minimum initial signal, v, needed to insure that the resulting drop in the final high-level signal node potential due to off-side conduction,  $\Delta V_2$ , will not prevent correct subsequent circuit operation.

Sense amplifier sensitivity may be characterized by two components, offset and minimum overdrive. The offset voltage is the initial signal which results in precisely equal signal node potential changes during amplifier operation. The offset voltage of a perfectly balanced sense amplifier is zero. The minimum overdrive voltage is the minimum difference between the initial signal and the offset voltage needed to insure that the final high-level signal node potential will permit correct subsequent circuit operation. Sensitivity can be expressed as

$$v_S = v_{OS} + v_{OD,min} \tag{2.28}$$

where  $v_{OS}$  is the offset voltage and  $v_{OD,min}$  is the minimum overdrive voltage.

Because the sensing operation outcome depends on the shape of the latching pulse,  $V_S(t)$ , and the initial signal, v, characterization of sensitivity is very difficult. In whatever manner the problem is addressed, simplifying assumptions must be employed to make the analysis tractable. For any single approach, the assumptions required cast significant doubt on the general validity and applicability of the solution. However, by examining the results of several different analyses, some important conclusions can be made with a good degree of confidence.

Sensitivity will be examined in the following manner. First, the physical origins of electrical mismatches will be summarized. Then, the results of published analyses will be reviewed. Next, sense amplifier sensitivity will be related to the dc offset voltage of the MOS source-coupled pair. Finally, some general conclusions will be presented.

#### 2.2.1 Sense Amplifier Circuit Mismatches

Sensitivity is commonly characterized using electrical mismatch parameters  $\Delta V_T$ ,  $\Delta \beta$ ,  $\Delta C_L$ , and  $\Delta C_{GS}$ . These parameters are defined by the following expressions:

$$V_{T1} = V_T + \Delta V_T/2, V_{T2} = V_T - \Delta V_T/2,

\beta_1 = \beta - \Delta \beta/2, \beta_2 = \beta + \Delta \beta/2,

C_{L1} = C_L + \Delta C_L/2, C_{L2} = C_L - \Delta C_L/2,

C_{GS1} = C_{GS} + \Delta C_{GS}/2, C_{GS2} = C_{GS} - \Delta C_{GS}/2.$$

(2.29)

Many process variations result in threshold voltage mismatches. The nominal threshold voltage,  $V_T$ , is given by

$$V_T = \phi_{MS} - \frac{Q_{SS}}{C_{ox}} - \frac{Q_i}{C_{ox}} + 2\phi_f + \gamma \sqrt{V_{SB} + 2\phi_f}.$$

(2.30)

$\phi_{MS}$  is the metal-silicon work-function difference.  $Q_{SS}$  is the surface-state charge.  $Q_i$  is the effective surface charge density per unit area due to threshold adjustment implants. The oxide capacitance per unit area,  $C_{ox}$ , is given by

$$C_{ox} = \epsilon_{ox}/t_{ox} \tag{2.31}$$

where  $\epsilon_{ox}$  is the permittivity of the gate oxide and  $t_{ox}$  is the gate oxide thickness. The bulk Fermi potential,  $\phi_f$ , is given by

$$\phi_f = \frac{kT}{q} \ln \left( \frac{N}{n_i} \right) \tag{2.32}$$

where N is the bulk doping. The bulk threshold parameter,  $\gamma$ , is given by

$$\gamma = \frac{1}{C_{or}} \sqrt{2q\epsilon_{Si}N} \tag{2.33}$$

where  $\epsilon_{Si}$  is the permittivity of the silicon. From (2.30), (2.31), (2.32), and (2.33) it is apparent that variations in oxide thickness, surface-state charge, threshold adjustment implant, and bulk doping result in threshold voltage mismatches. In addition, variations in channel length may also result in threshold mismatches due to short channel effects.

The transistor gain factor,  $\beta$ , is given by (2.2). Channel width, channel length, oxide thickness, and effective mobility variations result in  $\beta$  mismatches.

In saturation, the intrinsic gate-source capacitance is given by

$$C_{GS} = \frac{2}{3}WLC_{ox}. (2.34)$$

Thus, device width, device length, and oxide thickness variations result in  $C_{GS}$  mismatches.

The total signal node to ground capacitance,  $C_L$ , includes capacitances in the sense amplifier, and unless the bitlines are completely isolated from the sense amplifier during sensing, capacitances in the storage cell array. A major component of the sense amplifier contribution is the depletion region capacitances between the bulk and drain regions of the cross-coupled devices. Bulk doping variations result in  $C_L$  mismatches. In addition, misalignment of gate and diffusion masks may create differences in cross-coupled device drain areas, resulting in capacitance mismatches. The array contribution to the signal node to ground capacitance is subject to mismatches due to a variety of process variations including differences in transfer device diffusion capacitance, differences in isolation thickness, and differences in bitline width and height.

# 2.2.2 Published Sensitivity Analyses

Ieda et al. [17], [18] analyzed sense amplifier offset using computer simulation. They assumed that the latching pulse is given by

$$V_S(t) = V_0 - V_{T2} - Kt (2.35)$$

where K is constant. They obtained the following empirical expression for sense amplifier offset:

$$v_{OS} = A\sqrt{\frac{C_L K}{\beta}} \left[ \frac{\Delta \beta}{\beta} + \frac{\Delta C_L}{C_L} \right] + \Delta V_T. \tag{2.36}$$

A is a constant. Signal node coupling capacitance was neglected.  $C_{GS}$  variations were apparently ignored.

Masuda et al. [15] examined sense amplifier offset analytically. They assumed that the latch node potential,  $V_S$ , decreases linearly with time until both transistors turn

on. Once both transistors begin conducting, the latch node potential was assumed to decrease in such a manner that the low signal node potential,  $V_1$ , decreases linearly with time according to

$$\frac{dV_2(t)}{dt} = \alpha K \tag{2.37}$$

where  $\alpha$  and K are constants. They derived the following expression for sense amplifier offset:

$$v_{OS} \approx \sqrt{\frac{C_L \alpha K}{2\beta}} \left[ \frac{\Delta \beta}{\beta} + \frac{\Delta C_L}{C_L} \right] + \Delta V_T.$$

(2.38)

Signal node coupling capacitance and gate-source capacitances were apparently ignored.

Kraus [29] also examined sense amplifier offset analytically. Like Ieda et al., he assumed that the latch node potential decreases linearly with time:

$$V_S = V_S(0) - kt. (2.39)$$

He obtained the following expression for sense amplifier offset:

$$v_{OS} \approx \Delta V_T + \sqrt{\frac{2C_{L1}k}{\beta_1}} - \sqrt{\frac{2C_{L2}k}{\beta_2}}.$$

(2.40)

Signal node coupling capacitance and gate-source capacitances were apparently ignored. If  $\Delta \beta/\beta \ll 1$  and  $\Delta C_L/C_L \ll 1$  this expression reduces to

$$v_{OS} \approx \Delta V_T + \sqrt{\frac{C_L K}{2\beta}} \left( \frac{\Delta \beta}{\beta} + \frac{\Delta C_L}{C_L} \right).$$

(2.41)

Natori [28] derived a general expression for sensitivity. He began by deriving expressions for the optimal latching pulse assuming constant off-side current. He observed that the variations in optimal  $V_S(t)$  waveforms are mostly due to changes in  $t_{sat}$ . Arbitrary  $V_S(t)$  waveforms, he argued, can be characterized by one parameter,  $t_{sat}$ , and therefore matched with an optimal  $V_S(t)$  waveform. Using results of his

optimal  $V_S(t)$  analysis, he derived the following equations for sensitivity:

$$v_S = 2V_T \zeta + \frac{1}{f} \sqrt{\frac{2(C_L + C_{GS})\Delta V_2}{\beta t_{sat}}} \frac{2 - a_0 \left[2(1 - f)\eta + (3 - 2f)\xi - \mu\right]}{a_0 - 1}$$

(2.42)

$$a_0 = \left(1 + \frac{2}{V_T} \sqrt{\frac{2(C_L + C_{GS})\Delta V_2}{\beta t_{sat}}}\right) \exp\left(\sqrt{\frac{2\beta t_{sat}\Delta V_2}{C_L + C_{GS}}}\right). \tag{2.43}$$

The asymmetry parameters  $\zeta$ ,  $\mu$ ,  $\xi$ , and  $\eta$  are defined by

$$\zeta = \Delta V_T / 2V_T,

\mu = -\Delta \beta / 2\beta,

\xi = \Delta C_L / 2C_L,

\eta = \Delta C_{GS} / 2C_{GS}.$$

(2.44)

$\Delta V_2$  is the maximum drop in the final high level signal node due to off-side conduction that will not prevent correct subsequent circuit operation. Signal node coupling capacitance was ignored. Offset and minimum overdrive contributions to sensitivity are given by:

$$v_{OS} = 2V_T \zeta + \frac{1}{f} \sqrt{\frac{2(C_L + C_{GS})\Delta V_2}{\beta t_{sat}}} \frac{a_0}{a_0 - 1},$$

(2.45)

$$v_{OD,min} = \frac{1}{f} \sqrt{\frac{2(C_L + C_{GS})\Delta V_2}{\beta t_{sat}}} \frac{4}{a_0 - 1}.$$

(2.46)

For  $2\beta t_{sat}\Delta V_2/(C_L+C_{GS})\gg 1,$  (2.42) and (2.43) reduce to

$$v_S \approx \Delta V_T + \frac{1}{f} \sqrt{\frac{2(C_L + C_{GS})\Delta V_2}{\beta t_{sat}}} \left[ (1 - f) \frac{\Delta C_{GS}}{C_{GS}} + \frac{(3 - 2f)}{2} \frac{\Delta C_L}{C_L} + \frac{1}{2} \frac{\Delta \beta}{\beta} \right]. (2.47)$$

# 2.2.3 Source-Coupled Pair Offset

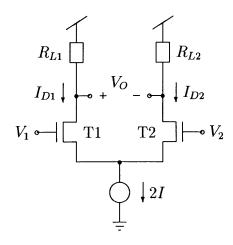

The MOS source-coupled pair is shown in Figure 2.3. The input referred dc offset voltage, defined as the differential input voltage required to make  $V_O = 0$ , is analogous to offset voltage of the cross-coupled pair. Because dc source-coupled pair offset depends only on dc circuit parameters, it is much easier to analyze than cross-coupled pair offset, which depends on  $V_S(t)$ .

Figure 2.3: Source-Coupled MOSFET Pair

Source-coupled pair performance characteristics are derived in [30]. Mismatch parameters are defined by

$$V_{1} = V_{I} + \Delta V_{I}/2, \qquad V_{2} = V_{I} - \Delta V_{I}/2,$$

$$I_{D1} = I + \Delta I_{D}/2, \qquad I_{D2} = I - \Delta I_{D}/2,$$

$$V_{T1} = V_{T} + \Delta V_{T}/2, \qquad V_{T2} = V_{T} - \Delta V_{T}/2,$$

$$\beta_{1} = \beta - \Delta \beta/2, \qquad \beta_{2} = \beta + \Delta \beta/2,$$

$$R_{L1} = R_{L} - \Delta R_{L}/2, \qquad R_{L2} = R_{L} + \Delta R_{L}/2.$$

(2.48)

The dc offset voltage is given by

$$V_{OS} = \Delta V_T + \frac{I}{G_m} \left( \frac{\Delta \beta}{\beta} + \frac{\Delta R_L}{R_L} \right). \tag{2.49}$$

The transconductance of the source coupled pair,  $G_m$ , is given by

$$G_m \equiv \left. \frac{\partial \Delta I_D}{\partial \Delta V_I} \right|_{\Delta V_I = 0} = \sqrt{2I\beta}. \tag{2.50}$$

A key source-coupled pair design parameter is the  $G_m/I$  ratio. This ratio is inversely proportional to the square root of I and is proportional to the square root of  $\beta$ . The  $\Delta\beta$  and  $\Delta R_L$  components of the offset are inversely proportional to  $G_m/I$ . Thus, source-coupled pair offset can be reduced by operating the pair at low currents and by increasing the W/L ratio of the transistors. If  $G_m/I$  is sufficiently large,  $V_{OS} \approx \Delta V_T$ .

These results suggest a tradeoff between cross-coupled pair sensing speed and sensitivity. To increase sensing speed,  $V_S(t)$  must decrease more rapidly, resulting in greater on-side and off-side currents. Higher currents imply a smaller  $G_m/I$  ratio. Thus, increasing sensing speed will likely result in greater offset.

# 2.2.4 Design Impacts

A speed versus power and sensitivity tradeoff is inherent to the cross-coupled pair. A faster latch node potential reduction increases sensing speed but also increases off-side current and reduces sensitivity.

In general, overall performance can be improved by reducing the total signal node capacitance. Signal node capacitance can be reduced by isolating the signal nodes from the bitlines during sensing. Equations (2.13) and (2.22) show that for a fixed off-side current level, reducing  $C_L$  will increase sensing speed. Equations (2.36), (2.38), (2.41), and (2.47) suggest that for a fixed sensing speed, reducing  $C_L$  will improve sensitivity.

Reducing  $C_L$  is not always beneficial. Unless  $C_L$  is large relative to  $C_C$  and  $C_{GS}$ , performance may be degraded. As  $C_L$  is reduced, the high signal potential drop due to coupling increases according to Equation (2.21). If  $C_L$  and  $(C_C + C_{GS})$  are comparable, the increase may be substantial.

Increasing device widths, W, improves amplifier performance at the expense of additional circuit area. Increasing W increases  $\beta$ . Equations (2.13) and (2.22) show that for a fixed off-side current level, increasing  $\beta$  will increase sensing speed. Equations (2.36), (2.38), (2.41), and (2.47) suggest that for a fixed sensing speed, increasing  $\beta$  will improve sensitivity. In addition, since for a given process  $\Delta W$  is likely independent of W, a larger absolute W value should produce a smaller  $\Delta W/W$  ratio, improving sensitivity.

A  $\beta$  and circuit area verses  $\Delta V_T$  and  $\Delta L/L$  tradeoff must be made in selecting device lengths. Short channels give higher  $\beta$  values and reduce circuit area. However, short channel devices exhibit a strong threshold voltage dependence on channel length due to short channel effects. In addition, a larger absolute L value should produce a smaller  $\Delta L/L$  ratio.

# Chapter 3

# Sense Amplifier Design Evolution

## 3.1 4K DRAM Generation

The 4K DRAM Generation represents the emergence of modern DRAM design. In this generation NMOS technology supplanted PMOS technology, the single transistor cell replaced the three-transistor cell, and the divided bitline architecture and balanced flip-flop sense amplifier were first employed. Mostek introduced address multiplexing, reducing package size.

#### 3.1.1 Texas Instruments

The 4K DRAM published by TI in 1973 [31] is one of the first commercial DRAMs to use the divided bitline architecture and balanced flip-flop sense amplifiers. The TI DRAM, like many other 4K DRAMs, employs a single polysilicon cell with diffused bitlines and metal wordlines. Three power supplies are required: +12 V for all circuits except the output buffer, +5 V for the output buffer, and -3 V for substrate biasing. Though each bitline segment has only 32 cells, the large bitline junction capacitance results in a sense signal of only 200 mV. The storage capacitance is approximately 100 fF and the cell area is approximately 1300 mm<sup>2</sup>.

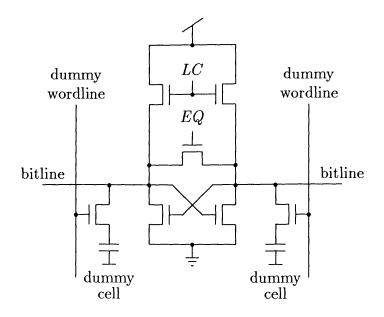

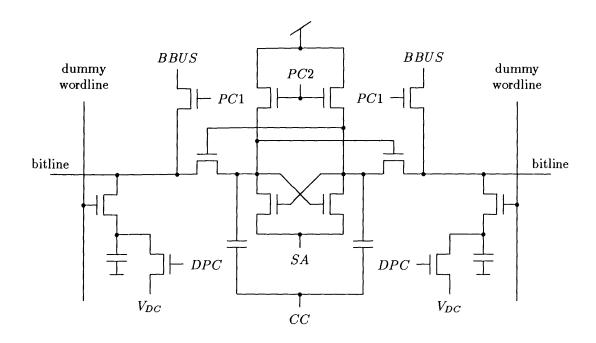

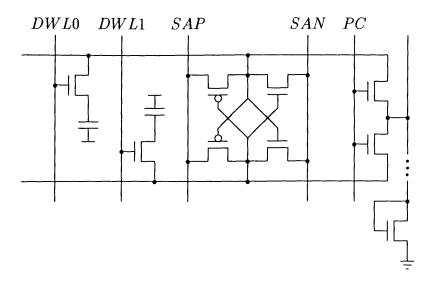

The TI 4K DRAM sense amplifier is shown in Figure 3.1. During standby the

Figure 3.1: TI 4K DRAM Sense Amplifier

load clock, LC, is low and the equalization clock, EQ, is high, shorting the two bitline segments together. The cross-coupled transistor pair pulls the segments down to +1  $V_T$  above ground. The segments may float below this potential. The dummy storage capacitors, equal in capacitance to the cell storage capacitors, are precharged to a potential approximately midway between the stored '0' and '1' voltage levels. After EQ is pulled down, the selected wordline and dummy wordlines are activated. Driving LC high turns on the load transistors, activating the flip-flop. Initially both signal node potentials rise. The difference in signal node potentials causes a difference in load currents which tends to equalize the potentials. As the signal node potentials rise above  $V_T$ , the difference in driver transistor currents increases. Amplification begins when the difference in driver transistor currents exceeds the difference in load transistor currents. Eventually, the flip-flop reaches a stable state.

The TI sense amplifier circuit requires only two clock signals, LC and EQ. These

signals carry current only when charging or discharging sense amplifier device gates. Employing clock signals to drive the sources of the cross-coupled transistors would require a substantial increase in chip area to accommodate the clock drivers.

To minimize signal loss due to load current differences, LC should have a short rise time. As the load device overdrives increase, the ratio of the current difference to the common-mode current decreases. Thus, less signal is lost as the common-mode bitline potentials increase.

Because the bitline precharge voltage is not midway between the '0' and '1' potentials, the use of dummy cells is necessary to produce reference potentials on bitline segments opposite the segments connected to the selected cells. A voltage generator provides a dummy storage capacitor precharge potential which tracks the supply voltage and the threshold voltage.

Selection of load transistor dimensions involves a tradeoff between amplifier speed and power. Load transistor currents are proportional to the W/L ratio of the devices. Higher current levels produce a faster increase in the high bitline potential. Lower currents limit dynamic and static power dissipation.

Amplifier sensitivity depends on the ratio of the driver and load transistor gain factors,  $\beta_D$  and  $\beta_L$ . The load and driver transistor current differences are proportional to  $\beta_L$  and  $\beta_D$ , respectively. Load transistor current differences work to reduce the signal. Unless  $\beta_D$  is several times larger than  $\beta_L$ , the common-mode bitline potential at which the driver transistor current difference begins to exceed the load transistor current difference will be quite large. As a result, the initial signal will be significantly reduced before amplification begins.

The final high and low bitline potentials also depend on the  $\beta_D/\beta_L$  ratio. A larger  $\beta_D/\beta_L$  ratio will give a lower final low bitline potential. As long as the final low potential is less than +1  $V_T$ , the final high potential will approach  $V_{DD} - V_T$ .

The  $\beta_D/\beta_L$  ratio can be increased either by increasing the width of the driver transistors or decreasing the W/L ratio of the load transistors. Increasing the width of the driver transistors requires additional layout area. Decreasing the W/L ratio of the load transistors reduces amplifier speed.

The low bitline precharge potential compromises sensitivity. Load transistor currents must increase the common-mode bitline potential before amplification begins. Even if the amplifier is perfectly balanced, load transistor current differences will reduce the signal. Load transistor mismatches may increase the current difference. In addition, bitline capacitance variations may increase the difference in the rate at which the bitline potentials rise. These problems are accentuated if the bitline potentials float below  $+1 V_T$  during precharge.

Because of the low bitline precharge potential, signal development is relatively fast. In the worst case, signal development begins when the wordlines reach  $+2 V_T$ . In addition, the maximum transfer device overdrive is large. Signal development would be even faster if the bitlines were precharged to ground. However, a larger increase in the common-mode bitline potential would be required to initiate signal amplification. Thus, sensitivity would be degraded.

A higher bitline precharge potential would improve sensitivity and reduce the load current required to increase the high bitline potential. However, if a higher precharge potential were employed the sources of the cross-coupled transistors could not be tied directly to ground. In addition, signal development would be slower.

# 3.1.2 Microsystems International

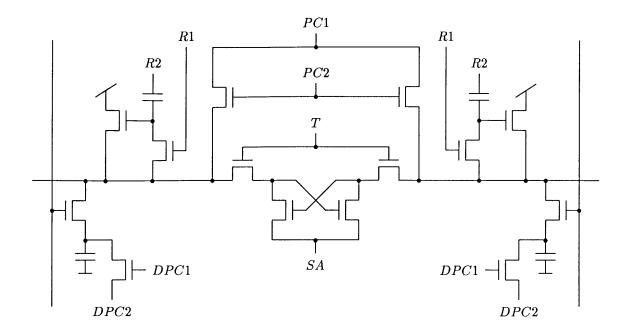

Foss and Harland published a Microsystems International 4K DRAM design in 1975 [32], [33], paying particular attention to sense amplifier design. Like the TI 4K DRAM, the Microsystems International DRAM employs a single polysilicon cell with

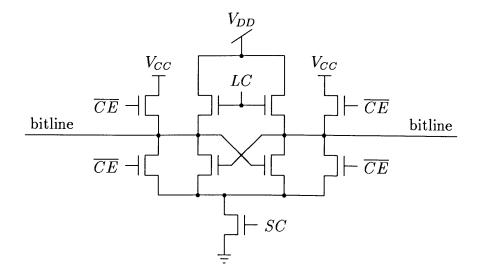

Figure 3.2: Microsystems International 4K DRAM Sense Amplifier

diffused bitlines and metal wordlines. +12 V  $V_{DD}$  and +5 V  $V_{CC}$  supplies are used. A 120 fF storage capacitance is achieved with an approximately 1250  $\mu$ m<sup>2</sup> cell area. Each bitline segment includes 32 cells, resulting in a 1 pF bitline segment capacitance. Chip area is about 13 mm<sup>2</sup>.

The sense amplifier is shown in Figure 3.2. During standby the load clock, LC, and the set clock, SC, are low.  $\overline{CE}$  is high, precharging the bitlines and the latch node to  $V_{CC}$ . A read operation begins with  $\overline{CE}$  going low. The selected wordline is activated. The potentials of bitline segments connected to cells storing a '1' increase. The potentials of segments connected to cells storing a '0' decrease. Bitline segments on the side of the sense amplifier opposite the selected wordline remain at  $V_{CC}$ .

Once signal development is complete SC rises, gradually pulling the latch node towards ground. While the higher signal node potential remains near  $V_{CC}$ , the lower node potential decreases towards ground. As the lower potential node reaches ground, LC goes high, slowly pulling the higher potential node to  $V_{DD} - V_T$ .

The sensitivity and speed of the amplifier depend on the rise time of the set clock.

A slower rise time reduces susceptibility to circuit mismatches. A faster rise time improves amplifier speed.

The column access circuits are designed to read the selected column before the high potential bitline segments are pulled up by the load transistors. As a result, chip access time is independent of load transistor operation. In addition, because the load transistors are not active during initial sensing, load transistor mismatches will not significantly degrade amplifier sensitivity.

A tradeoff must be made between cycle time and power dissipation. A larger load transistor W/L ratio reduces the time required to restore '1' cell potentials. A smaller W/L ratio reduces sense amplifier power dissipation.

The sensing scheme does not employ dummy cells. As a result, the bitline precharge potential determines the '0' and '1' signal magnitudes. Charge injected from the wordline to the selected bitline segment must be considered when choosing the precharge potential. The benefits of avoiding dummy cells include reduced chip complexity and layout area savings.

Use of the  $V_{CC}$  supply voltage for the bitline precharge potential avoids the complexity and layout area of an internal voltage generator and is convenient for signal margin testing. However, the precharge potential will not track other internal voltages and circuit parameters. As a result, the signal margin may be reduced.

Separate transistors are used to pull down each latch node. An alternative to this approach is to connect all the latch nodes together and use a single shared pull down circuit. If a shared pull down circuit is employed, sense amplifier operation is sensitive to the total current in the latch node set bus and is therefore sensitive to the stored data pattern. Use of separate transistors allows better latch node control and avoids the need for a latch node driver capable of carrying large currents. However, extra sense amplifier layout area for the latch node pull down and precharge devices

is required.

## 3.2 16K DRAM Generation

Power dissipation considerations played a key role in 16K DRAM design. Typical 4K DRAMs have only 64 sense amplifiers. In typical 16K DRAMs, 128 sense amplifiers are active during read cycles. The increase in the number of active sense amplifiers necessitated substantial reduction in power dissipation per sense amplifier.

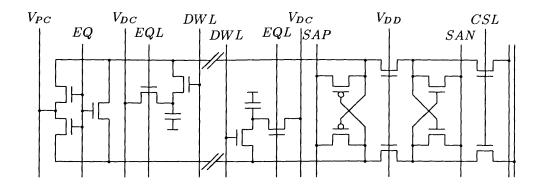

Activating static load devices during sensing results in significant off-side current. Most 16K DRAM designs precharge bitlines to  $V_{DD}$  in order to minimize, if not eliminate, activation of load devices during sensing.

### 3.2.1 Intel

The Intel 16K DRAM published in 1976 [34], [35], [36] introduced the planar, double-polysilicon cell used in most 16K DRAMs. The cell employs diffused bitlines and metal wordlines. The Intel DRAM requires three power supplies: +12 V, +5 V, and -5 V. The memory is divided into two 8K arrays. In normal operation, only one array is active, reducing power consumption. Each bitline segment serves only 32 cells. Bitline segment capacitance is 500 fF. Cell storage capacitance is 30 fF. Cell area and chip area are approximately  $455 \mu\text{m}^2$  and  $22 \text{ mm}^2$ , respectively.

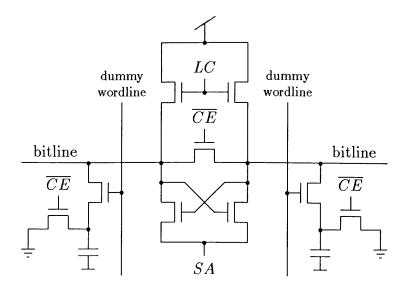

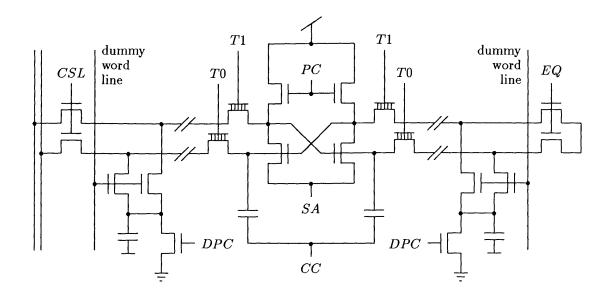

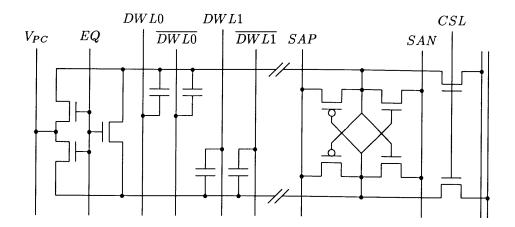

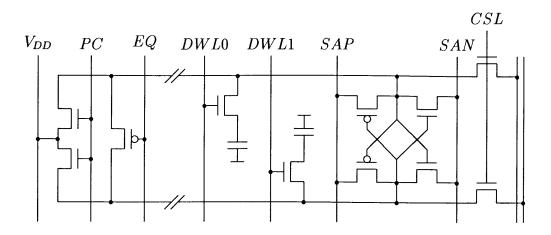

The Intel DRAM sense amplifier is shown in Figure 3.3. The dummy storage capacitance is half the ordinary cell storage capacitance. During standby, the latch node, SA, is allowed to float.  $\overline{CE}$  is high, equalizing the bitline segment potentials and precharging the dummy storage capacitors to ground. The load clock, LC, is high, precharging the bitline segments to a potential near  $V_{DD}$ .  $\overline{CE}$  and LC go low at the beginning of a read operation. When the selected wordline is activated, the dummy wordline on the opposite side of the sense amplifier is also activated. After signal development is complete, the latch node is gradually pulled down to ground,

Figure 3.3: Intel 16K DRAM Sense Amplifier

amplifying the signal. Once initial amplification is complete, LC is pulsed high, restoring the high bitline potential near  $V_{DD}$ .

The half-capacitance dummy cell technique is simple and efficient. However, differences in dummy cell and storage cell capacitances create mismatches between signal node capacitances, reducing amplifier sensitivity.

Use of clocked load devices enables active restoration of full signal levels without incurring power dissipation through the loads during primary sensing. Circuitry required to generate and drive the load clocks is shared by all sense amplifiers. Thus, with many active sense amplifiers, the price of load device clock generation per sense amplifier is fairly low.

The high bitline precharge potential has important benefits. The time and power required to pull up high potential bitline segments are minimized. In addition, load devices can be used to precharge the bitline segments, conserving layout area.

The high precharge potential results in relatively low precharge device overdrive, lengthening the interval required to precharge the bitlines. The use of a device to short the bitline segments speeds potential equalization, mitigating this disadvantage. Without an equalization device, incomplete bitline precharge would likely result in differences between bitline segment potentials, causing significant signal loss.

In the Intel DRAM, each 8K array has a common latch node, SA. As a result, independent latch node set devices need not be included in each amplifier. This saves sense amplifier area and permits more complex set clock timing.

The latch node decrease rate depends on the total capacitance seen by the driver. Until the latch node is pulled +1  $V_T$  below a bitline potential, the driver does not see the bitline capacitance. Suppose one sense amplifier is detecting a '1' and all other amplifiers are detecting a '0', the average bitline segment potential of the '1' column will be greater than that of the '0' columns. As SA falls, the '1' column sense amplifier will be activated before the '0' column sense amplifiers. Until the '0' column sense amplifiers are activated, the capacitance seen by the driver is relatively low and SA decreases rapidly. Therefore, initial sensing by the '1' column sense amplifier occurs with SA decreasing rapidly. This degrades the sensitivity of the amplifier and increases the high bitline segment potential reduction during sensing.

## 3.2.2 Mostek

The Mostek 16K DRAM, presented in 1977 [37], [38], [39] became a de facto industry standard. The DRAM employed the same double-polysilicon cell structure used by Intel. It required three power supplies: +12 V, +5 V, and -5 V. The memory consists of a single 16K array with 64 cells per bitline segment. Bitline segment capacitance is 800 fF. The 435  $\mu\text{m}^2$  cell provides a 40 fF storage capacitance. Chip area is about 20 mm<sup>2</sup>.

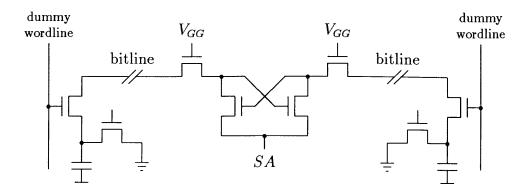

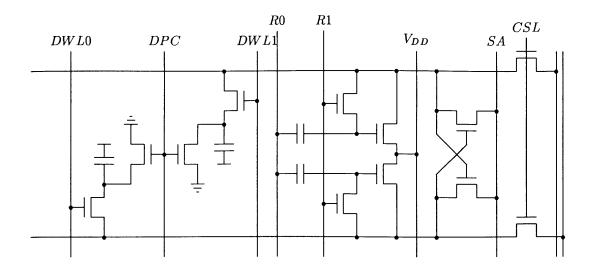

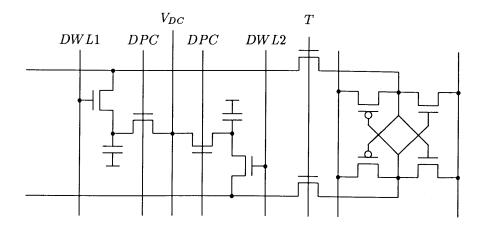

The Mostek DRAM sense amplifier, shown in Figure 3.4, introduced the use of isolation devices to partially decouple the sense amplifier signal nodes from the bitline

Figure 3.4: Mostek 16K DRAM Sense Amplifier

segments. The gates of the isolation devices are tied to an internal 16 V supply,  $V_{GG}$ .

During signal development, the bitline segment capacitance and the sense node capacitance are in series. Thus, the effective signal development time constant is small even though the isolation device resistance is substantial. During the sensing operation, the bitline segment capacitance and the isolation device resistance are in series, reducing the effective capacitance of the sense amplifier signal nodes and therefore improving amplifier speed and sensitivity.

The bitlines are precharged to  $V_{DD}$  (+12 V). Dummy storage capacitors, with half the ordinary cell capacitance, are precharged to ground. The appropriate dummy wordline is activated along with the selected wordline. After signal development is complete, the shared latch node, SA, is slowly pulled down. As the low signal node potential falls, the gate-source voltage of the isolation device separating the signal node and the bitline segment increases. As a result, the effective resistance of the device decreases, helping the sense amplifier pull the low-level bitline down.

All 16K and higher density DRAMs use address multiplexing. After the row address is received, the selected row is accessed and the sense amplifiers are activated. Later, after the column address is received, the column I/O circuitry either reads