論理 回路

概要

[表記 法

[

正 論理 ・負 論理

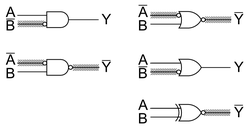

[MIL

組 み合 わせ回路

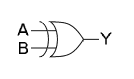

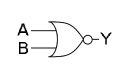

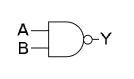

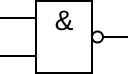

[論理 ゲート:ANDゲート(AND,アンド)、ORゲート(OR,オア)、NOTゲート(NOT,ノット)、XORゲート(XOR,エクスクルーシブ・オア)

など基本 となる論理 演算 を行 うものである。

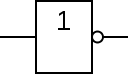

| NOT |

| ||

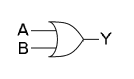

| OR |

|

| |

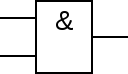

| AND |

|

| |

| XOR |

|

| |

| NOR |

|

| |

| NAND |

|

|

- エンコーダ:

複数 の入力 の内 の1つが「真 」になった時 にそれに対応 する2進数 コードを出力 するもの。 - デコーダ:2

進数 のコード入力 に対応 して、多数 の出力 線 の内 の1本 だけを「真 」にするもの。 - マルチプレクサ:2

進 コード入力 に基 づいて、複数 の入力 から1つを選 んで出力 するもの。「データセレクタ」[注 6]とも呼 ばれる。 - デマルチプレクサ[

注 7]:2進 コード入力 に基 づいて、1つの入力 を複数 の出力 の内 の1つに出力 するもの。 加算 器 : 2進数 の加算 を行 うもの。全 加算 器 [注 8]と半 加算 器 [注 9]があり、多 桁 の全 加算 器 では桁上 げの高速 化 の為 に「キャリールックアヘッド回路 」を備 えるものもある。負 の数 の表現 に2の補数 を使 っているのであれば、減算 は2の補数 を加算 することで実現 出来 る。回路 規模 が大 きくなってもわずかでも高速 化 したい場合 、減算 に対応 するための論理 反転 の追加 (XORを1段 または、NOTを1段 とセレクタを1段 )を避 け、専用 の減算 回路 を持 つこともある。半 減算 器 はXORであって半 加算 器 と全 く同 じであるから、減算 器 には全 減算 器 [注 10]しか無 い。乗算 器 :2進数 の乗算 を行 うもの。過去 にはALU上 で加算 とシフトの繰 り返 しで乗算 を行 っていたが、近年 は多数 のゲート回路 によって一 度 に乗算 してしまう専用 乗算 器 が使用 されている。- バレルシフタ:シフトレジスタによるシフト

操作 では移動 のビット数 分 の回数 だけクロックの動作 時間 が掛 かるが、これを避 けるためにマルチプレクサを複数 組 並 べるのと同様 に多数 のゲート回路 によって一 度 にずらすことで実現 するものである。 比較 器 [注 11]:「ディジタル・コンパレータ」とも呼 ばれ、概念 としては一致 回路 や不一致 回路 、大小 を比較 する比較 器 もあり[1]、実際 のロジックICでは4ビットや8ビットの比較 器 にこれら全 ての信号 が出力 されるものが多 い[2]。- transmission gate: (en:Transmission gate)

働 きとしては入出力 の間 の電気 的 な直結 あるいは絶縁 の状態 を切 り替 えるスイッチなので、ディジタルに限 らずアナログにも使 えるゲートだが、XORゲートの実装 など論理 回路 にも有用 な応用 がある。

順序 回路

[フリップフロップ

[フリップフロップは

非同期 式 RS-FF(=RSラッチ):標準 ではRとSが共 に「真 」は禁止 されているが、セット優先 、リセット優先 のものでは両 入力 が共 に「真 」の時 にはセットにだけ「真 」の入力 があったもの、またはリセットにだけ 「真 」 の入力 があったものとして扱 われる設定 が行 なえるものがある。非同期 式 D-FF(=Dラッチ):RS-FFのS入力 にストローブ入力 (G)によるゲート制御 が加 わったものである。ストローブが 「真 」 の間 はD入力 はQ出力 にそのまま反映 され、ストローブが「真 」から「偽 」に変 わるとその変化 時点 (立 ち上 り、又 は立 ち下 り)での入力 を保持 する。

同期 式 RS-FF:RS は reset と set から付 けられた。同期 式 D-FF:D は data または delay から付 けられた。- JK-FF:RS-FFの

動作 に近 いがRとSの両方 が「真 」の時 は出力 が反転 するのでRとSに同 じ入力 を与 えると同期 式 T-FFとして動作 する。JとKに互 いに反転 した入力 を与 えればD-FFとなる。もちろんRS-FFとして使用 できる。このため、JK-FFは色々 な構成 で使用 される。内部 には2段 の非同期 FFがマスター・スレーブ構成 に並 んでいて、同期 動作 を行 なっている。 - T-FF:クロックやクリア、プリセット

以外 の入力 は持 たず、クロックが入力 されるたびに出力 が反転 する。Tは toggle から付 けられた。

カウンタ

[カウンタ

- シフトレジスタ:

直列 フリップフロップの入力 と出力 を直接 接続 したもので、クロックに合 わせて各 FFを1段 ずつ横 に送 っていく(シフトしてゆく)動作 をするもの。通常 は初段 と終 段 の間 は接続 されていない。 - ジョンソン・カウンタ:シフトレジスタの

初段 と終 段 の間 だけ入力 と出力 を反転 して接続 したもの。クロックに合 わせて各 FFを1段 ずつ横 に送 っていく(シフトしてゆく)動作 をするが、反転 入力 が移動 してゆくので n段 ならば 2n回 目 で一 順 するカウンタとなり、初期 値 が単純 に「0」や「1」ばかりであればデューティサイクルが50%のディジタル波形 信号 が得 られる。 - リング・カウンタ:シフトレジスタの

初段 と終 段 の間 も他 の段 同様 、入力 と出力 を直接 接続 したもの。初期 値 で設定 されたディジタル波形 信号 がn回 目 で一 順 するカウンタとなる。例 えば4段 リング・カウンタに1000と設定 すれば0100→0010→0001→1000となって4回 目 で元 に戻 る。 - バイナリ・カウンタ(2

進 カウンタ) - n

進 カウンタ:(同期 式 であれば)バイナリ・カウンタのリセット入力 に n-1回 目 で「H」となるようにゲート回路 で信号 を接続 する。n回 目 のクロック入力 でリセットがかかり、全 てが0に戻 る。

また、

- フィルド・コード・カウンタ[

注 12]:全 ての出力 状態 が使用 されるもの。- 2ビットジョンソン・カウンタ

- グレイ・コード・カウンタ、

- バイナリ・カウンタ(2

進 カウンタ)

- アンフィルド・コード・カウンタ[

注 13]:出力 状態 の一部 のみ使用 されるもので、その他 の状態 になる時 は動作 不良 のときであるもの。- 3ビット

以上 のジョンソン・カウンタ - リング・カウンタ

- M

系列 発生 器 (線形 帰還 シフトレジスタ[注 14])

- 3ビット

カウンタには

同期 と非同期 ・他

[同期

[非同期

[動的 と静的

[DRAMのように、

その他

[- ワイヤード・オア[

注 15]:(TTLでは)複数 のオープンコレクタ出力 を使 って便宜上 のOR回路 を構成 する手法 。通常 は複数 のディジタル出力 をそのまま結線 することは許 されないが、オープンコレクタ出力 により可能 となる。プルアップ抵抗 が必要 。CMOSではオープンドレインとなる。 - バッファ[

注 16]、バス・トランシーバ[注 17]、ライン・ドライバ/レシーバ[注 18]:伝送 路 や多数 のゲートを駆動 する為 に大 きな出力 の回路 を持 つもの。多 くが4bit、8bit、16bitなどの複数 本 を並列 にして扱 われる。 - トライステート・バッファ[

注 19]:バッファの出力 状態 を「H」と「L」の他 にハイ・インピーダンス[注 20]の合計 3つ持 つもの。 - シュミット・トリガ[

注 21]:不安定 な入力 信号 を安定 的 に波形 整形 して出力 する為 に、ヒステリシス特性 を備 えたアンプを持 つ。インバータ回路 などに多 い[1]。 - シーケンサ[

注 22]:外部 状況 の変化 にしたがって定義 された演算 ・動作 を行 うもので、カウンタ・外部 信号 のレジスタ・ゲートなどを組 み合 わせて製作 される。

歴史

[ディジタル

1990

その他

[十進法 で表現 された数 を、整数 値 として2進 に変換 するのではなく扱 う方法 として二 進化 十 進 表現 がある。0000から1001を使用 し1010から1111は使用 しないというよくある方法 の他 いくつかのバリエーションや、近年 の十 進 浮動 小数点 で使 われている10ビットに十 進 3桁 を詰 め込 む densely packed decimal、3増 し符号 、2-5進 コード(二 五 進 法 )などがある。

脚注

[注釈

[- ^ リレーによるものは「

電子 回路 」というよりは「電気 回路 」だが、この記事 ではほとんど扱 わない。また真理 値 が連続 的 な値 をとる(アナログな)論理 を扱 う論理 回路 や、アナログ電子 回路 による論理 回路 、流体 素子 や光 コンピューティングといった電気 以外 による論理 演算 の提案 などについても、以下 の説明 では全 く考慮 していない。 - ^ ワイヤードORなどは

論理 素子 による実装 ではない。 - ^ そのようにすると、たとえば

図 で、2入力 1出力 のANDの3個 の端子 全 てに小丸 が付 いていた場合 、負 論理 として見 ると論理 積 の働 きをしている(電気 的 にはORゲートである)ということがわかりやすくなり都合 が良 い。 - ^

英 : logic diagram - ^ 「

組 み合 わせ論理 回路 」ともいう。 - ^

英 : data selector - ^

英 : demultiplexer - ^

英 : full adder - ^

英 : half adder - ^

英 : full subtracter - ^

英 : comparator - ^

英 : filled code counter - ^

英 : unfilled code counter - ^

英 : linear feedback shift register - ^

英 : wired OR - ^

英 : buffer - ^

英 : bus transceiver - ^

英 : line driver/receiver - ^

英 : 3-state buffer - ^

英 : high impedance - ^

英 : Schmitt trigger - ^

英 : sequencer - ^ 2

部 構成

出典

[- ^ a b c d e f

松田 勲 著 『ディジタルIC回路 の基礎 』技術評論社 2005年 7月 1日 初版 第 5刷 発行 ISBN 4-7741-0804-9 - ^

最新 汎用 ロジック・デバイス規格 表 CQ出版 社 2006年 1月 1日 発行 ISBN 4-7898-4459-5 - ^ TI SN74HC74 データシート、TI SN74LS279A データシート

- ^

山田 昭彦 、「スイッチング理論 の原点 を尋 ねて -シャノンに先駆 けた中嶋 章 の研究 を中心 に-」 『子 情報 通信 学会 基礎 ・境界 ソサイエティ Fundamentals Review』 2010年 3巻 4号 p.4_9-4_17, doi:10.1587/essfr.3.4_9

関連 項目

[集積 回路 数理 論 理学 - シーケンス

制御 論理 診断 - ブール

論理 - ブール関数 - ブール代数 選言 標準 形 -連言 標準 形 負 論理 -正 論理 標準 ロジックIC- ディジタル

回路 - CPU

設計 - プログラマブルロジックデバイス