NEC PowerVR PCX

Die PowerVR PCX Serie von NEC ist eine Familie von 3D-Grafikchips für den PCI-Bus, die auf IP der PowerVR Series 1 basieren und somit Tilebased Deferred Renderer (TBDR) sind. Die PowerVR PCX Serie wurde in Zusammenarbeit mit VideoLogic entwickelt.

Versionen

[Bearbeiten | Quelltext bearbeiten]PowerVR PCX1

[Bearbeiten | Quelltext bearbeiten]

PowerVR PCX1 (4 MB Textur-Speicher)

Der NEC PowerVR PCX1 war der allererste Grafikchip mit PowerVR-Technik (Series 1) und kam im Oktober 1996 als 3D-Zusatzkarte in etwa zeitgleich mit dem Voodoo Graphics-Chip von 3dfx auf dem Markt. Entwickelt und produziert wurde der Chip von NEC. Der Chip war in etwa ebenbürtig mit dem Voodoo 1, hatte aber durch den architekturbedingt fehlenden Z-Buffer heftige Probleme in Direct3D und konnte sich nicht gegen den Voodoo 1 durchsetzen. Zudem konnte sich die herstellereigene PowerSGL-Schnittstelle im Gegensatz zu 3dfx’ Glide nicht durchsetzen.

Als Besonderheit ist anzumerken, dass diese PowerVR-Serie ihren RAM ausschließlich für Texturen verwendet. Die Karten hatten keinen VGA-Ausgang, sondern schrieben die 3D-Szenen über den PCI-Bus direkt in den RAM der Hauptgrafikkarte. Deren Speicher wurde also mitbenutzt und war dadurch mit seiner Taktung geschwindigkeitsbeeinflussend. Dessen Größe bestimmte so auch die möglichen Auflösungen, wobei die PCX-Karten bis zu 1024 × 768 spielbar bereitstellten – 1996 ein auf Jahre bestehendes Alleinstellungsmerkmal. Abschließend bestimmte die Haupt-Karte noch die Signalqualität des Bildes, im Kontrast zum Voodoo-Verfahren, bei dem es die 3D-Karte war.

Der PCX1 nutzte als erster PC-Grafikprozessor mit dem „Infinite Planes“-Verfahren ein bandbreitenschonendes Vorgehen, indem er nur die nicht verdeckten 3D-Objekte einer Szene berechnete. Damit legte er den Grundstein für eine besondere Charakteristik der PowerVR-Grafikserien, dem Tilebased Deferred Renderering (TBDR). Erst hierdurch war es dem Chip möglich, trotz seines sehr schmalen 32-Bit-Speicheranschlusses eine der 3dfx Voodoo 1 (64-Bit-Speicheranbindung) vergleichbare Geschwindigkeit zu erzielen.

Dennoch war dieser Chip gleichzeitig wohl der erste 3D-Chip, der mit möglichen Tricks zum Erzielen hoher 3D-Benchmarkwerte auffiel. Hierzu erkannte der Treiber den D3D-Test von Microsoft,[1] und berechnete diesen weniger genau, aber deutlich schneller.[2] Erst Jahre später wurde ähnliches bei nVidia-GPUs bekannt (vgl. Nvidia GeForce).

Eine bekannte Grafikkarte mit diesem Chip war die VideoLogic Apocalypse 3D.

PowerVR PCX2

[Bearbeiten | Quelltext bearbeiten]

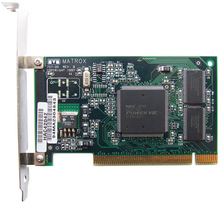

PowerVR PCX2 (4 MB Textur-Speicher)

Im August 1997 legte NEC dann den PowerVR PCX2 nach, der einige Detailverbesserungen wie bilineare Filterung und Gleitkomma-Formatierung[3] gegenüber dem PCX1 enthielt. Hierdurch gewann die Bildqualität und der Prozessor wurde entlastet. Dennoch schloss dieser Chip erst bei Pentium-II-Prozessoren zu Voodoo Graphics-basierten Beschleunigern auf[4]. Der Grund lag in seiner Architektur.

Wie alle Chips dieser Zeit müssen beide PCX' die Direct3D-Befehle im Treiber auf ihre interne Rendereinheit adaptieren, eine durch das Fehlen des Z-Buffers hier aber grundverschiedene. Einzig der Nvidia Riva war bereits in Hardware für Direct3D entworfen worden, was eine Reaktion auf seine dazu gänzlich inkompatible Vorgängerarchitektur war. Die Umwandlung ist systembedingt eine Prozessoraufgabe. Somit war der Rechenaufwand in PowerVR-Systemen höher als bei der Konkurrenz. Hinzu kam der Zusatzaufwand der Szenerie-Aufteilung in die namensgebenden Tiles. Erst die PowerVR Series 2 übernahm dieses Tiling mitsamt der Verwaltung der enthaltenen Polygone (in einer „Display List“) vom Prozessor.[5]

Die Tiles werden nach Erstellung einzeln zum Chip gesendet, welcher dieses in einem 12 Kilobyte großen Cache von den nicht sichtbaren Polygonen befreit. Von diesem ISP (Image Synthesis Processor) wandert die Bildkachel nun zum im selben Gehäuse befindlichen TSP (Texture and Shading Processor), der die Oberflächen der verbliebenen Polygone zeichnet und beleuchtet. Hierzu kombiniert er deren Eckdaten aus seinem 4 KB Parametercache mit den Texturen im Kartenspeicher und schreibt das Ergebnis in den Framebuffer der Haupt-Grafikkarte. Gespart werden so der Z-Buffer im chipexternen Speicher sowie die vielfachen Zugriffe darauf, ebenso das Vorhalten und Verarbeiten letztlich verdeckter Texturen.[6] Zunächst wurde so aber noch der enorme Bandbreitenvorteil gegen einen starken Prozessorbezug getauscht, sobald ein Spiel keine PowerSGL-Unterstützung anbot.

3Dfx lag mit seiner Architektur sehr nah am damals ebenfalls vielversprechenden Standard OpenGL, welcher dem noch sehr neuen DirectX in Reife und Funktionalität überlegen war. Diese Nähe minimierte für 3Dfx den Aufwand für ein Übersetzungsprogramm (MiniGL-Wrapper). Ein solches wandelt nach dem Schema des Direct3D-Treibers die wichtigsten OpenGL-Befehle der Anwendung in für den Chip kompatible Daten. 3Dfx orientierte sich dabei am Umfang des vom Spiel Quake benötigten Befehlssatzes (dies führte auch zur Bezeichnung „QuakeGL“). Um mit seinem MiniGL-Wrapper bei der abermals auch OpenGL-fernen Architektur noch vergleichbare Leistungswerte zu erzielen, verwarf der PowerVR-Treiber behelfsweise alle Beleuchtungseffekte.[7]

Ähnlich dem damaligen Konkurrenten 3dfx Voodoo Rush erschien auch mit dem PCX2 eine kombinierte 2D/3D-Karte, die Videologic Apocalypse 5D. Auch hier verwendete man aufgrund fehlender 2D-Kompetenz einen Zulieferchip. Diesen stellte Tseng Labs zunächst mit dem ET-6000 und später dessen Nachfolger ET-6100. Da 2D- und 3D-Chip unterschiedliche Speicherarten verwendeten, erhöhte dies die Zahl der verwendeten Bauteile – der resultierende Preis trug zum fehlenden Markterfolg bei. Um diesen systembedingten Nachteil auszugleichen, erschien später noch eine „Sonic“-Version mit dem Zusatz eines ESS-Maestro-1-Soundchips.

Anders als der Voodoo Rush hatten diese Karten durch ihre separaten Bildspeicher keine Performancenachteile gegenüber der reinen 3D-Version.

Die einzigen Addon-3D-Karten mit diesem Chip waren die VideoLogic Apocalypse 3Dx und die Matrox m3D.

Basierend auf diesem Chip ergänzte Videologic (mittlerweile umbenannt in Imagination Technologies) eine vierfache Texturkompression und steigerte in Zusammenarbeit mit NEC den Takt auf 100 MHz bei 250 nm Strukturbreite, um den Grafikchip PowerVR2DC (CLX2) für die Sega Dreamcast, NAOMI und Naomi 2 zu liefern.[8] Dessen PC-Variante NEC Neon 250 erschien erheblich verspätet erst Ende 1999, dafür mit 25 MHz höherer Taktrate.

Modelldaten

[Bearbeiten | Quelltext bearbeiten]| Model | Launch | Code- name[9] |

Herstellungs- verfahren |

Transi- storen in Mio. |

Schnitt- stelle |

max. Speicher in MB |

Takt (Chip) in MHz |

Takt (Speicher) in MHz |

RenderPipes x TMU × VPU |

Füllrate in MT/s |

Speicher- bandbreite in GB/s |

Speicher- Typ |

Speicher- busbreite |

DirectX / OpenGL- Version |

Features |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PowerVR PCX1 | 1996 | Midas 4 | 0,5 µm | 0,6 | PCI | 4 | 60 | 60 | 1x1×0 | bis 60 | 0,24 | SDRAM | 32 bit | 3 / - (MiniGL- Wrapper) |

TBDR, PowerSGL, RenderWare |

| PowerVR PCX2 | 1997 | Midas 5 | 0,35 µm | 1,2 | 4 | 66 | 66 | bis 66 | 0,26 |

- Die Füllrate ist abhängig von Prozessor und Hauptgrafikkarte.

Siehe auch

[Bearbeiten | Quelltext bearbeiten]Weblinks

[Bearbeiten | Quelltext bearbeiten]Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ mdgx.com Microsoft D3DTest

- ↑ Georg Schnurer: Tricky. In: c’t Magazin / heise online. 12. März 1997, abgerufen am 13. Oktober 2022 (Apocalypse 3D – 3D Benchmarktrick).

- ↑ pure.com. Ehemals im (nicht mehr online verfügbar); abgerufen am 2. August 2009 (Verbesserungen des PCX2). (Seite nicht mehr abrufbar. Suche in Webarchiven)

- ↑ geocities.com ( vom 25. Januar 2008 im Internet Archive)

- ↑ wave-report.com Polygonsetup und Tiling wandern in der zweiten Serie vom Prozessor zum Grafikchip

- ↑ stason.org PCX1-Spezifikationen

- ↑ Thomas Pabst: 3D Accelerator Review Step One – 3D Performance, the Real Deal. In: Tom’s Hardware. 21. Januar 1998, abgerufen am 13. Oktober 2022.

- ↑ the-nextlevel.com PowerVR2DC

- ↑ Codenamen laut PowerVR. Ehemals im (nicht mehr online verfügbar); abgerufen am 2. August 2009. (Seite nicht mehr abrufbar. Suche in Webarchiven)