Zilog Z8: Difference between revisions

No edit summary |

Em3rgent0rdr (talk | contribs) SPI is not included in original. Only in select (newer models). Added note on this, and converted other reference notes into more appropriate {{NoteTag}}. |

||

| (29 intermediate revisions by 20 users not shown) | |||

| Line 1: | Line 1: | ||

{{ |

{{More citations needed|date=July 2009}} |

||

[[ |

[[File:KL Zilog Z8.jpg|thumb|right|Zilog Z8 processor]] |

||

[[ |

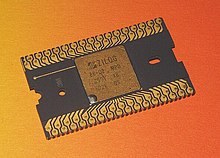

[[File:KL Zilog Z8 Super-8.jpg|thumb|Zilog Z8 (Super-8 family)]] |

||

[[File:Zilog Z8 02 1.jpg|thumb|A Zilog Z8-02 packaged in a [[Quad in-line package|QUIP]]]] |

|||

The '''[[Zilog]] Z8''' is a [[microcontroller]] architecture, originally introduced in 1979, which today also includes the '''eZ8 Encore!''' |

The '''[[Zilog]] Z8''' is a [[microcontroller]] architecture, originally introduced in 1979, which today also includes the '''[[Z8 Encore!]]''', '''eZ8 Encore!''',{{NoteTag|''The "Encore!" products contains the newer eZ8 core which is 2-3 times as clock cycle efficient as the original Z8 core.''}} '''eZ8 Encore! XP''', and '''eZ8 Encore! MC''' families. |

||

Signifying features of the architecture are up to 4,096 fast on-chip registers which may be used as accumulators, pointers, or as ordinary [[ |

Signifying features of the architecture are up to 4,096 fast on-chip registers which may be used as accumulators, pointers, or as ordinary [[random-access memory]] (RAM). A [[16-bit]] address space for between 1 [[kibibyte]] (KB) and 64 KB of either [[programmable read-only memory]] (PROM, OTP), [[read-only memory]] (ROM), or [[flash memory]], are used to store code and constants, and there is a second 16-bit address space which can be used for large applications. |

||

On chip [[peripheral]]s include [[ |

On chip [[peripheral]]s include [[analog-to-digital converter]] (A/D), [[Serial Peripheral Interface]] (SPI){{NoteTag|http://bitsavers.trailing-edge.com/components/zilog/z8/UM001602-0904_Z8_User_Manual_2004.pdf says SPI is only in select models. 1983 manual has no mention of an SPI: https://archive.org/details/bitsavers_zilogz8198hnicalManual_4348606}} and Inter-Integrated Circuit ([[I²C]]) channels, [[IrDA]] encoders/decoders etc. There are versions with from 8 up to 80 pins, housed in [[dual in-line package]] (PDIP), [[Quad Flat No-leads package]] (MicroLeadFrame, MLF), [[small outline integrated circuit]] (SOIC), Shrink Small-Outline Package (SSOP), and low profile [[Quad Flat Package]] (LQFP). The eZ8 Encore! series can be programmed and debugged through a single pin [[serial communication]] interface. |

||

The basic architecture, a modified (non-strict) [[Harvard architecture]], is ''technically'' very different from the [[Zilog Z80]]. Despite this, the [[instruction set]] and assembly [[syntax]] are quite similar to other Zilog processors: Load/store operations |

The basic architecture, a modified (non-strict) [[Harvard architecture]], is ''technically'' very different from the [[Zilog Z80]]. Despite this, the [[instruction set]] and [[assembly language]] [[syntax]] are quite similar to other Zilog processors: Load/store operations use the same <code>LD</code> mnemonic (no <code>MOV</code> or <code>MOVE</code>s), typifying instructions such as <code>DJNZ</code>, are the same, and so on. |

||

An [[integrated development environment]] (IDE) named Zilog Developer's Studio (ZDS) can be downloaded from Zilog's website including an assembler. The edition of ZDS II targeting Z8 Encore! and newer derivatives also includes a free compiler claiming ANSI C89 compliance. |

|||

A gratis C compiler and IDE can be downloaded from Zilog's website. |

|||

Primary competitors include the somewhat similar |

Primary competitors include the somewhat similar{{NoteTag|''The PIC and the 8051 are using Harvard architectures as well, but in a more rigid manner.''}} [[Microchip Technology]] [[PIC microcontroller|PIC]] family, and all [[Intel 8051]] descendants. Also more traditional ''[[von Neumann architecture]] based'' single chip [[microcontroller]]s may be regarded as competitors, such as the [[Motorola 6800]], [[Motorola 6809|6809]] based [[Motorola 68HC11]], the [[Hitachi H8]] family, and [[Z80]]-derivatives, such as [[Toshiba]] TLCS-870, to name only a few. |

||

==Product line== |

==Product line== |

||

*ROMless: Models without integrated ROM |

*ROMless: Models without integrated ROM |

||

*ROM: Models with integrated ROM |

*ROM: Models with integrated ROM |

||

*BASIC: Models with integrated BASIC interpreter and debugger in ROM |

*BASIC: Models with integrated BASIC interpreter and debugger in ROM |

||

*OTP: Models with integrated [[ |

*OTP: Models with integrated [[programmable read-only memory]] (OTP ROM) |

||

*Low Voltage: Working voltage run as low as 2V |

*Low Voltage: Working voltage run as low as 2V |

||

*GP: General purpose microcontroller |

*GP: General purpose microcontroller |

||

*Encore!: Integrated flash-based memory |

*Encore!: Integrated flash-based memory |

||

*Encore! XP: Encore! with sensors |

*Encore! XP: Encore! with sensors |

||

*Encore! MC (Motor Control): Motor control applications |

*Encore! MC (Motor Control): Motor control applications |

||

==Emulators== |

|||

JTCEMU is a free software ([[GNU General Public License]] (GPL) version 3) Z8 emulator written in [[Java (programming language)|Java]] for [[Linux]], [[Windows]], and [[macOS]].<ref>{{Cite web |url=http://www.jens-mueller.org/jtcemu/ |title=JTCEMU: JU+TE-Computer-Emulator |last=Müller |first=Jens |date=26 July 2011 |website=Jens Müller's homepage |access-date=2020-03-30}}</ref> |

|||

==Second sources== |

|||

<gallery caption="Zilog Z8 [[second source]]s" mode="packed"> |

|||

Robotron UC8810D 004 1.jpg|VEB [[Kombinat Mikroelektronik Erfurt]] ''Karl Marx'' (MME) UC8810D (mask ROM version) |

|||

Synertek Z8 03RS 1.jpg|[[Synertek]] Z8-03RS (piggy-back EPROM version) |

|||

</gallery> |

|||

==Notes== |

==Notes== |

||

{{ |

{{NoteFoot}} |

||

==References== |

==References== |

||

{{Reflist}} |

|||

* Grehan, Rick (September 1994). "Processors Proliferate". ''[[Byte (magazine)|Byte]]''. |

* Grehan, Rick (September 1994). "Processors Proliferate". ''[[Byte (magazine)|Byte]]''. |

||

== External links == |

== External links == |

||

* {{Official website|www.zilog.com}} |

|||

* [http://www.zilog.com/index.php?option=com_content&task=view&id=56&businessLine=1&parent_id=2&Itemid=184 Official page about Z8 Encore! Product Family ] |

|||

{{ |

{{Zilog}} |

||

{{Microcontrollers}} |

|||

{{8bitMCUs}} |

|||

[[Category:Microcontrollers]] |

[[Category:Microcontrollers]] |

||

[[Category:Zilog microprocessors]] |

|||

[[de:Zilog Z8]] |

|||

[[ja:Z8 (コントローラ)]] |

|||

[[pl:Zilog Z8]] |

|||

[[sv:Zilog Z8]] |

|||

Latest revision as of 16:46, 5 August 2023

This article needs additional citations for verification. (July 2009) |

The Zilog Z8 is a microcontroller architecture, originally introduced in 1979, which today also includes the Z8 Encore!, eZ8 Encore!,[note 1] eZ8 Encore! XP, and eZ8 Encore! MC families.

Signifying features of the architecture are up to 4,096 fast on-chip registers which may be used as accumulators, pointers, or as ordinary random-access memory (RAM). A 16-bit address space for between 1 kibibyte (KB) and 64 KB of either programmable read-only memory (PROM, OTP), read-only memory (ROM), or flash memory, are used to store code and constants, and there is a second 16-bit address space which can be used for large applications.

On chip peripherals include analog-to-digital converter (A/D), Serial Peripheral Interface (SPI)[note 2] and Inter-Integrated Circuit (I²C) channels, IrDA encoders/decoders etc. There are versions with from 8 up to 80 pins, housed in dual in-line package (PDIP), Quad Flat No-leads package (MicroLeadFrame, MLF), small outline integrated circuit (SOIC), Shrink Small-Outline Package (SSOP), and low profile Quad Flat Package (LQFP). The eZ8 Encore! series can be programmed and debugged through a single pin serial communication interface.

The basic architecture, a modified (non-strict) Harvard architecture, is technically very different from the Zilog Z80. Despite this, the instruction set and assembly language syntax are quite similar to other Zilog processors: Load/store operations use the same LD mnemonic (no MOV or MOVEs), typifying instructions such as DJNZ, are the same, and so on.

An integrated development environment (IDE) named Zilog Developer's Studio (ZDS) can be downloaded from Zilog's website including an assembler. The edition of ZDS II targeting Z8 Encore! and newer derivatives also includes a free compiler claiming ANSI C89 compliance.

Primary competitors include the somewhat similar[note 3] Microchip Technology PIC family, and all Intel 8051 descendants. Also more traditional von Neumann architecture based single chip microcontrollers may be regarded as competitors, such as the Motorola 6800, 6809 based Motorola 68HC11, the Hitachi H8 family, and Z80-derivatives, such as Toshiba TLCS-870, to name only a few.

Product line

[edit]- ROMless: Models without integrated ROM

- ROM: Models with integrated ROM

- BASIC: Models with integrated BASIC interpreter and debugger in ROM

- OTP: Models with integrated programmable read-only memory (OTP ROM)

- Low Voltage: Working voltage run as low as 2V

- GP: General purpose microcontroller

- Encore!: Integrated flash-based memory

- Encore! XP: Encore! with sensors

- Encore! MC (Motor Control): Motor control applications

Emulators

[edit]JTCEMU is a free software (GNU General Public License (GPL) version 3) Z8 emulator written in Java for Linux, Windows, and macOS.[1]

Second sources

[edit]- Zilog Z8 second sources

-

VEB Kombinat Mikroelektronik Erfurt Karl Marx (MME) UC8810D (mask ROM version)

-

Synertek Z8-03RS (piggy-back EPROM version)

Notes

[edit]- ^ The "Encore!" products contains the newer eZ8 core which is 2-3 times as clock cycle efficient as the original Z8 core.

- ^ http://bitsavers.trailing-edge.com/components/zilog/z8/UM001602-0904_Z8_User_Manual_2004.pdf says SPI is only in select models. 1983 manual has no mention of an SPI: https://archive.org/details/bitsavers_zilogz8198hnicalManual_4348606

- ^ The PIC and the 8051 are using Harvard architectures as well, but in a more rigid manner.

References

[edit]- ^ Müller, Jens (26 July 2011). "JTCEMU: JU+TE-Computer-Emulator". Jens Müller's homepage. Retrieved 2020-03-30.

- Grehan, Rick (September 1994). "Processors Proliferate". Byte.