IA-32

IA-32 (Intel Architecture 32 bit) – 32-bitowy model programowy mikroprocesora opracowany przez firmę Intel. Nazywany również x86-32, jako że opiera się na 32-bitowym rozwinięciu modelu programowego rodziny x86. Architektura IA-32 zaliczana jest z reguły do kategorii CISC, choć technologie wprowadzane stopniowo w nowszych wersjach procesorów IA-32 spełniają także wiele cech procesorów RISC.

Model IA-32 został wprowadzony w 1985 roku, wraz z procesorem Intel 80386 i jest najpopularniejszym modelem architektury stosowanym w komputerach ogólnego przeznaczenia (tzn. komputerach osobistych, serwerach). Stopniowo jest wypierany przez model 64-bitowy AMD64, Intel 64 (EM64T), czyli tzw. x86-64.

Tryby pracy

[edytuj | edytuj kod]Procesory IA-32 posiadają trzy podstawowe tryby pracy, określające m.in. sposób zarządzania pamięcią i uprawnienia użytkownika.

- Tryb rzeczywisty – tryb zgodny z najstarszymi procesorami rodziny x86 z Intel 8086 włącznie. W trybie tym występuje segmentacja pamięci, rozmiar segmentu jest stały i wynosi 64 KB. Przestrzeń adresowa ograniczona jest do 1 MB, do adresowania wykorzystuje się rejestry segmentowe oraz offset. W trybie tym współczesne procesory pracują jedynie od chwili uruchomienia do przekazania kontroli systemowi operacyjnemu.

- Tryb chroniony – tryb inicjalizowany i w znacznej mierze kontrolowany przez system operacyjny. Pamięć może być zorganizowana w segmenty dowolnej wielkości, fizyczna przestrzeń adresowa ograniczona jest z reguły do 64 GB, liniowa przestrzeń adresowa do 4 GB. Rodzaj adresowania zależy od systemu operacyjnego – może być stosowany tzw. model płaski (bez segmentacji), model z segmentacją analogiczną do trybu rzeczywistego lub – najczęściej – adresowanie nieliniowe (tzw. logiczne). W adresowaniu nieliniowym adres fizyczny jest zależny od wpisu w systemowej tablicy deskryptorów, na który wskazuje selektor. W trybie chronionym procesor obsługuje wielozadaniowość, chroni przed nieupoważnionym dostępem do urządzeń wejścia/wyjścia.

- Tryb wirtualny V86 – odmiana trybu chronionego, która jest symulacją trybu rzeczywistego. Służy np. do uruchamiania programów MS-DOS.

- Tryb SMM (System Management Mode) – jest to tryb przeznaczony do zarządzania sprzętem przez systemy operacyjne, niedostępny z poziomu użytkownika.

Rejestry

[edytuj | edytuj kod]

Rejestry ogólnego przeznaczenia

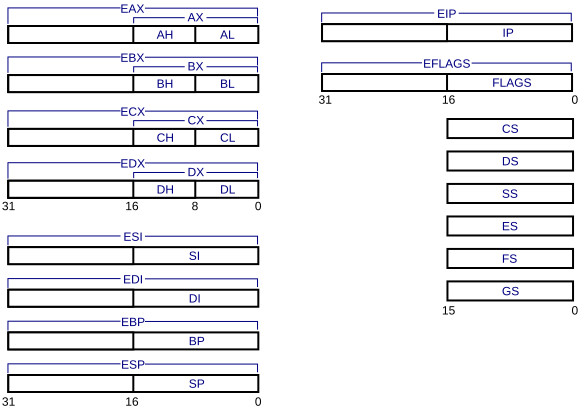

[edytuj | edytuj kod]W procesorach opartych na modelu IA-32 dostępne jest osiem 32-bitowych rejestrów ogólnego przeznaczenia:

- Rejestry danych

- EAX – rejestr akumulacji

- EBX – rejestr bazowy

- ECX – rejestr licznika

- EDX – rejestr danych

- Rejestry adresowe

- ESI – indeks źródła

- EDI – indeks przeznaczenia

- EBP – wskaźnik bazowy

- ESP – wskaźnik stosu

Z rejestrów ogólnego przeznaczenia można korzystać także jako rejestrów 16-bitowych (wykorzystywane jest wtedy młodsze 16 bitów rejestru 32-bitowego). Rejestry takie oznacza się z pominięciem litery E na początku symbolu. Dodatkowo, w przypadku rejestrów danych (EAX-EDX) można się odwoływać do ich 8-bitowych części – najmłodsze 8 bitów rejestru AX oznaczane jest przez AL, kolejne 8 przez AH. Odpowiednio najmłodsze bity rejestru BX oznacza się przez BL itd.

Rejestry koprocesora

[edytuj | edytuj kod]Koprocesor arytmetyczny w procesorach IA-32 zrealizowany jest w architekturze stosowej, tzn. dane tworzą stos. Położenie danych w koprocesorze określa się przez „odległość” od wierzchołka stosu, a nie konkretny symbol rejestru. Stos koprocesora tworzy 8 rejestrów 80-bitowych. Wierzchołek stosu oznacza się symbolem ST lub ST(0), kolejne rejestry w głąb stosu odpowiednio ST(1), ST(2), aż do ST(7). Rejestry stosu koprocesora mogą przechowywać liczby w formacie zmiennoprzecinkowym zgodnym z normą IEEE 754, o rozmiarze 32, 64 lub 80 bitów.

Ponadto w koprocesorze znajdują się 16-bitowe rejestry dodatkowe:

- rejestr stanu stosu koprocesora, określający typ zawartości ośmiu rejestrów stosu

- rejestr stanu koprocesora, m.in. sygnalizujący wyjątki i określający położenie wierzchołka stosu

- rejestr sterujący koprocesora, pozwala m.in. na ustawianie rodzaju zaokrąglenia, maskowanie wyjątków

Rejestry segmentowe

[edytuj | edytuj kod]W procesorach IA-32 zdefiniowano sześć 16-bitowych rejestrów segmentowych, służących albo do bezpośredniego określania adresu fizycznego w trybach stosujących segmentację pamięci, bądź jako selektory w trybie chronionym procesora. Rejestry te to:

- CS – rejestr segmentu kodu programu

- DS – rejestr segmentu danych

- SS – rejestr segmentu stosu

- ES, FS, GS – rejestry pomocnicze dla danych

Rejestry specjalnego przeznaczenia

[edytuj | edytuj kod]W procesorach IA-32 występuje również szereg innych rejestrów. Są to m.in.:

- EFLAGS – rejestr stanu opisujący i kontrolujący stan procesora,

- EIP – licznik programu, za jego pomocą procesor realizuje m.in. skoki, pętle, przejścia do podprogramów,

- rejestry technologii MMX i Streaming SIMD Extensions,

- inne rejestry kontrolne i służące do debugowania.

Wykonywanie programów

[edytuj | edytuj kod]Zestaw instrukcji

[edytuj | edytuj kod]Procesory IA-32 posiadają rozbudowany zestaw instrukcji, liczący kilkaset instrukcji. Liczba instrukcji rosła wraz z wprowadzaniem kolejnych technologii rozwijających model IA-32, jak MMX, SSE, 3DNow! itd. Cechą zestawu instrukcji IA-32, charakterystyczną dla architektur CISC jest fakt, że wiele ze złożonych instrukcji można zastąpić instrukcjami prostszymi, np. pętlę zrealizować można dokonując porównań i skoków warunkowych lub za pomocą specjalizowanej instrukcji pętli LOOP.

Instrukcje podzielić można na grupy:

- instrukcje przesyłania danych

- instrukcje kontroli przepływu (porównania, skoki, pętle)

- instrukcje arytmetyczne (stałoprzecinkowe, wykonywane przez jednostkę arytmetyczno-logiczną oraz zmiennoprzecinkowe, wykonywane przez koprocesor)

- instrukcje operacji logicznych

- operacje bitowe

- inne instrukcje

Instrukcje identyfikowane są przez procesor na podstawie binarnego kodu maszynowego. Dla wygody programistów opisano je jednak mnemonikami, ułatwiającymi programowanie na poziomie asemblera.

Kodowanie instrukcji

[edytuj | edytuj kod]Kodowaniem instrukcji zajmuje się kompilator lub asembler podczas kompilacji programu. Wynikowy kod maszynowy musi być zgodny z zasadami kodowania instrukcji IA-32. Rozkazy koduje się w postaci ciągów zero-jedynkowych. W architekturze IA-32 rozkazy są zmiennej długości, od 1 do nawet kilkunastu bajtów, w zależności od rodzaju rozkazu i typu argumentów.

Kod instrukcji zawiera identyfikator rozkazu oraz – jeśli posiada argumenty – położenie ich w pamięci lub ich wartości. W modelu IA-32, w celu ograniczenia długości rozkazu, w przypadku większości rozkazów przyjęto, że docelowe miejsce zapisu wyniku określone jest przez pierwszy z operandów oraz że tylko jeden z argumentów danej instrukcji może odwoływać się do pamięci.

Schemat kodu każdego rozkazu można podzielić na następujące części:

- Prefiksy instrukcji (opcjonalne) – do czterech bajtów dodatkowych informacji o instrukcji:

- prefiks LOCK (zapewniający wyłączność dostępu do pamięci wspólnej dla danej instrukcji),

- prefiksy powtarzania (REP, REPE, REPZ...) wykorzystywane w operacjach na blokach danych,

- prefiksy chwilowej zmiany segmentu,

- prefiks podpowiedzi rozgałęzienia (branch hint), pozwalający procesorowi na wybór bardziej prawdopodobnej ścieżki wykonania w przetwarzaniu potokowym,

- prefiksy zmiany rozmiaru operandu i zmiany rozmiaru adresu.

- Kod operacji długości 1-3 bajtów, zawierający często dodatkowe informacje:

- bit wskazujący, w którym operandzie zapisać wynik,

- bit oznaczający rozmiar operandów.

- Dodatkowe 3 bity kodu operacji znajdować się mogą także zamiast pola reg w bajcie ModR/M.

- Bajt ModR/M (tylko w przypadku instrukcji posiadających argumenty w pamięci lub rejestrach) – służy do określenia położenia argumentów. Składa się z trzech części:

- pole mod (2 bity) – określa czy operacja odwołuje się do pamięci oraz jaką długość ma ewentualne pole przesunięcia;

- pole reg (3 bity) – kod rejestru lub modyfikacji adresowej pierwszego argumentu, czasem występuje w roli dodatkowych bitów kodu operacji;

- pole R/M (3 bity) – kod rejestru lub modyfikacji adresowej drugiego argumentu.

- Bajt SIB (tylko w przypadku operacji o złożonym sposobie odwoływania się do pamięci, np. za pomocą podwójnej modyfikacji adresowej) – służy do określenia dodatkowych parametrów modyfikacji adresowych, m.in. współczynnik skali pozwalający na wygodne operowanie na tablicach.

- Pole przesunięcia (opcjonalne) – podaje odległość danych w stosunku do początku segmentu, może mieć długość 1, 2 lub 4 bajtów.

- Dane stałe (immediate, opcjonalne) – podana bezpośrednio wartość liczbowa argumentu o długości 1, 2 lub 4 bajtów.

Kod prostych instrukcji bez argumentów zajmuje z reguły 1 bajt, a np. skomplikowane operacje przesyłania danych do pamięci mogą zajmować 9 bajtów.

Cykl rozkazowy

[edytuj | edytuj kod]Procesor wykonuje instrukcje programu po kolei, zgodnie z ustalonym schematem, zwanym cyklem rozkazowym. Na cykl rozkazowy składa się kolejno:

- pobranie rozkazu z pamięci,

- dekodowanie kodu rozkazowego,

- obliczenie adresu efektywnego argumentu z uwzględnieniem modyfikacji adresowych, jeśli polecenie odwołuje się do pamięci,

- obliczenie adresu fizycznego argumentu (rzeczywistego położenia danej w pamięci fizycznej)

- pobranie argumentu z pamięci

- wykonanie rozkazu (np. obliczenie właściwego wyniku)

- zapisanie wyniku

- wyznaczenie położenia następnego rozkazu (odpowiednia modyfikacja rejestru EIP).

Współczesne procesory IA-32 stosują przetwarzanie potokowe, czyli technologię polegającą na jednoczesnym wykonywaniu kolejnych etapów cyklu dla sąsiednich rozkazów przez różne bloki funkcjonalne.

Producenci procesorów

[edytuj | edytuj kod]W ciągu ponad 25 lat istnienia i rozwoju architektury IA-32, powstało bardzo dużo procesorów opartych i implementujących ją. Wśród największych producentów takich procesorów warto wymienić: Intel, AMD, VIA, Cyrix, Centaur Technology, Transmeta, IBM, NexGen, NEC, UMC, SiS, ALi, nVidia. Część z tych firm produkowała lub projektowała procesory z architekturą IA-32 tylko przez pewien okres, część również przestała istnieć lub została wykupiona przez innych producentów.

Zobacz też

[edytuj | edytuj kod]Linki zewnętrzne

[edytuj | edytuj kod]- Intel® 64 and IA-32 Architectures Software Developer Manuals. Intel.com. [dostęp 2018-10-20]. (ang.).