本 ほん 条目 じょうもく 存在 そんざい 以下 いか ,请协

助 すけ 改善 かいぜん 本 ほん 条目 じょうもく 或 ある 在 ざい 讨论页 针对议题发表

看 み 法 ほう 。

此条目 め 需要 じゅよう 更新 こうしん (2022年 ねん 月 がつ 日 にち ) 请更新 しん 本文 ほんぶん 反映 はんえい 近 きん 新 しん 增 ぞう 内容 ないよう 完成 かんせい 修 おさむ 改 あらため 后 きさき 除 じょ 本 ほん 模 も 板 ばん

PCI Express PCI Express标志

英文 えいぶん 全 ぜん 名 な Peripheral Component 发明日 び 期 き 2003年 ねん ,21年 ねん 前 まえ (2003 ) 发明者 しゃ 阔度 1-32 最多 さいた 1 带宽 单通道 どう 和 わ 通 つう 道 どう 双 そう 每 まい 方向 ほうこう v. 1.x (2.5 GT /s): 0.25 GB/s (x1) 4.00 GB/s (x16) v. 2.x (5 GT/s): 0.50 GB/s (x1) 8.00 GB/s (x16) v. 3.x (8 GT/s): 0.98 GB/s (x1) 15.75 GB/s (x16) v. 4.x (16 GT/s): 1.97 GB/s (x1) 31.51 GB/s (x16) v. 5.x (32 GT/s): 3.94 GB/s (x1) 63.02 GB/s (x16) v. 6.x (64 GT/s): 7.56 GB/s (x1) 121.00 GB/s (x16) 类别 串 くし 行 ぎょう 热插拔 支持 しじ 依 よ 制式 せいしき 外 そと 置 おけ 接 せっ 口 こう 支持 しじ 通 つう 和 わ 外接 がいせつ 例 れい Thunderbolt

Peripheral Component Interconnect Express ,简称PCI-E ,官 かん 方 かた PCIe ,是 ぜ 计算机 つくえ 的 てき 一 いち 重要 じゅうよう 分 ぶん 支 ささえ 用 よう 既 すんで 有 ゆう 的 てき 概念 がいねん 号 ごう 了 りょう 更 さら 加 か 高速 こうそく 的 てき 串 くし 行 ゆき 通信 つうしん 系 けい 准 じゅん 目前 もくぜん 由 ゆかり PCI-SIG 组织制定 せいてい 和 わ 用 よう 部 ぶ 由 よし 是 ぜ 基 もと 有 ゆう 的 てき PCI 系 けい 所以 ゆえん 只 ただ 改 あらため 物理 ぶつり 改 あらため 将 はた 系 けい

PCIe拥有更 さら 快 かい 的 まと 速 そく 率 りつ 所 しょ 代 だい 了 りょう 以往 いおう 所有 しょゆう 的 てき 内部 ないぶ 总线 (包括 ほうかつ AGP 和 かず 英 えい 特 とく 和 わ AMD 已 やめ 采 さい 用 よう 片 へん 取 と 代 だい 原 はら 有 ゆう 的 てき 南 みなみ 和 わ 北 きた 方案 ほうあん

除 じょ 外 がい 能 のう 支持 しじ 热拔插 以及热交换 特性 とくせい 目前 もくぜん 支持 しじ 的 てき

考 こう 显卡 功 こう 日 び 益 えき 增加 ぞうか 在 ざい 中 ちゅう 改善 かいぜん 了 りょう 直接 ちょくせつ 槽 そう 中 ちゅう 取 と 功 こう 率 りつ 限 げん 制 せい 的 てき 最大 さいだい 提供 ていきょう 功 こう 率 りつ 一 いち 度 ど 了 りょう [ 1] 相 あい 接 せっ 口 こう 有 ゆう 了 りょう 的 てき 提 ひさげ 升 ます

PCIe保 ほ 兼 けん 容 よう 性 せい 支持 しじ 的 てき 操作 そうさ 系 けい 行 ぎょう 任 にん 何 なん 更改 こうかい 即 そく 可 か 支持 しじ 升 ます 来 らい 方便 ほうべん 由 よし 最大 さいだい 的 てき 意 い 的 てき 通用 つうよう 性 せい 不 ふ 的 てき 延伸 えんしん 到 いた 芯 しん 片 へん 接 せっ 器 き 整 せい I/O 系 けい 新 しん 起 おこり 来 らい 将 はた 更 さら 增加 ぞうか 机 つくえ 的 てき 可 か 移植 いしょく 性 せい 和 わ 模 かたぎ

在 ざい 年 ねん 的 てき 春季 しゅんき 英 えい 特 とく 上 じょう 公布 こうふ 取 と 代 だい 的 てき 第 だい 三 さん 代 だい 技 わざ 被 ひ 称 しょう 3GIO ”。该总线的规范由 よし 支持 しじ 的 てき AWG (Arapahoe Work Group)负责制定 せいてい 年 ねん 月 がつ 日 にち 正式 せいしき 宣布 せんぷ 草稿 そうこう 制定 せいてい 完 かん 移 うつり PCI特殊 とくしゅ (PCI-SIG)进行审核,2002年 ねん 月 がつ 日 にち 后 きさき 正式 せいしき 公布 こうふ 改名 かいめい 据 すえ 在 ざい 年 ねん 正式 せいしき [ 2] [ 3] 年 ねん 月 がつ 日 にち 官 かん 方 かた 了 りょう 的 てき 版 はん 基 もと 主要 しゅよう 定 てい 的 てき 架 か 属性 ぞくせい 管理 かんり 接 せっ 口 こう 等 とう 内容 ないよう [ 4]

PCI Express 总线性能 せいのう [ 2] [ 3]

版本 はんぽん 推出

Line 编码

每 まい 通 つう 道 どう 率 りつ [ i] 带宽(每 まい 方向 ほうこう [ i]

x1

x2

x4

x8

x16

1.0

2003

NRZ

8b/10b

2.5 GT /s

0.250 GB /s

0.500 GB/s

1.000 GB/s

2.000 GB/s

4.000 GB/s

2.0

2007

5.0 GT/s

0.500 GB/s

1.000 GB/s

2.000 GB/s

4.000 GB/s

8.000 GB/s

3.0

2010

128b/130b

8.0 GT/s

0.985 GB/s

1.969 GB/s

3.938 GB/s

0 7.877 GB/s15.754 GB/s

4.0

2017

16.0 GT/s

1.969 GB/s

3.938 GB/s

0 7.877 GB/s15.754 GB/s

0 31.508 GB/s

5.0[ 5] [ 6]

2019[ 7] [ 8]

32.0 GT/s [ ii] 3.938 GB/s

0 7.877 GB/s15.754 GB/s

31.508 GB/s

63.015 GB/s

6.0

2021

PAM-4 FEC

1b/1bFLIT

64.0 GT/s 32.0 GBd

7.563 GB/s

15.125 GB/s

30.250 GB/s

60.500 GB/s

121.000 GB/s

7.0

2025

128.0 GT/s 64.0 GBd

15.125 GB/s

30.250 GB/s

60.500 GB/s

121.000 GB/s

242.000 GB/s

^ 1.0 1.1 每 まい 条 じょう 通 どおり 道 どう 都 みやこ 是 ただし 全 ぜん 双 そう 工 こう 通 つう 道 どう ^ 出 で 行 ぎょう 性 せい 最初 さいしょ

以PCIe 2.0为例,每秒 まいびょう 原始 げんし 数 すう 据 すえ 率 りつ 方式 ほうしき 每 まい 特 とく 只 ただ 有 ゆう 有效 ゆうこう 数 すう 据 すえ 即 そく 有效 ゆうこう

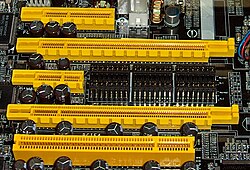

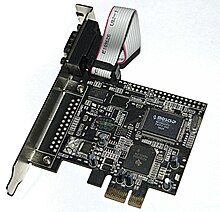

与 あずか 比 ひ [ 编辑 ] PCI Express ×16插槽 PCI Express ×1插槽 PCIe的 てき 主要 しゅよう 是 ぜ 提 ひさげ 升 ます 内部 ないぶ 所有 しょゆう 的 てき 速度 そくど 因 いん 带宽 有 ゆう 多 た 同 どう 是 ぜ 特 とく 所 しょ 的 てき 效率 こうりつ 最高 さいこう 不 ふ 上 じょう 的 てき 出 で 但 ただし 是 ぜ 指 ゆび 的 てき 理想 りそう 是 ぜ 使用 しよう 接 せっ 口 こう 的 てき 猛 もう 性能 せいのう 表 ひょう 的 てき 数 すう 据 すえ 会 かい 有 ゆう 大 だい 的 てき 差 さ 存在 そんざい [ 9] [ 10]

传输通 どおり 道 みち 数 すう

脚 あし 主 しゅ 接 せっ 口 こう 区 く 数 すう 总长 度 ど

主 しゅ 接 せっ 口 こう 区 く

x1

36

14

25 mm

7.65 mm

x4

64

42

39 mm

21.65 mm

x8

98

76

56 mm

38.65 mm

x16

164

142

89 mm

71.65 mm

规格

总线宽度

工作 こうさく 主 ぬし 资料速 そく 率 りつ

PCI 2.3

32位 い

33/66 MHz

133/266 MB/s

PCI-X 1.0

64位 い

66/100/133 MHz

533/800/1066 MB/s

PCI-X 2.0(DDR)

64位 い

133 MHz

2.1 GB/s

PCI-X 2.0(QDR)

64位 い

133 MHz

4.2 GB/s

AGP 2X

32位 い

66 MHz

*2=532 MB/s

AGP 4X

32位 い

66 MHz

*4=1.0 GB/s

AGP 8X

32位 い

66 MHz

*8=2.1 GB/s

PCI-E 1.0 X1

1比 ひ 特 とく

2.5 GHz

250 MB/s

PCI-E 1.0 X2

2比 ひ 特 とく

2.5 GHz

500 MB/s

PCI-E 1.0 X4

4位 い

2.5 GHz

1 GB/s

PCI-E 1.0 X8

8位 い

2.5 GHz

2 GB/s

PCI-E 1.0 X16

16位 い

2.5 GHz

4 GB/s

计算公式 こうしき 串 くし 行 ゆき 串 くし 行 ゆき 串 くし 行 ゆき 位 い 串 くし 行 ゆき 管 かん 方式 ほうしき 每 まい 数 すう 据 すえ 例 れい 双 そう 工 こう

PCI Express 1.0总线频率2500 MHz,这是在 ざい 的 てき 基 もと 准 じゅん 通 どおり 锁相环 振 ふ 的 てき 提 ひさげ 高 だか 到 いた 高 だか 到 いた 方式 ほうしき

的 てき 硬 かた 件 けん [ 编辑 ] PCIe的 てき 是 ぜ 建立 こんりゅう 在 ざい 点 てん 基 もと 上 じょう 之 の 通 つう 道 どう 一 いち 点 てん 上 じょう 与 あずか 早期 そうき 形成 けいせい 基 もと 制 せい 所有 しょゆう 共 ども 享 とおる 双 そう 向 こう 位 い 是 ぜ 由 よし 事 ごと 数 すう 据 すえ 物理 ぶつり 成 なり 物理 ぶつり 可 か 子 こ 可分 かぶん 理代 りよ 和 かず 介 かい 入 にゅう 控 ひかえ 制 せい 子 こ 借用 しゃくよう 自 じ IEEE 802 网络协议模型 もけい 通 どおり ASPM 管理 かんり

各 かく 式 しき 不同 ふどう 的 てき 由 よし 上 じょう 与 あずか 相 あい 的 てき 最 さい 下方 かほう 取 と 自 じ 的 てき 机 つくえ 板 ばん 于使用 しよう 方面 ほうめん 每 まい 水 すい 使用 しよう 的 てき 低 てい 差分 さぶん 信号 しんごう 合 ごう 接收 せっしゅう 不 ふ 同数 どうすう 据 すえ 会 かい 使用 しよう 不同 ふどう 的 てき 通 どおり 道 どう 每 まい 之 の 成 なり 形成 けいせい 更 さら 多 た 的 てき 通 どおり 道 どう 各 かく 少 しょう 支持 しじ 通 どおり 道 どう 的 てき 道 どう 的 てき 好 このみ 的 てき 提供 ていきょう 双 そう 向 こう 兼 けん 容 よう 性 せい 模 も 式 しき 将 しょう 用 よう 部 ぶ 接 せっ 口 こう 模 も 式 しき 使用 しよう 在 ざい 至 いたり 少 しょう 与 あずか 之 これ 通 どおり 道 どう 相当 そうとう 的 てき 上 じょう 例 れい 接 せっ 口 こう 的 てき 能 のう 工作 こうさく 在 ざい 或 ある 的 てき 上 じょう 例 れい 道 どう 的 てき 能 のう 支持 しじ 道 どう 之 の 将 しょう 使用 しよう 通 どおり 道 どう 数 すう 的 てき 作 さく 准 じゅん 一 いち 支持 しじ 通 どおり 道 どう 的 てき 不能 ふのう 在 ざい 支持 しじ 通 どおり 道 どう 的 てき 上 じょう 正常 せいじょう 工作 こうさく 例 れい 接 せっ 口 こう 的 てき 不能 ふのう 在 ざい 的 てき 上 じょう 正常 せいじょう 工作 こうさく 入 いれ 但 ただし 在 ざい 的 てき 上 じょう 只 ただ 建立 こんりゅう 道 どう 在 ざい 同 どう 方便 ほうべん 与 あずか PCI 的 てき 兼 けん 容 よう 多 た 通 どおり 道上 どうじょう 的 てき 数 すう 据 すえ 采 さい 取 と 交叉 こうさ 意味 いみ 着 ぎ 字 じ 交叉 こうさ 在 ざい 不同 ふどう 的 てき 通 どおり 道 どう 上 じょう 数 かず 据 すえ 条 じょう 需要 じゅよう 非常 ひじょう 的 てき 硬 かた 件 けん 支持 しじ 数 すう 据 すえ 的 てき 同 どう 步 ふ 的 てき 数 すう 据 すえ 量 りょう 要求 ようきゅう 由 よし 据 すえ 填 はま 充 たかし 的 てき 数 すう 据 すえ 交叉 こうさ 不 ふ 需要 じゅよう 数 すう 据 すえ 包 つつみ 与 あずか 高速 こうそく 数 すう 一 いち 信 しん 息 いき 嵌入 かんにゅう 信号 しんごう 中 ちゅう 在 ざい 物理 ぶつり 采 さい 用 よう 常 つね 代 だい 式 しき 来 らい 的 てき 和 わ 字 じ 符 ふ 串 くし 符合 ふごう 保 ほ 接收 せっしゅう 端 はし 不 ふ 会 かい 方案 ほうあん 用 よう 位 い 比 ひ 特 とく 代替 だいたい 比 ひ 特 とく 来 らい 数 すう 据 すえ 占 うらない 用 よう 的 てき 到 いた 了 りょう 采 さい 用 よう 代 だい 式 しき 用 よう 的 てき 有 ゆう SONET )使用 しよう 的 てき 不 ふ 在 ざい 数 すう 据 すえ 流 りゅう 中 ちゅう 嵌入 かんにゅう 信 しん 息 いき 的 てき 特性 とくせい 不 ふ 化 か 的 てき 方法 ほうほう 但 ただし 方法 ほうほう 与 あずか 完全 かんぜん 不同 ふどう 方法 ほうほう 主要 しゅよう 用 よう 来 らい 数 すう 据 すえ 中 ちゅう 的 てき 数 すう 据 すえ 重 じゅう 出 で 据 すえ 散 ち 射 しゃ 第 だい 一 いち 代 だい 采 さい 用 よう 号 ごう 率 りつ 在 ざい 未来 みらい 版本 はんぽん 中 ちゅう 增强 ぞうきょう 到 いた

数 かず 据 すえ 用 よう 的 てき 息 いき 包 つつみ 是 ぜ 由 よし 生成 せいせい 位 い 循环冗余校 こう 码(CRC,本 ほん 文中 ぶんちゅう 用 よう 数 すう 据 すえ 保 ほ 采 さい 用 よう 著名 ちょめい 的 てき 的 てき 信 しん 息 いき 包 つつみ 能 のう 通 どおり 校 こう 性 せい 校 こう 称 しょう 命令 めいれい 正 せい 答 こたえ 没 ぼつ 有 ゆう 通 どおり 称 しょう 没 ぼつ 有 ゆう 没 ぼつ 有 ゆう 的 てき 或 ある 者 もの 等 とう 待 まち 超 ちょう 会 かい 被 ひ 重 じゅう 新 しん 内容 ないよう 存 そん 数 すう 据 すえ 内 ない 可 か 保 ほ 的 てき 不 ふ 子 こ 干 ひ 有 ゆう 所 しょ 在 ざい 收 おさむ 到 いた 数 すう 据 すえ 包 つつみ 之 の 后 きさき 在 ざい 是 ぜ 延 のべ 的 てき 等 とう 待 まち 因 よし 流 りゅう 程 ほど 的 てき 需要 じゅよう 出 で 重 じゅう 新 しん 器 き

TLPs加 か 上 じょう 比 ひ 特 とく 后 きさき 被 ひ 包 つつみ 据 すえ 息 いき 包 つつみ 除 じょ 了 りょう 外 がい 信号 しんごう 和 わ 信号 しんごう 亦 また 被 ひ 包 つつみ 信 しん 息 いき 包 つつみ 中 ちゅう 除 じょ 外 がい 来 らい 的 てき 流 りゅう 控 ひかえ 制 せい 信 しん 息 いき 和 わ 管理 かんり 功 こう 能 のう

PCI Express采 さい 用 よう 分 ぶん 数 かず 据 すえ 提 ひさげ 在 ざい 上分 かみぶん 可 か 保 ほ 道 どう 在 ざい 目 め 等 とう 待 まち 回 かい 息 いき 数 すう 据 すえ 信 しんじ 息 いき

PCI Express采 さい 用 よう 可 か 信 しん 性 せい 流 りゅう 控 ひかえ 制 せい 模 も 式 しき 下 か 所 しょ 占 うらない 用 よう 的 てき 可 か 信 しん 信号 しんごう 量 りょう 直 ちょく 至 いたり 接收 せっしゅう 端初 たんしょ 始 はじめ 可 か 信 しん 信号 しんごう 最高 さいこう 接收 せっしゅう 端 はし 在 ざい 完 かん 存 そん 中 ちゅう 的 てき 后 きさき 回送 かいそう 端 はし 可 か 信 しん 信号 しんごう 是 ぜ 定 じょう 制 せい 的 てき 器 き 相 そう 比 ひ 他 た 方法 ほうほう 握手 あくしゅ 的 てき 模 も 式 しき 的 てき 在 ざい 信 しん 信号 しんごう 的 てき 回 かい 会 かい 影 かげ 性能 せいのう 因 いん 果 はて 双方 そうほう 的 てき 足 あし 是 ぜ 不 ふ 会 かい 出 で 到 いた 可 か 信 しん 信号 しんごう 最高 さいこう 情 じょう 数 すう 据 すえ 不 ふ 会 かい 停 とま

第 だい 一 いち 代 だい 可 か 支持 しじ 每 ごと 通 どおり 道 どう 每秒 まいびょう 的 てき 数 すう 据 すえ 率 りつ 除 じょ 位 い 每 まい 字 じ 意味 いみ 着 ぎ 一 いち 通 つう 道 どう 的 てき 可 か 的 てき 率 りつ 要 よう 根 ね 据 すえ 数 すう 据 すえ 有效 ゆうこう 率 りつ 即 そく 依 よ 数 すう 据 すえ 的 てき 本身 ほんみ 特性 とくせい 由 よし 更 さら 高 だか 程 ほど 序 じょ 和 わ 中 ちゅう

PCI Express与 あずか 高速 こうそく 序列 じょれつ 系 けい 相似 そうじ 的 てき 强健 きょうけん 性 せい CRC校 こう 和 わ ACK )。长时间连续的单向数 すう 据 すえ 高速 こうそく 存 そん 可 か 的 てき 通 どおり 道 みち 数 すう 据 すえ 利用 りよう 率 りつ 的 てき 受益 じゅえき 增加 ぞうか 的 てき 通 どおり 道 どう 等 とう 但 ただし 大 だい 多数 たすう 程 ほど 序 じょ 或 ある 制 せい 器 き 会 かい 把 わ 内容 ないよう 小 しょう 的 てき 数 すう 据 すえ 包 つつめ 同 どう 会 かい 强制 きょうせい 加 か 上 じょう 信号 しんごう 数 すう 据 すえ 由 よし 加数 かすう 据 すえ 包 つつみ 的 てき 解析 かいせき 和 わ 强制 きょうせい 中断 ちゅうだん 降 くだ 低 てい 通 どおり 道 どう 的 てき 效率 こうりつ 作 さく 通信 つうしん 需要 じゅよう 通信 つうしん 要求 ようきゅう 的 てき 高 だか 数 すう 据 すえ 容 よう 忍 にん 度 ど 效率 こうりつ 的 てき 降 くだ 低 てい 只 ただ 出 で 上 じょう

下表 かひょう 列 れつ 出 で 在 ざい 器 き 上 じょう 的 てき 在 ざい 印刷 いんさつ 板 ばん 的 てき [ 11] 和 かず 比 ひ 稍 やや 短 たん 保 ほ 插入 そうにゅう 全 ぜん 插入 そうにゅう 采 さい 用 よう 全 ぜん 机 つくえ 但 ただし 拉 ひしげ 高 だか 用 よう 表明 ひょうめい 是能 これよし [ 12]

PCI Express连接器 き 的 てき

引脚

B侧

A侧

描述

引脚

B侧

A侧

描述

1

+12 V

PRSNT1#

必须连接到 いた 最 さい

50

HSOp (8)

Reserved

通 つう 道 どう 数 すう 据 すえ 和 わ

2

+12 V

+12 V

51

HSOn (8)

Ground

3

+12 V

+12 V

52

Ground

HSIp (8)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ

4

Ground

Ground

53

Ground

HSIn (8)

5

SMCLK

TCK

SMBus 和 わ JTAG 端 はし 口 こう 54

HSOp (9)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ

6

SMDAT

TDI

55

HSOn (9)

Ground

7

Ground

TDO

56

Ground

HSIp (9)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ

8

+3.3 V

TMS

57

Ground

HSIn (9)

9

TRST#

+3.3 V

58

HSOp (10)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ

10

+3.3 V aux

+3.3 V

备用电源

59

HSOn (10)

Ground

11

WAKE#

PERST#

链接激 げき 活 かつ 基本 きほん

60

Ground

HSIp (10)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ

Key notch

61

Ground

HSIn (10)

12

CLKREQ#

Ground

要求 ようきゅう 的 てき 62

HSOp (11)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ

13

Ground

REFCLK+

参考 さんこう 差分 さぶん 63

HSOn (11)

Ground

14

HSOp (0)

REFCLK−

64

Ground

HSIp (11)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ

15

HSOn (0)

Ground

65

Ground

HSIn (11)

16

Ground

HSIp (0)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ 66

HSOp (12)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ

17

PRSNT2#

HSIn (0)

67

HSOn (12)

Ground

18

Ground

Ground

68

Ground

HSIp (12)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ

PCI Express ×1卡于引脚18结束

69

Ground

HSIn (12)

19

HSOp (1)

Reserved

通 つう 道 どう 数 すう 据 すえ 和 わ 70

HSOp (13)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ

20

HSOn (1)

Ground

71

HSOn (13)

Ground

21

Ground

HSIp (1)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ 72

Ground

HSIp (13)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ

22

Ground

HSIn (1)

73

Ground

HSIn (13)

23

HSOp (2)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ 74

HSOp (14)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ

24

HSOn (2)

Ground

75

HSOn (14)

Ground

25

Ground

HSIp (2)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ 76

Ground

HSIp (14)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ

26

Ground

HSIn (2)

77

Ground

HSIn (14)

27

HSOp (3)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ 78

HSOp (15)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ

28

HSOn (3)

Ground

79

HSOn (15)

Ground

29

Ground

HSIp (3)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ 80

Ground

HSIp (15)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ

30

Reserved

HSIn (3)

81

PRSNT2#

HSIn (15)

31

PRSNT2#

Ground

82

Reserved

Ground

32

Ground

Reserved

PCI Express ×4卡于引脚32结束

33

HSOp (4)

Reserved

通 つう 道 どう 数 すう 据 すえ 和 わ

34

HSOn (4)

Ground

35

Ground

HSIp (4)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ

36

Ground

HSIn (4)

37

HSOp (5)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ

38

HSOn (5)

Ground

39

Ground

HSIp (5)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ

40

Ground

HSIn (5)

41

HSOp (6)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ

42

HSOn (6)

Ground

43

Ground

HSIp (6)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ 图例

44

Ground

HSIn (6)

接地 せっち 零 れい 基 もと 准 じゅん

45

HSOp (7)

Ground

通 つう 道 どう 数 すう 据 すえ 和 わ 电源引脚

为PCIe卡供电

46

HSOn (7)

Ground

输出引脚

从PCIe卡到主 ぬし 板 いた 的 てき 信号 しんごう

47

Ground

HSIp (7)

通 つう 道 どう 接收 せっしゅう 数 すう 据 すえ 和 わ 输入引脚

从主板 ばん 到 いた 信号 しんごう

48

PRSNT2#

HSIn (7)

漏 も 路 ろ 可 か 拉 ひしげ 至 いたり 低 てい 或 ある 感 かん 多 た

49

Ground

Ground

检测引脚

卡连接 せっ 在 ざい 一起 かずき

PCI Express ×8卡于引脚49结束

备用

目前 もくぜん 没 ぼつ 有 ゆう 使用 しよう 不 ふ

有 ゆう RS-232 接 せっ 口 こう 的 てき 基 もと 速 そく 序列 じょれつ 了 りょう 包括 ほうかつ HyperTransport 、InfiniBand 、RapidIO 和 わ StarFabric 等 ひとし 等 ひとし 均 ひとし 有 ゆう 的 てき 不同 ふどう 企 くわだて 支持 しじ 背 せ 后 きさき 有 ゆう 大量 たいりょう 的 てき 投入 とうにゅう 的 てき 研究 けんきゅう 所以 ゆえん 每 ごと 独占 どくせん 主要 しゅよう 的 てき 差 さ 性 せい 性 せい 与 あずか 反 はん 成本 なりもと 的 てき 取 と 舍 しゃ 平衡 へいこう 各 かく 不 ふ 相 あい 同 どう 的 てき 一 いち 子 こ 是 ぜ 在 ざい 包 つつみ 上 じょう 增加 ぞうか 不 ふ 支持 しじ 方式 ほうしき 的 てき 信 しん 息 いき 增加 ぞうか 降 くだ 低 てい 了 りょう 接 せっ 口 こう 的 てき 有效 ゆうこう 更 さら 但 ただし 是 ぜ 相 しょう 造 づくり 了 りょう 新 しん 的 てき 支持 しじ 能 のう 架 か 需要 じゅよう 追 つい 支持 しじ 和 わ 即 そく 能 のう 功 こう 能 のう 的 てき 信 しん 息 いき 包 つつみ 意味 いみ 着 ぎ 包 つつみ 用 よう 了 りょう 包 つつみ 的 てき 更 さら 大 だい 百分比 ひゃくぶんひ 又 また 降 くだ 低 てい 了 りょう 有效 ゆうこう 能 のう 能 のう 的 てき 是 ぜ 和 わ 取 と 中庸 ちゅうよう 之 の 道 みち 定位 ていい 一 いち 系 けい 口 こう 透明 とうめい 目 め 制 せい 了 りょう 某 ぼう 程度 ていど 上 じょう 增加 ぞうか 了 りょう 反 はん

技 わざ 嘉 よしみ 采 さい 用 よう 在 ざい 年 ねん 已 やめ 近 きん 的 てき 主 しゅ 板 いた 不 ふ 少 しょう 但 ただし 最 さい 基本 きほん 的 てき 原因 げんいん 是 ぜ 软件 开发者 しゃ 完全 かんぜん 透明 とうめい 所 しょ 的 てき 操作 そうさ 系 けい 何 なん 代 だい 改 あらため 来 らい 其二 そのじ 增强 ぞうきょう 系 けい 性能 せいのう 强 きょう 有力 ゆうりょく 的 てき 品 ひん 牌 ぱい 各 かく 声 こえ 当 とう 下 した 的 てき 固 かた 都 と 使用 しよう 了 りょう 下面 かめん 流 りゅう 的 てき 使用 しよう 的 てき 外 そと 品 ひん

大 だい 部分 ぶぶん 新型 しんがた 的 てき 或 ある 都 と 使用 しよう 在 ざい 的 てき SLI 上 うえ 采 さい 用 よう 的 てき 高速 こうそく 数 すう 据 すえ 得 とく 相 しょう 同 どう 芯 しん 片 へん 可 か 同 どう 工作 こうさく 一 いち 台 だい 之 の 上 うえ 公司 こうし 一 いち GPU 一同运作的技术,称 しょう CrossFire 。

当 とう 下 した 主流 しゅりゅう 的 てき 固 かた 口 こう 有 ゆう M.2 、U.2 、PCIe、SATA 、SATA Express 、SAS 等 ひとし 和 わ 可 か 接 せっ 口 こう [ 14] NVMe 协议是 ぜ 目前 もくぜん 最高 さいこう 效 こう 的 てき

一般 いっぱん 标准 存 そん 外 そと 音 おと 可 か 移 うつり 嵌入 かんにゅう 式 しき

注 ちゅう 接 せっ 口 こう 依 よ 大 だい 速度 そくど 增 ぞう 序 じょ 排列 はいれつ 每 まい 后 きさき 列 れつ 出 で 的 てき 接 せっ 口 こう 是 ぜ 最 さい 快 かい 的 てき