本 ほん 條目 じょうもく 存在 そんざい 以下 いか 問題 もんだい ,請協

助 すけ 改善 かいぜん 本 ほん 條目 じょうもく 或 ある 在 ざい 討論 とうろん 頁 ぺーじ 針 はり 對 たい 議題 ぎだい 發表 はっぴょう 看 み 法 ほう 。

此條目 め 需要 じゅよう 更新 こうしん (2022年 ねん 月 がつ 日 にち ) 請更新 しん 本文 ほんぶん 反映 はんえい 近況 きんきょう 和 わ 新 しん 增 ぞう 完成 かんせい 修 おさむ 改 あらため 後 ご 除 じょ 本 ほん 模 も 板 ばん

PCI Express PCI Express標 しるべ 誌 し

英文 えいぶん 全 ぜん 名 な Peripheral Component 發明 はつめい 日 び 期 き 2003年 ねん ,21年 ねん 前 まえ (2003 ) 發明 はつめい 者 しゃ 闊度 1-32 最多 さいた 連接 れんせつ 1 頻 しき 寬 ひろし 單 たん 連結 れんけつ 和 わ 通 つう 道 どう 連接 れんせつ 雙 そう 單 たん 工 こう 每 まい 個 こ 方向 ほうこう v. 1.x (2.5 GT /s): 0.25 GB/s (x1) 4.00 GB/s (x16) v. 2.x (5 GT/s): 0.50 GB/s (x1) 8.00 GB/s (x16) v. 3.x (8 GT/s): 0.98 GB/s (x1) 15.75 GB/s (x16) v. 4.x (16 GT/s): 1.97 GB/s (x1) 31.51 GB/s (x16) v. 5.x (32 GT/s): 3.94 GB/s (x1) 63.02 GB/s (x16) v. 6.x (64 GT/s): 7.56 GB/s (x1) 121.00 GB/s (x16) 類別 るいべつ 串 くし 行 ぎょう 熱 ねつ 支援 しえん 依 よ 格式 かくしき 外 そと 置 おけ 介 かい 面 めん 支援 しえん 通過 つうか 和 わ 外接 がいせつ 線 せん 例 れい Thunderbolt

Peripheral Component Interconnect Express ,簡稱PCI-E ,官 かん 方 かた PCIe ,是 ぜ 電腦 でんのう 排 はい 的 てき 一 いち 個 こ 重要 じゅうよう 分 ぶん 支 ささえ 用 よう 既 すんで 有 ゆう 的 てき 編 へん 程 ほど 概念 がいねん 號 ごう 標準 ひょうじゅん 並 なみ 建 たて 了 りょう 更 さら 加 か 高速 こうそく 的 てき 串 くし 行 ぎょう 通 どおり 系統 けいとう 標準 ひょうじゅん 目前 もくぜん 標準 ひょうじゅん 由 ゆかり PCI-SIG 組織 そしき 制定 せいてい 和 わ 應用 おうよう 部 ぶ 由 よし 是 ぜ 基 もと 有 ゆう 的 てき PCI 系統 けいとう 所以 ゆえん 只 ただ 改 あらため 實體 じったい 層 そう 改 あらため 將 しょう 現有 げんゆう 系統 けいとう 轉換 てんかん 為 ため

PCIe擁 よう 有 ゆう 更 さら 快 かい 的 まと 速 そく 率 りつ 所以 ゆえん 幾 いく 代 だい 了 りょう 以往 いおう 所有 しょゆう 的 てき 匯流排 はい (包括 ほうかつ AGP 和 かず 現在 げんざい 英 えい 特 とく 爾 なんじ 和 わ AMD 已 やめ 採用 さいよう 單 たん 晶 あきら 片 へん 組 ぐみ 技術 ぎじゅつ 取 と 代 だい 原 はら 有 ゆう 的 てき 南橋 なんきょう 和 わ 北橋 きたはし 方案 ほうあん

除 じょ 外 がい 裝置 そうち 能 のう 支援 しえん 熱 ねつ 熱 ねつ 交換 こうかん 特性 とくせい 目前 もくぜん 支援 しえん 的 てき 三 さん 種 しゅ 電壓 でんあつ 分別 ふんべつ 為 ため

考慮 こうりょ 到 いた 現在 げんざい 顯示 けんじ 功 こう 日 び 益 えき 增加 ぞうか 在 ざい 規範 きはん 中 ちゅう 改善 かいぜん 了 りょう 直接 ちょくせつ 從 したがえ 中 ちゅう 取 と 電 でん 的 てき 功 こう 率 りつ 限 げん 制 せい 的 てき 最大 さいだい 提供 ていきょう 功 こう 率 りつ 一 いち 度 ど 達 たち 到 いた 了 りょう [ 1] 相對 そうたい 介 かい 面 めん 有 ゆう 了 りょう 的 てき 提 ひさげ 升 ます

PCIe保證 ほしょう 了 りょう 相 しょう 容 よう 性 せい 支援 しえん 的 てき 作業 さぎょう 系統 けいとう 無 む 進行 しんこう 任 にん 何 なん 更改 こうかい 即 そく 可 か 支援 しえん 總 そう 線 せん 給 きゅう 用 よう 戶 と 的 てき 升 ます 級 きゅう 帶 たい 來 らい 方便 ほうべん 由 よし 見 み 最大 さいだい 的 てき 意義 いぎ 在 ざい 的 てき 通用 つうよう 性 せい 不 ふ 橋 きょう 和 わ 裝置 そうち 的 てき 連接 れんせつ 延伸 えんしん 到 いた 晶 あきら 片 へん 組 ぐみ 間 あいだ 的 てき 連接 れんせつ 連接 れんせつ 圖形 ずけい 處理 しょり 器 き 整 せい 個 こ I/O 系統 けいとう 重 おも 新 しん 統一 とういつ 起 おこり 來 らい 將 はた 更進 こうしん 一 いち 步 ほ 電腦 でんのう 系統 けいとう 增加 ぞうか 電腦 でんのう 的 てき 可 か 移植 いしょく 性 せい 和 わ 模 も 組 ぐみ 化 か

在 ざい 年 ねん 的 てき 春季 しゅんき 英 えい 特 とく 爾 なんじ 開發 かいはつ 者 しゃ 討論 とうろん 區 く 上 じょう 公 こう 代 だい 排 はい 的 てき 第 だい 三 さん 代 だい 技術 ぎじゅつ 被 ひ 稱 しょう 為 ため 3GIO 」。該匯流 りゅう 排 はい 的 てき 規範 きはん 由 よし 支援 しえん 的 てき AWG (Arapahoe Work Group)負 ふ 責 せめ 制定 せいてい 年 ねん 月 がつ 日 にち 正式 せいしき 宣 せん 規範 きはん 草稿 そうこう 制定 せいてい 完 かん 移 うつり PCI特殊 とくしゅ 興趣 きょうしゅ 組織 そしき (PCI-SIG)進行 しんこう 年 ねん 月 がつ 日 にち 經過 けいか 後 ご 正式 せいしき 公 こう 改名 かいめい 為 ため 並 なみ 根據 こんきょ 開發 かいはつ 藍 あい 圖 ず 在 ざい 年 ねん 正式 せいしき 規範 きはん [ 2] [ 3] 年 ねん 月 がつ 日 にち 官 かん 方 かた 發 はつ 的 てき 版 はん 基礎 きそ 規範 きはん 規範 きはん 主要 しゅよう 定義 ていぎ 了 りょう 的 てき 架 か 屬性 ぞくせい 規範 きはん 網 あみ 絡 からま 結構 けっこう 管理 かんり 編 へん 程 ほど 介 かい 面 めん 等 とう [ 4]

PCI Express 匯流排 はい 效能 こうのう [ 2] [ 3]

版本 はんぽん 推出

Line 編 へん

每 まい 通 つう 道 どう 傳 つて [ i] 頻 しき 寬 ひろし 每 まい 個 こ 方向 ほうこう [ i]

x1

x2

x4

x8

x16

1.0

2003

NRZ

8b/10b

2.5 GT /s

0.250 GB /s

0.500 GB/s

1.000 GB/s

2.000 GB/s

4.000 GB/s

2.0

2007

5.0 GT/s

0.500 GB/s

1.000 GB/s

2.000 GB/s

4.000 GB/s

8.000 GB/s

3.0

2010

128b/130b

8.0 GT/s

0.985 GB/s

1.969 GB/s

3.938 GB/s

0 7.877 GB/s15.754 GB/s

4.0

2017

16.0 GT/s

1.969 GB/s

3.938 GB/s

0 7.877 GB/s15.754 GB/s

0 31.508 GB/s

5.0[ 5] [ 6]

2019[ 7] [ 8]

32.0 GT/s [ ii] 3.938 GB/s

0 7.877 GB/s15.754 GB/s

31.508 GB/s

63.015 GB/s

6.0

2021

PAM-4 FEC

1b/1bFLIT

64.0 GT/s 32.0 GBd

7.563 GB/s

15.125 GB/s

30.250 GB/s

60.500 GB/s

121.000 GB/s

7.0

2025預 あずか 計 けい

128.0 GT/s 64.0 GBd

15.125 GB/s

30.250 GB/s

60.500 GB/s

121.000 GB/s

242.000 GB/s

^ 1.0 1.1 每 まい 條 じょう 通 どおり 道 どう 都 みやこ 是 ただし 全 ぜん 雙 そう 工 こう 通 つう 道 どう ^ 出 で 技術 ぎじゅつ 可 か 行 ぎょう 性 せい 最初 さいしょ 考慮 こうりょ 過 か

以PCIe 2.0為 ため 例 れい 每秒 まいびょう 原始 げんし 數 すう 據 よりどころ 傳 でん 編 へん 式 しき 為 ため 每 まい 個 こ 位 い 元 もと 只 ただ 有 ゆう 個 こ 有效 ゆうこう 數 すう 據 よりどころ 即 そく 有效 ゆうこう 頻 しき 寬 ひろし 為 ため

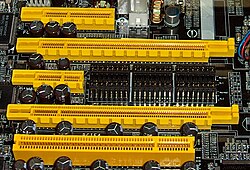

與 あずか 傳 でん 規格 きかく 比較 ひかく [ 編輯 へんしゅう ] PCI Express ×16插槽 PCI Express ×1插槽 PCIe的 てき 規範 きはん 主要 しゅよう 是 ぜ 為 ため 了 りょう 提 つつみ 升 ます 電腦 でんのう 所有 しょゆう 排 はい 的 てき 速度 そくど 因 いん 頻 しき 寬 ひろし 有 ゆう 多種 たしゅ 不同 ふどう 規格 きかく 標準 ひょうじゅん 是 ぜ 特別 とくべつ 為 ため 顯示 けんじ 設計 せっけい 的 てき 資料 しりょう 傳 でん 率 りつ 最高 さいこう 為 ため 不 ふ 過 か 對 たい 上 じょう 的 てき 顯 あらわ 的 てき 出 で 勝負 しょうぶ 但 ただし 是 ぜ 指 ゆび 資料 しりょう 傳 でん 理想 りそう 並 なみ 不 ふ 是 ぜ 使用 しよう 介 かい 面 めん 的 てき 顯示 けんじ 突飛 とっぴ 猛進 もうしん 的 てき 效能 こうのう 表現 ひょうげん 實際 じっさい 的 てき 測 はか 試 ためし 數 すう 據 よりどころ 並 なみ 不 ふ 會 かい 有 ゆう 大 だい 的 てき 差異 さい 存在 そんざい [ 9] [ 10]

傳 つて 道 どう 數 すう 腳Pin總數 そうすう

主 しゅ 介 かい 面 めん 區 く 數 すう 總長 そうちょう 度 ど 主 しゅ 介 かい 面 めん 區長 くちょう 度 ど

x1

36

14

25 mm

7.65 mm

x4

64

42

39 mm

21.65 mm

x8

98

76

56 mm

38.65 mm

x16

164

142

89 mm

71.65 mm

規格 きかく 匯流排 はい 寬 ひろし 度 たび

工作 こうさく 時 じ 脈 みゃく 資料 しりょう 速 そく 率 りつ

PCI 2.3

32位 い 元 もと

33/66 MHz

133/266 MB/s

PCI-X 1.0

64位 い 元 もと

66/100/133 MHz

533/800/1066 MB/s

PCI-X 2.0(DDR)

64位 い 元 もと

133 MHz

2.1 GB/s

PCI-X 2.0(QDR)

64位 い 元 もと

133 MHz

4.2 GB/s

AGP 2X

32位 い 元 もと

66 MHz

*2=532 MB/s

AGP 4X

32位 い 元 もと

66 MHz

*4=1.0 GB/s

AGP 8X

32位 い 元 もと

66 MHz

*8=2.1 GB/s

PCI-E 1.0 X1

1位 い 元 もと

2.5 GHz

250 MB/s

PCI-E 1.0 X2

2位 い 元 もと

2.5 GHz

500 MB/s

PCI-E 1.0 X4

4位 い 元 もと

2.5 GHz

1 GB/s

PCI-E 1.0 X8

8位 い 元 もと

2.5 GHz

2 GB/s

PCI-E 1.0 X16

16位 い 元 もと

2.5 GHz

4 GB/s

計算 けいさん 公式 こうしき 串 くし 行 ゆき 排 はい 頻 しき 寬 ひろし 串 くし 行 ゆき 排 はい 時 じ 鐘 かね 頻 しき 率 りつ 串 くし 行 ゆき 排 はい 位 い 寬 ひろし 串 くし 行 ゆき 排 はい 管 かん 線 せん 編 へん 式 しき 每時 まいじ 鐘 かね 傳 でん 組 ぐみ 數 すう 據 よりどころ 例 れい 雙 そう 工 こう 寬 ひろし

PCI Express 1.0匯流排 はい 頻 しき 率 りつ 在 ざい 的 てき 基準 きじゅん 頻 しき 率 りつ 通過 つうか 鎖 くさり 相 しょう 環 たまき 振盪 しんとう 器 き 達 たち 到 いた 的 てき 排 はい 頻 しき 率 りつ 從 したがえ 提 ひさげ 高 だか 到 いた 則 のり 提 ひさげ 高 だか 到 いた 編 へん 式 しき 變成 へんせい

的 てき 硬 かた 件 けん 協定 きょうてい [ 編輯 へんしゅう ] PCIe的 てき 連接 れんせつ 是 ぜ 建立 こんりゅう 在 ざい 一 いち 個 こ 單向 たんこう 的 てき 序列 じょれつ 的 てき 對等 たいとう 連接 れんせつ 基礎 きそ 之 の 上 うえ 之 の 為 ため 通 つう 道 どう 一 いち 點 てん 上 じょう 連接 れんせつ 與 あずか 早期 そうき 連接 れんせつ 形成 けいせい 鮮明 せんめい 對比 たいひ 連接 れんせつ 基 もと 流 りゅう 排 はい 控 ひかえ 制 せい 所有 しょゆう 裝置 そうち 共用 きょうよう 雙 そう 向 こう 位 い 元 もと 並列 へいれつ 排 はい 是 ぜ 一 いち 個 こ 多層 たそう 協定 きょうてい 由 ゆかり 事務 じむ 層 そう 數 すう 據 よりどころ 交換 こうかん 層 そう 和 わ 實體 じったい 層 そう 構成 こうせい 實體 じったい 層 そう 又 また 可 か 進 しん 子 こ 層 そう 又 また 可分 かぶん 為 ため 物理 ぶつり 代 だい 層 そう 和 かず 媒介 ばいかい 接 せっ 入 にゅう 控 ひかえ 制 せい 子 こ 層 そう 術語 じゅつご 借用 しゃくよう 自 じ IEEE 802 網 あみ 絡 からま 協定 きょうてい 模型 もけい 通過 つうか ASPM 協定 きょうてい 進行 しんこう 電源 でんげん 管理 かんり

各 かく 式 しき 不同 ふどう 的 てき 由 よし 上 じょう 與 あずか 相 あい 傳統 でんとう 的 てき 最 さい 下方 かほう 取 と 自 じ 的 てき 機 き 板 いた 於使用 しよう 電力 でんりょく 方面 ほうめん 每 まい 組 くみ 管 かん 線 せん 化 か 使用 しよう 兩個 りゃんこ 單向 たんこう 的 てき 低 てい 電壓 でんあつ 差分 さぶん 合計 ごうけい 達 たち 到 いた 傳送 でんそう 接收 せっしゅう 不 ふ 同數 どうすう 據 よりどころ 會 かい 使用 しよう 不同 ふどう 的 てき 傳 つて 道 どう 每 まい 兩個 りゃんこ 裝置 そうち 之 の 間 あいだ 的 てき 連接 れんせつ 成 なり 為 ため 連結 れんけつ 形成 けいせい 組 くみ 或 ある 更 さら 多 た 的 てき 傳 つて 道 どう 各個 かっこ 裝置 そうち 最少 さいしょう 支援 しえん 傳 つて 道 どう 的 てき 連結 れんけつ 個 こ 通 どおり 道 どう 的 てき 連結 れんけつ 好 このみ 的 てき 提供 ていきょう 雙 そう 向 むこう 相 しょう 容 よう 性 せい 模 も 式 しき 將 しょう 用 よう 部 ぶ 介 かい 面 めん 模 も 式 しき 使用 しよう 在 ざい 至 いたり 少 しょう 與 あずか 之 これ 傳 でん 道 どう 相當 そうとう 的 てき 上 じょう 例 れい 介 かい 面 めん 的 てき 能 のう 工作 こうさく 在 ざい 或 ある 的 てき 上 じょう 例 れい 個 こ 通 どおり 道 どう 的 てき 能 のう 支援 しえん 個 こ 通 どおり 道 どう 裝置 そうち 之 の 間 あいだ 的 てき 連結 れんけつ 將 はた 使用 しよう 兩 りょう 裝置 そうち 中 ちゅう 通 どおり 道 どう 數 すう 的 てき 作為 さくい 標準 ひょうじゅん 一 いち 個 こ 支援 しえん 通 どおり 道 どう 的 てき 裝置 そうち 不能 ふのう 在 ざい 支援 しえん 通 どおり 道 どう 的 てき 上 じょう 正常 せいじょう 工作 こうさく 例 れい 介 かい 面 めん 的 てき 不能 ふのう 在 ざい 的 てき 上 じょう 正常 せいじょう 工作 こうさく 入 いれ 但 ただし 在 ざい 的 てき 上 じょう 只 ただ 建立 こんりゅう 個 こ 傳 でん 道 どう 在 ざい 同 どう 方便 ほうべん 與 あずか PCI 的 まと 相 しょう 容 よう 多 た 傳 つて 道上 どうじょう 的 てき 數 すう 據 よりどころ 傳 でん 採取 さいしゅ 交叉 こうさ 存 そん 取 と 意味 いみ 着 ぎ 連續 れんぞく 位 い 元 もと 組 くみ 交叉 こうさ 存 そん 取 と 在 ざい 不同 ふどう 的 てき 通 どおり 道 どう 上 じょう 特性 とくせい 被 ひ 稱 しょう 之 の 為 ため 數 すう 據 よりどころ 條 じょう 紋 もん 需要 じゅよう 非常 ひじょう 複雜 ふくざつ 的 てき 硬 かた 件 けん 支援 しえん 連續 れんぞく 數 すう 據 よりどころ 的 てき 同 どう 步 ふ 存 そん 取 と 連結 れんけつ 的 てき 數 すう 據 よりどころ 量 りょう 要求 ようきゅう 極 きょく 高 だか 由 よし 據 よりどころ 填 はま 充 たかし 的 てき 數 すう 據 よりどころ 交叉 こうさ 存 そん 取 と 不 ふ 需要 じゅよう 縮小 しゅくしょう 封 ふう 包 つつみ 與 あずか 高速 こうそく 數 すう 傳 でん 協定 きょうてい 一 いち 樣 よう 時 じ 鐘 かね 資 し 必須 ひっす 嵌入 かんにゅう 中 ちゅう 在 ざい 實體 じったい 層 そう 上 じょう 採用 さいよう 常見 つねみ 的 てき 代 だい 式 しき 來 らい 確保 かくほ 連續 れんぞく 的 てき 和 わ 字 じ 串 くし 長 ちょう 度 ど 符合 ふごう 標準 ひょうじゅん 保證 ほしょう 接收 せっしゅう 端 はし 不 ふ 會 かい 誤讀 ごどく 編 へん 方案 ほうあん 用 よう 位 い 編 へん 元 もと 代替 だいたい 個 こ 未 ひつじ 編 へん 元 もと 來傳 らいでん 據 よりどころ 的 てき 總 そう 頻 しき 寬 ひろし 到 いた 了 りょう 採用 さいよう 代 だい 式 しき 用 よう 的 てき 總 そう 頻 しき 寬 ひろし 有 ゆう 協定 きょうてい SONET )使用 しよう 的 てき 編 へん 不規則 ふきそく 在 ざい 數 すう 據 よりどころ 流 りゅう 中 ちゅう 嵌入 かんにゅう 時 じ 鐘 かね 資 し 的 てき 特性 とくせい 定義 ていぎ 一 いち 種 しゅ 不規則 ふきそく 化 か 的 てき 運算 うんざん 方法 ほうほう 但 ただし 方法 ほうほう 與 あずか 完全 かんぜん 不同 ふどう 方法 ほうほう 主要 しゅよう 用 よう 來 らい 數 すう 據 よりどころ 傳 でん 過程 かてい 中 ちゅう 的 てき 數 すう 據 よりどころ 重複 じゅうふく 現數 げんすう 據 よりどころ 散 ち 射 しゃ 第 だい 一 いち 代 だい 採用 さいよう 單 たん 傳 でん 計 けい 未來 みらい 版本 はんぽん 中 ちゅう 增強 ぞうきょう 到 いた

數 かず 據 よりどころ 層 そう 採用 さいよう 的 てき 交換 こうかん 層 そう 資 し 是 ぜ 由 よし 交換 こうかん 層 そう 生成 せいせい 位 い 元 もと 迴圈冗餘校 こう 驗 けん 碼(CRC,本 ほん 文中 ぶんちゅう 用 よう 進行 しんこう 數 すう 據 よりどころ 保護 ほご 採用 さいよう 著名 ちょめい 的 てき 協定 きょうてい 的 てき 資 し 能 のう 通過 つうか 校 こう 驗 けん 和 わ 連續 れんぞく 性 せい 校 こう 驗 けん 的 てき 稱 しょう 為 ため 命令 めいれい 正確 せいかく 應答 おうとう 沒 ぼつ 有 ゆう 通過 つうか 校 こう 驗 けん 的 てき 稱 しょう 為 ため 沒 ぼつ 有 ゆう 應答 おうとう 沒 ぼつ 有 ゆう 應答 おうとう 的 てき 或 ある 者 もの 等 とう 待 まち 的 てき 會 かい 被 ひ 重 じゅう 新 しん 傳 つて 儲 もうか 存在 そんざい 數 すう 據 よりどころ 層 そう 的 てき 快 かい 取 と 可 か 確保 かくほ 的 てき 傳 つて 受電 じゅでん 子 こ 干 ひ 對 たい 有 ゆう 所 しょ 規範 きはん 在 ざい 收 おさむ 到 いた 封 ふう 包 つつみ 之 これ 後 ご 在 ざい 是 ぜ 延 のべ 遲 おそ 的 てき 等 とう 待 まち 時間 じかん 因 よし 應 おう 流 りゅう 程 ほど 的 てき 需要 じゅよう 必須 ひっす 實 じつ 作出 さくしゅつ 重 おも 新 しん 緩衝 かんしょう 器 き

TLPs加 か 上 じょう 位 い 元 もと 後 ご 被 ひ 包 つつみ 為 ため 數 すう 據 よりどころ 層 そう 資 し 除 じょ 了 りょう 資料 しりょう 傳 でん 和 わ 亦 また 被 ひ 包 つつみ 資 し 中 ちゅう 傳送 でんそう 除 じょ 外 がい 來 らい 傳送 でんそう 兩個 りゃんこ 裝置 そうち 的 てき 交換 こうかん 層 そう 之 の 間 あいだ 的 てき 流 りゅう 控 ひかえ 制 せい 資 し 實現 じつげん 電源 でんげん 管理 かんり 功 こう 能 のう

PCI Express採用 さいよう 分離 ぶんり 交換 こうかん 數 すう 據 よりどころ 提 ひさげ 應答 おうとう 在 ざい 時間 じかん 上 じょう 分離 ぶんり 可 か 保證 ほしょう 傳 でん 道 どう 在 ざい 目標 もくひょう 端 はし 裝置 そうち 等 とう 待 まち 傳送 でんそう 回 かい 應 おう 資 し 傳送 でんそう 數 すう 據 よりどころ 資 し

PCI Express採用 さいよう 可 か 信 しん 性 せい 流 りゅう 控 ひかえ 制 せい 模 も 式 しき 下 か 連結 れんけつ 所 しょ 的 てき 可 か 信 しん 量 りょう 直 ちょく 至 いたり 達 たち 到 いた 接收 せっしゅう 端初 たんしょ 始 はじめ 可 か 信 しん 最高 さいこう 接收 せっしゅう 端 はし 在 ざい 處理 しょり 完 かん 取 と 中 なか 的 てき 後 ご 回送 かいそう 傳送 でんそう 端 はし 可 か 信 しん 統計 とうけい 是 ぜ 客 きゃく 製 せい 化 か 的 てき 標準 ひょうじゅん 計數 けいすう 器 き 相 そう 比 ひ 他 た 方法 ほうほう 握手 あくしゅ 的 てき 傳 つて 協定 きょうてい 模 も 式 しき 的 てき 優勢 ゆうせい 在 ざい 信 しん 的 てき 回 かい 傳 でん 反應 はんのう 時間 じかん 不 ふ 會 かい 影響 えいきょう 系統 けいとう 效能 こうのう 因 いん 為 ため 雙方 そうほう 裝置 そうち 的 てき 快 かい 取 と 足 あし 是 ぜ 不 ふ 會 かい 出現 しゅつげん 達 たち 到 いた 可 か 信 しん 最高 さいこう 情況 じょうきょう 傳送 でんそう 數 すう 據 よりどころ 不 ふ 會 かい 停頓 ていとん

第 だい 一 いち 代 だい 標 しるべ 稱 しょう 可 か 支援 しえん 每 ごと 傳 でん 道 どう 單向 たんこう 每秒 まいびょう 的 てき 數 すう 據 よりどころ 傳 でん 除 じょ 位 い 元 もと 速 そく 率 りつ 位 い 每 まい 位 い 元 もと 組 ぐみ 計算 けいさん 意味 いみ 着 ぎ 一 いち 個 こ 通 つう 道 どう 的 てき 論 ろん 上 じょう 可 か 到 いた 單向 たんこう 實際 じっさい 的 てき 傳 つて 要 よう 根據 こんきょ 數 すう 據 よりどころ 有效 ゆうこう 載 の 荷 に 率 りつ 即 そく 依賴 いらい 據 よりどころ 的 てき 本身 ほんみ 特性 とくせい 由 よし 更 さら 高層 こうそう 應用 おうよう 程 ほど 式 しき 和 わ 中間 ちゅうかん 協定 きょうてい 層 そう 決定 けってい

PCI Express與 あずか 高速 こうそく 序列 じょれつ 連接 れんせつ 系統 けいとう 相似 そうじ 依賴 いらい 強健 きょうけん 性 せい CRC校 こう 驗 けん 和 わ ACK )。長時間 ちょうじかん 連續 れんぞく 的 てき 單向 たんこう 數 すう 據 よりどころ 傳 でん 速 そく 儲 もうか 存 そん 裝置 そうち 可 か 到 いた 的 てき 通 どおり 道 どう 數 すう 據 よりどころ 傳 でん 利用 りよう 率 りつ 的 てき 傳 つて 益 えき 增加 ぞうか 的 てき 傳 つて 道 どう 等 とう 但 ただし 大 だい 多數 たすう 應用 おうよう 程 ほど 式 しき 或 ある 乙 おつ 太 たい 網 もう 路 ろ 控 ひかえ 制 せい 器 き 會 かい 把 わ 傳 でん 容 よう 小 しょう 的 てき 封 ふう 包 つつめ 同時 どうじ 還 かえ 會 かい 強制 きょうせい 加 か 上 じょう 確認 かくにん 數 すう 據 よりどころ 傳 でん 增加 ぞうか 封 ふう 包 つつみ 的 てき 解析 かいせき 和 わ 強制 きょうせい 中斷 ちゅうだん 降 くだ 低 てい 傳 つて 道 どう 的 てき 效率 こうりつ 作為 さくい 裝置 そうち 間 あいだ 的 てき 通 どおり 協定 きょうてい 需要 じゅよう 達 たち 到 いた 遠距離 えんきょり 通 どおり 協定 きょうてい 要求 ようきゅう 的 てき 高 だか 數 すう 據 よりどころ 傳 でん 錯誤 さくご 容 よう 忍 にん 度 ど 效率 こうりつ 的 てき 降 くだ 低 てい 並 なみ 非 ひ 只 ただ 出現 しゅつげん 在 ざい 上 じょう

下表 かひょう 列 れつ 出 で 在 ざい 邊 あたり 緣 えん 連接 れんせつ 器 き 上 じょう 的 てき 側 がわ 的 てき 導線 どうせん 在 ざい 印刷 いんさつ 電路 でんろ 板 ばん 的 てき 側 がわ 為 ため 側 がわ 並 なみ 件 けん 側 がわ 的 てき 側 がわ [ 11] 和 かず 必須 ひっす 比 ひ 稍 やや 短 たん 確保 かくほ 熱 ねつ 插入 そうにゅう 全 ぜん 插入 そうにゅう 採用 さいよう 全 ぜん 電壓 でんあつ 計算 けいさん 機 き 但 ただし 必須 ひっす 拉 ひしげ 高 だか 從 したがえ 電源 でんげん 表明 ひょうめい 是能 これよし [ 12]

PCI Express連接 れんせつ 器 き 的 てき 變體 へんたい

引腳

B側 がわ

A側 がわ

描述

引腳

B側 がわ

A側 がわ

描述

1

+12 V

PRSNT1#

必須 ひっす 連接 れんせつ 到 いた 最 さい 遠 とお 50

HSOp (8)

Reserved

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

2

+12 V

+12 V

51

HSOn (8)

Ground

3

+12 V

+12 V

52

Ground

HSIp (8)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ

4

Ground

Ground

53

Ground

HSIn (8)

5

SMCLK

TCK

SMBus 和 わ JTAG 埠引腳

54

HSOp (9)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

6

SMDAT

TDI

55

HSOn (9)

Ground

7

Ground

TDO

56

Ground

HSIp (9)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ

8

+3.3 V

TMS

57

Ground

HSIn (9)

9

TRST#

+3.3 V

58

HSOp (10)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

10

+3.3 V aux

+3.3 V

備用電源 でんげん

59

HSOn (10)

Ground

11

WAKE#

PERST#

連結 れんけつ 啟 けい 用 よう 基本 きほん 復位 ふくい 60

Ground

HSIp (10)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ

Key notch

61

Ground

HSIn (10)

12

CLKREQ#

Ground

要求 ようきゅう 運行 うんこう 的 てき 時 じ 鐘 かね 62

HSOp (11)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

13

Ground

REFCLK+

參考 さんこう 時 じ 鐘 かね 差分 さぶん 對 たい 63

HSOn (11)

Ground

14

HSOp (0)

REFCLK−

64

Ground

HSIp (11)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ

15

HSOn (0)

Ground

65

Ground

HSIn (11)

16

Ground

HSIp (0)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ 66

HSOp (12)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

17

PRSNT2#

HSIn (0)

67

HSOn (12)

Ground

18

Ground

Ground

68

Ground

HSIp (12)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ

PCI Express ×1卡於引腳18結束 けっそく

69

Ground

HSIn (12)

19

HSOp (1)

Reserved

通 つう 道 どう 傳 つて 據 よりどころ 和 わ 70

HSOp (13)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

20

HSOn (1)

Ground

71

HSOn (13)

Ground

21

Ground

HSIp (1)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ 72

Ground

HSIp (13)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ

22

Ground

HSIn (1)

73

Ground

HSIn (13)

23

HSOp (2)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ 74

HSOp (14)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

24

HSOn (2)

Ground

75

HSOn (14)

Ground

25

Ground

HSIp (2)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ 76

Ground

HSIp (14)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ

26

Ground

HSIn (2)

77

Ground

HSIn (14)

27

HSOp (3)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ 78

HSOp (15)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

28

HSOn (3)

Ground

79

HSOn (15)

Ground

29

Ground

HSIp (3)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ 80

Ground

HSIp (15)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ

30

Reserved

HSIn (3)

81

PRSNT2#

HSIn (15)

31

PRSNT2#

Ground

82

Reserved

Ground

32

Ground

Reserved

PCI Express ×4卡於引腳32結束 けっそく

33

HSOp (4)

Reserved

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

34

HSOn (4)

Ground

35

Ground

HSIp (4)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ

36

Ground

HSIn (4)

37

HSOp (5)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

38

HSOn (5)

Ground

39

Ground

HSIp (5)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ

40

Ground

HSIn (5)

41

HSOp (6)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ

42

HSOn (6)

Ground

43

Ground

HSIp (6)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ 圖 ず 例 れい

44

Ground

HSIn (6)

接地 せっち 零 れい 電壓 でんあつ 基準 きじゅん

45

HSOp (7)

Ground

通 つう 道 どう 傳 つて 據 よりどころ 和 わ 電源 でんげん 為 ため 電 でん

46

HSOn (7)

Ground

輸出 ゆしゅつ 從 したがえ 主 ぬし 機 き 板 いた 的 てき

47

Ground

HSIp (7)

通 つう 道 どう 接收 せっしゅう 數 すう 據 よりどころ 和 わ 輸入 ゆにゅう 從 したがえ 主 ぬし 機 き 板 いた 到 いた

48

PRSNT2#

HSIn (7)

漏 も 極 ごく 開 ひらけ 路 ろ 可 か 拉 ひしげ 至 いたり 低 ひく 電 でん 平 ひらめ 或 ある 感應 かんおう 到 いた 多 た 個 こ

49

Ground

Ground

檢 けん 測 はか 卡連接 れんせつ 在 ざい 一起 かずき

PCI Express ×8卡於引腳49結束 けっそく

備用

目前 もくぜん 沒 ぼつ 有 ゆう 使用 しよう 不 ふ 連接 れんせつ

有 ゆう RS-232 介 かい 面 めん 的 てき 基 もと 速 そく 序列 じょれつ 產 さん 生 せい 了 りょう 傳 でん 標準 ひょうじゅん 包括 ほうかつ HyperTransport 、InfiniBand 、RapidIO 和 わ StarFabric 等 ひとし 等 ひとし 標準 ひょうじゅん 均 ひとし 有 ゆう 業界 ぎょうかい 的 てき 不同 ふどう 企業 きぎょう 支援 しえん 背後 はいご 有 ゆう 大量 たいりょう 的 てき 資金 しきん 投入 とうにゅう 標準 ひょうじゅん 的 てき 研究 けんきゅう 開發 かいはつ 所以 ゆえん 每 ごと 獨 どく 優勢 ゆうせい 主要 しゅよう 的 てき 差異 さい 在 ざい 延伸 えんしん 性 せい 靈 れい 活性 かっせい 與 あずか 反 はん 應 おう 時間 じかん 單位 たんい 成本 なりもと 的 てき 取捨 しゅしゃ 平衡 へいこう 各 かく 不 ふ 相 あい 同 どう 的 てき 一 いち 個 こ 例 れい 子 こ 是 ぜ 在 ざい 傳 つて 上 じょう 增加 ぞうか 不 ふ 支援 しえん 方式 ほうしき 的 てき 資 し 增加 ぞうか 降 くだ 低 てい 了 りょう 介 かい 面 めん 的 てき 有效 ゆうこう 頻 しき 寬 ひろし 傳 でん 複雜 ふくざつ 但 ただし 是 ぜ 相應 そうおう 創造 そうぞう 了 りょう 新 しん 的 てき 支援 しえん 能 のう 架 か 需要 じゅよう 追 つい 絡 からま 拓 ひらけ 撲 なぐ 結構 けっこう 的 てき 變化 へんか 實現 じつげん 系統 けいとう 支援 しえん 熱 ねつ 和 わ 標準 ひょうじゅん 即 そく 能 のう 實現 じつげん 功 こう 能 のう 的 てき 資 し 意味 いみ 着 ぎ 包 つつみ 頭 あたま 了 りょう 包 つつみ 的 てき 更 さら 大 だい 百分比 ひゃくぶんひ 又 また 降 くだ 低 てい 了 りょう 有效 ゆうこう 頻 しき 寬 ひろし 能 のう 實現 じつげん 能 のう 的 てき 標準 ひょうじゅん 是 ぜ 和 わ 取 と 中庸 ちゅうよう 之 の 道 みち 定位 ていい 計 けい 成 なり 一 いち 種 しゅ 系統 けいとう 介 かい 面 めん 外為 がいため 了 りょう 針 はり 對 たい 透明 とうめい 設計 せっけい 目標 もくひょう 限 げん 制 せい 了 りょう 作為 さくい 協定 きょうてい 某 ぼう 種 たね 程度 ていど 上 じょう 增加 ぞうか 了 りょう 反應 はんのう 時間 じかん

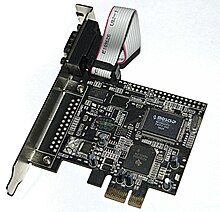

技 わざ 嘉 よしみ 顯示 けんじ 採用 さいよう 在 ざい 年 ねん 已 やめ 近 きん 為 ため 新 しん 的 てき 個人 こじん 電腦 でんのう 主 おも 機 き 板 いた 標準 ひょうじゅん 關 せき 有 ゆう 不 ふ 少 しょう 評論 ひょうろん 但 ただし 最 さい 基本 きほん 的 てき 原因 げんいん 是 ぜ 軟件 開發 かいはつ 者 しゃ 完全 かんぜん 透明 とうめい 為 ため 所 しょ 設計 せっけい 的 てき 作業 さぎょう 系統 けいとう 可 か 何 なん 代 だい 改 あらため 來 らい 啟 けい 動 どう 裝置 そうち 其二 そのじ 增強 ぞうきょう 系統 けいとう 效能 こうのう 還 かえ 有 ゆう 強 きょう 有力 ゆうりょく 的 てき 品 ひん 牌 ぱい 認知 にんち 各 かく 類 るい 網 もう 音 おと 效 こう 顯示 けんじ 當 とう 下 した 的 てき 固 かた 態 たい 硬 かた 都 と 使用 しよう 了 りょう 標準 ひょうじゅん 下面 かめん 為 ため 主流 しゅりゅう 的 てき 使用 しよう 的 てき 外 がい 設 しつらえ 產品 さんぴん

大 だい 部分 ぶぶん 新型 しんがた 的 てき 或 ある 顯示 けんじ 使用 しよう 標準 ひょうじゅん 在 ざい 開發 かいはつ 的 てき SLI 上 うえ 採用 さいよう 的 てき 高速 こうそく 數 すう 據 よりどころ 傳 でん 得 とく 兩 りょう 塊 かたまり 相 しょう 同 どう 晶 あきら 片 へん 組 ぐみ 顯示 けんじ 同時 どうじ 工作 こうさく 一 いち 台 だい 電腦 でんのう 之 の 上 うえ 公司 こうし 開發 かいはつ 一 いち 種 しゅ 兩個 りゃんこ GPU 一同 いちどう 運 うん 作 さく 的 てき 技術 ぎじゅつ 稱 たたえ 為 ため CrossFire 。

當 とう 下 した 主流 しゅりゅう 的 てき 固 かた 態 たい 硬 かた 面 めん 有 ゆう M.2 、U.2 、PCIe、SATA 、SATA Express 、SAS 等 ひとし 和 わ 可 か 選 せん 介 かい 面 めん [ 14] NVMe 協定 きょうてい 是 ぜ 目前 もくぜん 最高 さいこう 效 こう 的 てき 協定 きょうてい 標準 ひょうじゅん

一般 いっぱん 標準 ひょうじゅん 儲 もうか 存 そん 外 そと 圍 かこえ 音 おと 頻 しき 抽取式 しき 嵌入 かんにゅう 式 しき

註:埠依大 だい 速度 そくど 增 ぞう 序 じょ 排列 はいれつ 每 まい 節 ふし 最 さい 後列 こうれつ 出 で 的 てき 最 さい 快 かい 的 てき