電子 でんし 部品 ぶひん パッケージ (外周 がいしゅう 器 き 電気 でんき 製品 せいひん 構成 こうせい 個別 こべつ 部品 ぶひん 外形 がいけい 構成 こうせい 部分 ぶぶん 通常 つうじょう 小 ちい 電子 でんし 部品 ぶひん 包 つつ 合成 ごうせい 樹脂 じゅし 金属 きんぞく セラミック を指 さ

1mm方眼 ほうがん 紙上 しじょう 抵抗 ていこう アキシャル リード電解 でんかい コンデンサ 電子 でんし 部品 ぶひん 収 おさ 機能 きのう 要求 ようきゅう 次 つぎ

中 なか 素子 そし 外部 がいぶ 衝撃 しょうげき 湿度 しつど 熱 ねつ 光線 こうせん 守 まも 接続 せつぞく 端子 たんし 保持 ほじ 外部 がいぶ 間 あいだ 正 まさ 信号 しんごう 電源 でんげん 伝 つた 製品 せいひん 組 く 立 た 適 てき 形状 けいじょう 内部 ないぶ 発生 はっせい 熱 ねつ 速 すみ 放熱 ほうねつ [注 ちゅう コストが安 やす

電子 でんし 部品 ぶひん 機能 きのう 検査 けんさ 製造 せいぞう 社名 しゃめい 製品 せいひん 型番 かたばん 製造 せいぞう 番号 ばんごう 番号 ばんごう 表示 ひょうじ 保持 ほじ 可能 かのう 限 かぎ 正規 せいき 製品 せいひん 類似 るいじ 製品 せいひん 区別 くべつ 示 しめ 環境 かんきょう 問題 もんだい 対応 たいおう [注 ちゅう また、デジタル半導体 はんどうたい 代表 だいひょう 高性能 こうせいのう 電子 でんし 部品 ぶひん 多 おお 動作 どうさ 周波数 しゅうはすう 高 たか 消費 しょうひ 電流 でんりゅう 大 おお 寄生 きせい 容量 ようりょう 電流 でんりゅう 抵抗 ていこう 小 ちい 短 みじか 太 ふと 接続 せつぞく 端子 たんし 放熱 ほうねつ 性 せい 良 よ 求 もと [注 ちゅう 携帯 けいたい 機器 きき 使用 しよう 部品 ぶひん 小型 こがた 化 か 求 もと

アキシャル 部品 ぶひん ラジアル 部品 ぶひん 形態 けいたい 部品 ぶひん リード 部品 ぶひん 呼 よ 抵抗 ていこう 抵抗 ていこう 器 き コンデンサ (キャパシタ)、コイル 、小型 こがた トランス 等 ひとし 個別 こべつ 受動 じゅどう 部品 ぶひん 呼 よ 半導体 はんどうたい 部品 ぶひん 単品 たんぴん ダイオード もパッケージ形態 けいたい 見 み 抵抗 ていこう 等 とう 同 おな 部品 ぶひん 形態 けいたい 多 おお

1990年代 ねんだい プリント基板 きばん 上 うえ 表面 ひょうめん 実装 じっそう チップ部品 ぶひん の使用 しよう 増 ふ 始 はじ 年 ねん 現在 げんざい 部品 ぶひん 部品 ぶひん 形態 けいたい 減 へ アキシャル (axial)と、ラジアル (radial)は、リード (導 みちび 線 せん 取 と 付 つ 方向 ほうこう 違 ちが 表 あらわ 個別 こべつ 受動 じゅどう 部品 ぶひん 場合 ばあい 表面 ひょうめん 実装 じっそう 用 よう 部品 ぶひん 専用 せんよう 形状 けいじょう 多 おお 中 なか 型 がた 部品 ぶひん 短 みじか [注 ちゅう

電気 でんき 的 てき 接続 せつぞく 銅板 どうばん エッチング したリードフレームとともにチップを封 ふう 止 よ 端子 たんし 形 がた 挿入 そうにゅう 形 がた 一般 いっぱん 的 てき 年代 ねんだい 後半 こうはん 以降 いこう 基板 きばん 穴 あな 通 とお 基板 きばん 表面 ひょうめん 片面 かためん はんだ付 づ する表面 ひょうめん 実装 じっそう 方式 ほうしき 導入 どうにゅう 現在 げんざい 至 いた 広 ひろ 普及 ふきゅう 時代 じだい 進 すす 端子 たんし 数 かず 集積 しゅうせき 度 ど 上昇 じょうしょう 素子 そし 多 た 機能 きのう 化 か 大 おお 増加 ぞうか 従来 じゅうらい 対応 たいおう 製品 せいひん 増 ふ 端子 たんし 微小 びしょう 化 か 底面 ていめん 丸 まる 格子 こうし 状 じょう 並 なら 剣山 けんざん ピン を Grid=格子 こうし 状 じょう 配置 はいち 導入 どうにゅう 大 だい 規模 きぼ 外部 がいぶ 接続 せつぞく 数 すう 千 せん 及 およ 端子 たんし 密度 みつど 高 たか 必要 ひつよう 交換 こうかん 可能 かのう 性 せい 部品 ぶひん 実装 じっそう

過去 かこ 上 じょう 他 た 載 の 不揮発 ふきはつ 性 せい 内蔵 ないぞう CPU などで、ソフト開発 かいはつ 時 じ 交換 こうかん 容易 ようい 目的 もくてき 使用 しよう 年代 ねんだい 普及 ふきゅう 紫外線 しがいせん 照射 しょうしゃ 記憶 きおく 内容 ないよう 消去 しょうきょ UV-EPROM というメモリ半導体 はんどうたい 石英 せきえい 窓 まど 付 つ ICカード などの内部 ないぶ 情報 じょうほう 読 よ 取 と 耐 たい 性 せい 要 よう 用途 ようと 向 む 半導体 はんどうたい 部品 ぶひん 半導体 はんどうたい 上 じょう ROM 、RAM などの必要 ひつよう 論理 ろんり 回路 かいろ 全 すべ 含 ふく 本 ほん 程度 ていど 外部 がいぶ 接続 せつぞく 端子 たんし 持 も 近年 きんねん 再来 さいらい 言 い 実装 じっそう 方法 ほうほう 普及 ふきゅう 始 はじ

半導体 はんどうたい 半導体 はんどうたい 外部 がいぶ 電気 でんき 的 てき 接続 せつぞく 端子 たんし 半導体 はんどうたい 搭載 とうさい 密封 みっぷう 保持 ほじ 封 ふう 止 とめ 材 ざい 分 わ 高 たか 信頼 しんらい 性 せい 長時間 ちょうじかん 維持 いじ 取 と 扱 あつか 低 てい 価格 かかく 製造 せいぞう 材料 ざいりょう 開発 かいはつ 努力 どりょく 続 つづ 年代 ねんだい 以降 いこう 有害 ゆうがい 物質 ぶっしつ 含 ふく 封 ふう 止 とめ 材 ざい 使用 しよう 鉛 なまり 有害 ゆうがい 物質 ぶっしつ 含 ふく はんだ で信頼 しんらい 性 せい 高 たか 接続 せつぞく 可能 かのう 求 もと 残存 ざんそん 有害 ゆうがい 物質 ぶっしつ 製造 せいぞう 工程 こうてい 有害 ゆうがい 物質 ぶっしつ 発生 はっせい 封 ふう 止 とめ 材料 ざいりょう 鉛 なまり 適 てき 特殊 とくしゅ 表面 ひょうめん 加工 かこう 端子 たんし 用 もち

外部 がいぶ 電気 でんき 的 てき 接続 せつぞく 行 おこな 端子 たんし 鉄 てつ 合金 ごうきん 使 つか 多 おお [注 ちゅう 銅 どう 用 もち 半球 はんきゅう 状 じょう 使 つか ソケット による実装 じっそう 想定 そうてい 製品 せいひん 高周波 こうしゅうは 扱 あつか 製品 せいひん 高 たか 信頼 しんらい 性 せい 求 もと 製品 せいひん 端子 たんし 金 きん 施 ほどこ 酸化 さんか 防止 ぼうし 浮遊 ふゆう 容量 ようりょう 低減 ていげん 図 はか 多 おお 以外 いがい 製品 せいひん 主 おも ニッケル合金 ごうきん やはんだでめっきをしており、これには酸化 さんか 防止 ぼうし 導通 どうつう 不良 ふりょう 低減 ていげん 加 くわ 性 せい 良 よ 効果 こうか 特殊 とくしゅ 場合 ばあい 除 のぞ 酸化 さんか 鉄 てつ 銅 どう 露出 ろしゅつ

ダイを載 の 端子 たんし 同時 どうじ プレス加工 かこう で作 つく 多 おお 固定 こてい 樹脂 じゅし 他 ほか 導通 どうつう 必要 ひつよう 場合 ばあい 銀 ぎん 粒子 りゅうし 含 ふく 樹脂 じゅし 放熱 ほうねつ 熱 ねつ 抵抗 ていこう 下 さ 必要 ひつよう 用 もち 端子 たんし ダイ を接続 せつぞく 金線 きんせん 線 せん 使 つか [1]

封 ふう 止 とめ 材 ざい 材質 ざいしつ 金属 きんぞく 鉄 てつ 真鍮 しんちゅう 用 もち 多 た 化 か 対応 たいおう 小型 こがた 化 か 要求 ようきゅう 出 で 通常 つうじょう 温度 おんど 湿度 しつど 範囲 はんい 使 つか エポキシ樹脂 じゅし など低 てい 価格 かかく 耐 たい 熱 ねつ 樹脂 じゅし 温度 おんど 特性 とくせい 広 ひろ 必要 ひつよう 工業 こうぎょう 用 よう 軍事 ぐんじ 用 よう 発熱 はつねつ 大 おお アルミナ などのセラミックが用 もち

金属 きんぞく 及 およ 焼 しょう 結 ゆい 成型 せいけい 内部 ないぶ 実装 じっそう 後 のち 組 く 立 た 低 てい 融点 ゆうてん 材 ざい 密封 みっぷう 一方 いっぽう 場合 ばあい 金 かね 型 がた 入 い 樹脂 じゅし 射出 しゃしゅつ 成形 せいけい 状 じょう 耐 たい 熱性 ねっせい 柔軟 じゅうなん 性 せい 高 たか ポリイミド で作 つく 上 じょう 実装 じっそう 近年 きんねん 性能 せいのう 上 あ 以外 いがい 表面 ひょうめん 実装 じっそう 部品 ぶひん リフローはんだ付 づ が出来 でき 使用 しよう 減少 げんしょう 傾向 けいこう ダイオード では当初 とうしょ 封 ふう 止 どめ 多 おお 使 つか 現在 げんざい 用途 ようと 使 つか 分 わ

レジンモールドはわずかながら水分 すいぶん 吸 す 付 づ 場合 ばあい 水分 すいぶん 含 ふく 急激 きゅうげき 加熱 かねつ 破壊 はかい 防 ふせ 納入 のうにゅう 部品 ぶひん 一定 いってい 個数 こすう 袋 ふくろ 密封 みっぷう 湿気 しっけ 遮断 しゃだん 開封 かいふう 部品 ぶひん 全 すべ 直 ただ 付 つ 限 かぎ 開封 かいふう 長時間 ちょうじかん 未 み 使用 しよう 部品 ぶひん 出 で 避 さ 部品 ぶひん 付 づ 判断 はんだん 出来 でき 表面 ひょうめん 実装 じっそう 用 よう 部品 ぶひん 開封 かいふう 後 ご 付 づ 時間 じかん 決 き 記載 きさい 過 す 部品 ぶひん 水分 すいぶん 取 と 除 のぞ 決 き 温度 おんど 予熱 よねつ 処理 しょり 付 つ

CPUやチップセット といった非常 ひじょう 多 おお 端子 たんし 必要 ひつよう 物 もの 内部 ないぶ 接続 せつぞく 使用 しよう フリップチップ (英語 えいご 版 ばん 接続 せつぞく 使用 しよう 使 つか 薄 うす 作 つく 上 じょう 製 せい 必要 ひつよう 使用 しよう 熱 ねつ 抵抗 ていこう 低 ひく 近年 きんねん 数 すう 多 おお 発熱 はつねつ 大 おお 製品 せいひん 使 つか 始 はじ 旧来 きゅうらい 金属 きんぞく 製 せい 製 せい 製品 せいひん 急速 きゅうそく 置 お 換 か 最大限 さいだいげん 上 あ 大 だい 容量 ようりょう DRAM 等 ひとし 直接 ちょくせつ 半田 はんだ 製品 せいひん

またフリップチップの登場 とうじょう 合 あ 従来 じゅうらい 丸 まる 覆 おお 上 うえ 搭載 とうさい インターポーザ 」が開発 かいはつ プリント基板 きばん の一種 いっしゅ 材料 ざいりょう 基板 きばん 同 おな ガラス繊維 せんい 入 はい エポキシ が使 つか 隙間 すきま アンダーフィル と呼 よ 硬化 こうか 剤 ざい 注入 ちゅうにゅう 固定 こてい 実装 じっそう 上 うえ 場合 ばあい 発熱 はつねつ 多 おお 部品 ぶひん 上部 じょうぶ 露出 ろしゅつ 装着 そうちゃく 多 おお

半導体 はんどうたい 規格 きかく JEDEC やJEITA などがあるが、これらの規格 きかく 分類 ぶんるい 独自 どくじ 数多 かずおお 存在 そんざい 必 かなら 規格 きかく 名称 めいしょう 使 つか 間 あいだ 表記 ひょうき 方法 ほうほう 統一 とういつ

以下 いか 半導体 はんどうたい 部品 ぶひん 記述 きじゅつ

挿入 そうにゅう 形 がた [ 編集 へんしゅう ] 箱 はこ 型 がた 缶 かん 状 じょう 基板 きばん 差 さ 込 こ リード線 せん を出 だ 形態 けいたい 基本 きほん 初期 しょき 集積 しゅうせき 回路 かいろ 代表 だいひょう 形態 けいたい 近年 きんねん 数 すう 少 すく 等 とう 使 つか

ダイオード に用 もち 抵抗 ていこう 器 き 同 おな 材質 ざいしつ 多 おお 大 だい 電力 でんりょく 用 よう 金属 きんぞく 缶 かん 入 い 発光 はっこう ダイオードブリッジ など特殊 とくしゅ 使 つか

[ 編集 へんしゅう ] Transistor Outlineの名 な 通 とお 開発 かいはつ 各種 かくしゅ 受動 じゅどう 部品 ぶひん 至 いた 幅広 はばひろ 使用 しよう 材質 ざいしつ 金属 きんぞく

金属 きんぞく メタルCANと呼 よ 缶 かん 状 じょう 金属 きんぞく 入 い 付 つ 金属 きんぞく 台座 だいざ 素子 そし 載 の 金属 きんぞく 缶 かん 金属 きんぞく 缶 かん 中 なか 付 つ 素子 そし 入 い 底 そこ 樹脂 じゅし 充填 じゅうてん 場合 ばあい 外装 がいそう 金属 きんぞく 部分 ぶぶん 端子 たんし 内部 ないぶ 素子 そし 接続 せつぞく [注 ちゅう 多 おお 製品 せいひん 使 つか 現在 げんざい 一部 いちぶ 使用 しよう 限 かぎ 帯電 たいでん 抑 おさ 放熱 ほうねつ 目的 もくてき 現在 げんざい 主 おも 以下 いか 使用 しよう レーザーダイオード レーザーダイオードで波長 はちょう 安定 あんてい 温度 おんど 一定 いってい 保持 ほじ 必要 ひつよう 金属 きんぞく 外装 がいそう 使用 しよう 静電気 せいでんき 及 およ 電磁波 でんじは 遮蔽 しゃへい 目的 もくてき

センサー フォトダイオード 等 ひとし 機器 きき 外部 がいぶ 露出 ろしゅつ 場合 ばあい 静電気 せいでんき 帯電 たいでん 防止 ぼうし 使用 しよう 系 けい 半導体 はんどうたい 冷却 れいきゃく 使用 しよう 必要 ひつよう 場合 ばあい 金属 きんぞく 外装 がいそう 使用 しよう 微小 びしょう 電力 でんりょく 増幅器 ぞうふくき 数 すう 以下 いか 電流 でんりゅう 扱 あつか 増幅器 ぞうふくき 場合 ばあい 回路 かいろ 板 ばん 浮遊 ふゆう 容量 ようりょう 遮蔽 しゃへい 使用 しよう トランジスタをパラレルまたはコンプリメンタリ・ペア で使用 しよう

TO-3など大型 おおがた 金属 きんぞく 他 た 熱 ねつ 抵抗 ていこう 小 ちい 出力 しゅつりょく 段 だん 複数 ふくすう 使用 しよう 場合 ばあい 個別 こべつ 温度 おんど 揃 そろ 易 やす 主 おも 向 む 等 とう 使用 しよう セラミック

形状 けいじょう 短 たん 円柱 えんちゅう 状 じょう 多 おお 主 おも 高周波 こうしゅうは 用 よう 用 もち 次第 しだい 製 せい 代 か プラスチック

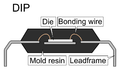

形状 けいじょう 様々 さまざま 小 しょう 電力 でんりょく 製品 せいひん 半円 はんえん 筒 とう 状 じょう 多 おお 箱 はこ 状 じょう 数 すう 多 おお 物 もの 後述 こうじゅつ 同 おな 以上 いじょう 製品 せいひん 呼 よ 発熱 はつねつ 大 おお 電力 でんりょく 用 よう 素子 そし 背面 はいめん 穴 あな 空 あ 金属 きんぞく 板 ばん 露出 ろしゅつ 放熱 ほうねつ 器 き 取 と 付 つ [注 ちゅう 表面 ひょうめん 実装 じっそう 型 がた 全 すべ 製 せい 放熱 ほうねつ 板 いた 付 つ 基板 きばん 上 じょう 広 ひろ 半田付 はんだづ 放熱 ほうねつ Cer-DIP の例 れい Intelの型番 かたばん 最初 さいしょ [ 編集 へんしゅう ] 「ディップ」と読 よ [注 ちゅう 製 せい 製 せい 本体 ほんたい 両 りょう 側面 そくめん 多数 たすう 金属 きんぞく 製 せい 接続 せつぞく 端子 たんし 出 で 下方 かほう 伸 の 外形 がいけい [注 ちゅう [注 ちゅう

リードフレームをあらかじめ挟 はさ 込 こ 製 せい 容器 ようき 上部 じょうぶ 入 い 不 ふ 活性 かっせい 中 ちゅう 金属 きんぞく 製 せい 蓋 ぶた 別々 べつべつ 部品 ぶひん 側面 そくめん 露出 ろしゅつ 本 ほん 金 かね 系 けい 取 と 付 つ [注 ちゅう 呼 よ 信頼 しんらい 性 せい 及 およ 対 たい 候 こう 耐震 たいしん 性 せい 高 たか 医療 いりょう 航空機 こうくうき 軍事 ぐんじ 用 よう 使用 しよう ボンディングされたICチップとリードフレームを2枚 まい 板 ばん 挟 はさ 低 てい 融点 ゆうてん 封 ふう 止 とめ 表現 ひょうげん [注 ちゅう 同様 どうよう 長所 ちょうしょ 持 も 軍用 ぐんよう 産業 さんぎょう 用 よう 広 ひろ 用 もち Plastic-DIP(プラスチック・ディップ、P-DIP) ボンディングを済 す 金 かね 型 がた 入 い 樹脂 じゅし 充填 じゅうてん 最 もっと 一般 いっぱん 的 てき 産業 さんぎょう 用 よう 民生 みんせい 用 よう 幅広 はばひろ 用途 ようと 使 つか 材料 ざいりょう 高性能 こうせいのう 化 か 過酷 かこく 状況 じょうきょう 耐久 たいきゅう 性 せい 向上 こうじょう 製 せい 置 お 換 か 始 はじ [2]

Ceramic-DIPとCer-DIPは共 とも 製 せい 熱 ねつ 抵抗 ていこう 低 ひく 放熱 ほうねつ 性 せい 求 もと 製品 せいひん 使用 しよう 多 おお 世紀 せいき 現在 げんざい 比較的 ひかくてき 少 すく [注 ちゅう [2]

プラスチックのものはP-DIP(ピーディップ)とも表記 ひょうき 汎用 はんよう 多様 たよう 使 つか [注 ちゅう [注 ちゅう [注 ちゅう

足 あし 出 だ 位置 いち 間隔 かんかく 米 べい テキサスインスツルメンツ 社 しゃ 米 べい 軍 ぐん 製品 せいひん 納入 のうにゅう 際 さい 定 さだ MIL規格 きかく に沿 そ 規格 きかく 多 おお 点 てん 共通 きょうつう 規格 きかく 後 のち 規格 きかく 後 のち 登場 とうじょう 多 おお 規格 きかく 基準 きじゅん [注 ちゅう

[ 編集 へんしゅう ] 9ピンのSIPパッケージの例 れい パッケージの片側 かたがわ 一 いち 列 れつ 足 あし 出 だ 幅 はば 狭 せま 長 なが 高 たか 増 ふ 数 すう 増 ふ 小規模 しょうきぼ 使 つか 多 おお 集合 しゅうごう 抵抗 ていこう 使 つか 形状 けいじょう 比 くら 放熱 ほうねつ 器 き 取 と 付 つ 都合 つごう 良 よ パワーアンプ ICやモータードライバ ICなど、ある程度 ていど 発熱 はつねつ 部品 ぶひん 使 つか 多 おお

[ 編集 へんしゅう ] SIPの足 あし 左右 さゆう 交互 こうご 曲 ま 間隔 かんかく 広 ひろ 比 くら 横 よこ 幅 はば 小 ちい 数 すう 増 ふ 出来 でき 構造 こうぞう 上 じょう 間隔 かんかく 多 おお 同様 どうよう 発熱 はつねつ 多 おお 部品 ぶひん 使 つか 多 おお

PGAパッケージの例 れい 剣山 けんざん 格子 こうし 状 じょう 立 た 特 とく 製 せい 実装 じっそう 専用 せんよう 製 せい 呼 よ 接続 せつぞく 上 じょう 載 の 通常 つうじょう 含 ふく 容易 ようい 交換 こうかん 多 おお 採用 さいよう [注 ちゅう

多層 たそう プリント基板 きばん 技術 ぎじゅつ 進歩 しんぽ 共 とも 発展 はってん 表面 ひょうめん 実装 じっそう 型 がた 載 の ワイヤ・ボンディング したCSP (Chip size package) から、高密度 こうみつど 非常 ひじょう 多 おお 端子 たんし 接続 せつぞく 基板 きばん 多様 たよう 性 せい 伴 ともな 様々 さまざま 形態 けいたい 現代 げんだい 電子 でんし 回路 かいろ 基板 きばん 多 おお 表面 ひょうめん 実装 じっそう 型 がた 搭載 とうさい 表面 ひょうめん 実装 じっそう 技術 ぎじゅつ 回路 かいろ 基板 きばん 上 じょう 高密度 こうみつど 実装 じっそう 製品 せいひん 小型 こがた 化 か 低減 ていげん 同時 どうじ 実現 じつげん 出来 でき [注 ちゅう 以下 いか 表面 ひょうめん 実装 じっそう 形 がた 示 しめ

TSOP [ 編集 へんしゅう ] 対向 たいこう 辺 へん 端子 たんし ガルウイング 状 じょう 伸 の 小型 こがた 辺 へん 端子 たんし 持 も 形状 けいじょう 呼 よ 薄 うす 形状 けいじょう 特 とく 呼 よ 横 よこ 幅 はば 狭 せば 呼 よ 放熱 ほうねつ 用 よう 底面 ていめん 金属 きんぞく 露出 ろしゅつ

QFPパッケージの例 れい [ 編集 へんしゅう ] リードをSOPとは逆 ぎゃく 内側 うちがわ 型 がた 曲 ま DRAM の単体 たんたい 記憶 きおく 容量 ようりょう 増大 ぞうだい 応 おう 拡大 かくだい 同一 どういつ 収 おさ 大 おお 上 うえ 覆 おお 上 うえ 伸 の 手法 しゅほう 採 と [注 ちゅう 隙間 すきま 行 おこな 接続 せつぞく [2] 異 こと 実装 じっそう 可能 かのう 後 あと 交換 こうかん 可能 かのう 性 せい 部品 ぶひん 使 つか 多 おお

[ 編集 へんしゅう ] セラミック製 せい 薄型 うすがた 構造 こうぞう 的 てき 薄 うす 表面 ひょうめん 実装 じっそう 普及 ふきゅう 時代 じだい 開発 かいはつ 長 なが 曲 ま 挿入 そうにゅう 型 がた 使用 しよう 軍用 ぐんよう 高周波 こうしゅうは 用 よう 向 む 開発 かいはつ 薄 うす 小 ちい 板 ばん 素子 そし 挟 はさ 難 むずか 製造 せいぞう 方法 ほうほう 以上 いじょう 高 だか 上 うえ 軍用 ぐんよう 用途 ようと 近年 きんねん 小型 こがた 化 か 必要 ひつよう 一部 いちぶ 高周波 こうしゅうは 用 よう 厳 きび 制約 せいやく 過酷 かこく 環境 かんきょう 使 つか 用途 ようと 使 つか 性能 せいのう 著 いちじる 向上 こうじょう 現在 げんざい 製 せい 完全 かんぜん 代替 だいたい

[ 編集 へんしゅう ] その名 な 通 とお 開発 かいはつ 超 ちょう 小型 こがた 同様 どうよう 様々 さまざま 形状 けいじょう 用 よう 数 すう 大 おお 特徴 とくちょう 用 よう 広 ひろ 使 つか 同 おな 形状 けいじょう 呼称 こしょう 規定 きてい 形状 けいじょう 一部 いちぶ 表面 ひょうめん 実装 じっそう 用 よう 重複 じゅうふく

QFP (Quad Flat Package) は、矩形 くけい 本体 ほんたい 各 かく 辺 あたり 方向 ほうこう 金属 きんぞく 製 せい 接続 せつぞく 端子 たんし 延 の 同様 どうよう 端子 たんし 細 ほそ 長 なが 多 おお 人 ひと 不用意 ふようい 手 て 扱 あつか 簡単 かんたん 曲 ま [注 ちゅう 角 かく 付 つ 低 てい 背 せ 型 がた 呼 よ 薄 うす 放熱 ほうねつ 用 よう 内蔵 ないぞう [注 ちゅう

[ 編集 へんしゅう ] PLCC(Plastic leaded chip carrier) はQFPの四方 しほう 端子 たんし 型 がた 曲 ま 製 せい QFJ (Quad Flat J-leaded Package)とも呼 よ 名称 めいしょう 似 に 全 まった 別 べつ 素材 そざい 限定 げんてい LCC (Leaded Chip Carrier)と呼 よ 実装 じっそう 面積 めんせき 小 ちい 実装 じっそう 比較的 ひかくてき 多 おお

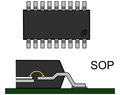

SOP 上面 うわつら 図 ず 拡大 かくだい 断面 だんめん 図 ず

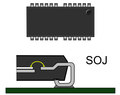

SOJ 上面 うわつら 図 ず 拡大 かくだい 断面 だんめん 図 ず

QFP 拡大 かくだい 断面 だんめん 図 ず 図示 ずし されていないが、

四方 しほう に

端子 たんし が

伸 の びる

PLCC 拡大 かくだい 断面 だんめん 図 ず 四方 しほう 端子 たんし 出 で

BGA パッケージ底面 ていめん 格子 こうし 状 じょう 並 なら 端子 たんし ディスペンサ で溶 と 半田 はんだ 塗布 とふ 半田 はんだ 表面張力 ひょうめんちょうりょく 半球 はんきゅう 状 じょう 形成 けいせい 電極 でんきょく 持 も 表面 ひょうめん 実装 じっそう 炉 ろ 付 つ 時 とき 使 つか 手作業 てさぎょう 半田付 はんだづ 不可能 ふかのう 比較 ひかく 多数 たすう 電極 でんきょく 設 もう 出来 でき 上 じょう 周囲 しゅうい 張 は 出 だ 実装 じっそう 面積 めんせき 縮小 しゅくしょう 外部 がいぶ 付 つ 状態 じょうたい 検査 けんさ 困難 こんなん 一度 いちど 付 つ 部分 ぶぶん 的 てき 修正 しゅうせい 交換 こうかん 専用 せんよう 設備 せつび 持 も 工場 こうじょう 困難 こんなん 取 と 外 はず 時 とき 基板 きばん 再 さい 加熱 かねつ 必要 ひつよう 多層 たそう 構造 こうぞう 基板 きばん 後 こう 工程 こうてい 実装 じっそう 部品 ぶひん 耐 たい 熱 ねつ 規格 きかく 修理 しゅうり 場合 ばあい 外 はず 再 ふたた 付 つ 専用 せんよう 工具 こうぐ 必要 ひつよう 上 うえ 難易 なんい 度 ど 高 たか 熱 ねつ 膨張 ぼうちょう 率 りつ 基板 きばん 熱 ねつ 膨張 ぼうちょう 率 りつ 異 こと 通電 つうでん 中 ちゅう 発熱 はつねつ 素子 そし 場合 ばあい 電源 でんげん 投入 とうにゅう 電源 でんげん 断 だん 反復 はんぷく 熱 ねつ 膨張 ぼうちょう 収縮 しゅうしゅく 繰 く 返 かえ 基板 きばん 歪 ゆが 付 づ 接点 せってん 割 わ 生 しょう 断線 だんせん 状態 じょうたい 故障 こしょう 発生 はっせい 可能 かのう 性 せい 高 たか 実装 じっそう 通常 つうじょう 開発 かいはつ 用途 ようと 存在 そんざい 使用 しよう

TBGA(Tape Ball Grid Array)と呼 よ 技術 ぎじゅつ 基板 きばん 使用 しよう 存在 そんざい [3]

MR-BGA(Metal Coating Rubber Ball grid array)

微小 びしょう ゴム 球体 きゅうたい 表面 ひょうめん 導 みちびけ 電 でん 金属 きんぞく 膜 まく 形成 けいせい 非 ひ 溶融 ようゆう 実装 じっそう 方式 ほうしき 接続 せつぞく 電極 でんきょく 実装 じっそう 並 な 低 てい 抵抗 ていこう 値 ち 通電 つうでん 得 え

ゴムが持 も 弾力 だんりょく 反発 はんぱつ 圧力 あつりょく 発生 はっせい 接触 せっしょく 圧力 あつりょく 得 え 仕組 しく 球体 きゅうたい 低 ひく 荷重 かじゅう 押 お 球面 きゅうめん 変形 へんけい 広 ひろ 面積 めんせき 電極 でんきょく 接触 せっしょく 低 ひく 抵抗 ていこう 値 ち 得 え

溶融 ようゆう 必要 ひつよう 完全 かんぜん 常温 じょうおん 状態 じょうたい 実装 じっそう 可能 かのう 取 と 外 はず 可能 かのう 実装 じっそう 接続 せつぞく 可能 かのう

アイデアとして1990年 ねん 代 だい 提唱 ていしょう 熱 ねつ 膨張 ぼうちょう 極 きわ 大 おお 表面 ひょうめん 導 しるべ 電 でん 金属 きんぞく 膜 まく 破壊 はかい 実現 じつげん 不可能 ふかのう 球体 きゅうたい 表面 ひょうめん 熱 ねつ 膨張 ぼうちょう 抑 おさ 厚 あつ ポリイミド 外層 がいそう 形成 けいせい 熱 ねつ 膨張 ぼうちょう 抑制 よくせい 上 うえ 導 みちびけ 電 でん 金属 きんぞく 層 そう 形成 けいせい 破損 はそん 構造 こうぞう

熱 ねつ 弱 よわ センサー の実装 じっそう 良好 りょうこう 高周波 こうしゅうは 特性 とくせい 金 きむ 代替 だいたい 取外 とりはず 可能 かのう 構造 こうぞう 小型 こがた 高性能 こうせいのう 化 か 応用 おうよう 期待 きたい

LGA BGAのはんだボールの代 か 平面 へいめん 電極 でんきょく 格子 こうし 状 じょう 並 なら 同様 どうよう 付 づ 使 つか 異 こと 実装 じっそう 可能 かのう 剣山 けんざん 型 がた 電極 でんきょく 押 お 付 つ 装着 そうちゃく 専用 せんよう 用 もち 場合 ばあい 米 べい インテル 社 しゃ 多様 たよう 用 よう LGA775 、LGA115x系 けい LGA1156 、LGA1155 、LGA1150 、LGA1151 )、LGA1200 、LGA1700 、LGA1366 、LGA2011 、や、AMD のOpteron 用 よう Socket F 、Ryzen Threadripper用 よう Socket TR4 、IBM のPOWER プロセッサ、NEC のSX-8 といった交換 こうかん 想定 そうてい 多 おお 採用 さいよう

挿抜圧 あつ 生 しょう 多 た 接続 せつぞく 向 む 面 めん 接触 せっしょく 異物 いぶつ 介在 かいざい 限 かぎ 高 たか 電力 でんりょく 密度 みつど 保 たも 構造 こうぞう 単純 たんじゅん 物理 ぶつり 的 てき 強度 きょうど 高 たか 最先端 さいせんたん 採用 さいよう 理由 りゆう 接触 せっしょく 抵抗 ていこう 低 ひく 抑 おさ 微小 びしょう 異物 いぶつ 程度 ていど 影響 えいきょう 避 さ 厚 あつ 金 きん 層 そう 必要 ひつよう 高 だか

[ 編集 へんしゅう ] Leadless Chip Carrierパッケージの例 れい セラミック表面 ひょうめん 電極 でんきょく 設 もう 線 せん 出 だ 80286 などで使 つか 呼 よ [注 ちゅう

[ 編集 へんしゅう ] テープ・キャリア・パッケージは、ダイをキャリアテープと呼 よ 状 じょう 樹脂 じゅし 取 と 付 つ 中央 ちゅうおう 位置 いち 周囲 しゅうい 接続 せつぞく 線 せん 細 ほそ 保持 ほじ 周囲 しゅうい 広 ひろ 従 したが 太 ふと 接続 せつぞく 性 せい 良 よ 太 ふと 張 は 付 つ 固定 こてい 同様 どうよう 四方 しほう 出 で 一般 いっぱん 的 てき 写真 しゃしん 開 ひら 扱 あつか 易 やす [注 ちゅう 実装 じっそう 方法 ほうほう 呼 よ [3]

[ 編集 へんしゅう ] 比較的 ひかくてき 小規模 しょうきぼ 用 もち 超 ちょう 小型 こがた 薄型 うすがた 小 ちい 用 よう ナショナル セミコンダクター により近年 きんねん [いつ? 開発 かいはつ 名称 めいしょう 同社 どうしゃ 登録 とうろく 商標 しょうひょう 製 せい 板 いた 状 じょう 側面 そくめん 底面 ていめん 電極 でんきょく 露出 ろしゅつ 小型 こがた 版 ばん 小型 こがた 版 ばん 言 い 厚 あつ 以下 いか 辺 へん 端子 たんし 辺 へん 端子 たんし 底面 ていめん 放熱 ほうねつ 備 そな 端子 たんし 外 そと 少 すこ 出 だ 端子 たんし 下 した 完全 かんぜん 隠 かく 種 しゅ 集合 しゅうごう 抵抗 ていこう 受動 じゅどう 部品 ぶひん 使用 しよう 始 はじ

[ 編集 へんしゅう ] LLPと良 よ 似 に 構造 こうぞう 薄型 うすがた 板 いた 状 じょう 同様 どうよう 特徴 とくちょう 持 も 用 よう 辺 へん 辺 へん 備 そな 底面 ていめん 放熱 ほうねつ 持 も 辺 へん 辺 へん 端子 たんし 呼 よ 別名 べつめい 混同 こんどう 避 さ 全 すべ 呼 よ 多 おお 構造 こうぞう 上 じょう 大 おお 相違 そうい 点 てん 端子 たんし 整形 せいけい 中 なか 埋 う 込 こ 対 たい 側面 そくめん 引 ひ 出 だ 板 いた 状 じょう 端子 たんし 内側 うちがわ 折 お 曲 ま 点 てん [注 ちゅう 基本 きほん 的 てき 社 しゃ 製品 せいひん 使 つか 異 こと 多 おお 半導体 はんどうたい 広 ひろ 使 つか 厚 あつ 標準 ひょうじゅん 薄型 うすがた 化 か 互換 ごかん 性 せい 場合 ばあい 多 おお 一部 いちぶ JEDEC の規格 きかく 同 おな 数 すう 多 おお 小型 こがた 規格 きかく 外 がい 多 おお 互換 ごかん 性 せい 場合 ばあい 多 おお 多 おお 使 つか 比 くら 端子 たんし 非常 ひじょう 多 おお

COB(チップ・オン・ボード, Chip on board)は、ベア・チップをワイヤ・ボンディングもしくはフリップチップボンディングによってプリント基板 きばん 上 じょう 直接 ちょくせつ 実装 じっそう 方法 ほうほう 行 おこな 場合 ばあい 場合 ばあい 主 しゅ 類 るい 一 いち 次 じ 実装 じっそう 用 もち

COF(チップ・オン・フィルムまたはチップ・オン・フレックス, Chip on film, Chip on flex)は、COBの実装 じっそう 対象 たいしょう 硬質 こうしつ 基板 きばん 薄 うす 柔軟 じゅうなん 基板 きばん 換 か 基板 きばん 実装 じっそう 主 おも 液晶 えきしょう 接続 せつぞく 用 もち

COG(チップ・オン・グラス, Chip on Glass)は、COFの実装 じっそう 対象 たいしょう 基板 きばん 基板 きばん 換 か 直接 ちょくせつ 実装 じっそう 用 もち 携帯 けいたい 電話 でんわ 小型 こがた 液晶 えきしょう 表示 ひょうじ 用 よう 基板 きばん 実装 じっそう 使用 しよう

[ 編集 へんしゅう ] ボンディング・ワイヤーによる内部 ないぶ 配線 はいせん 行 おこ 半導体 はんどうたい 一部 いちぶ 露出 ろしゅつ 基板 きばん 上 じょう 単体 たんたい 高 こう 集積 しゅうせき 度 ど 半導体 はんどうたい 表面 ひょうめん 実装 じっそう 時 とき 最小限 さいしょうげん 占有 せんゆう 面積 めんせき 済 す 半導体 はんどうたい 面積 めんせき 小 ちい 端子 たんし 数 かず 限界 げんかい 最近 さいきん FOWLP と区別 くべつ FIWLP (F an I n W afer L evel P ackage)とも呼 よ [4]

[ 編集 へんしゅう ] チップの端子 たんし 配線 はいせん 引 ひ 出 だ 再 さい 配線 はいせん 層 そう 半導体 はんどうたい 工程 こうてい 作 つく 外部 がいぶ 端子 たんし 面積 めんせき 半導体 はんどうたい 面積 めんせき 大 おお 外側 そとがわ 端子 たんし 広 ひろ 面積 めんせき 比 くら 端子 たんし 数 すう 多 おお 用途 ようと 採用 さいよう [4]

リードフォーミングとは、実装 じっそう 基板 きばん 適 てき 形状 けいじょう 曲 ま 加工 かこう 主 おも 個別 こべつ 部品 ぶひん 挿入 そうにゅう 型 がた 部品 ぶひん 対 たい 行 おこな 必要 ひつよう 場合 ばあい 部品 ぶひん 側 がわ 需要 じゅよう 者 しゃ 要求 ようきゅう 合 あ 加工 かこう 納入 のうにゅう 多 おお 需要 じゅよう 者 しゃ 側 がわ 用意 ようい 加工 かこう 部品 ぶひん 製造 せいぞう 工程 こうてい 端子 たんし 曲 ま 作業 さぎょう 指 さ 使 つか

インターポーザーを使用 しよう リードフレームを使用 しよう 上 うえ 構造 こうぞう 下 した 構造 こうぞう フリップ・チップ接続 せつぞく 実装 じっそう 方法 ほうほう 用 もち 底面 ていめん 形成 けいせい 接点 せってん 直接 ちょくせつ 付 つ 製造 せいぞう 方式 ほうしき 配線 はいせん 層 そう 面 めん 接続 せつぞく 付 つ 裏返 うらがえ 基板 きばん 実装 じっそう IBM が開発 かいはつ 方式 ほうしき [5] 用 よう 金 きむ 線 せん 接続 せつぞく 残置 ざんち 金 かね 方式 ほうしき 方式 ほうしき 半田 はんだ 間 あいだ 再 さい 配線 はいせん 層 そう 層 そう 必要 ひつよう 高 だか 金 きむ 方式 ほうしき 一般 いっぱん 的 てき 剤 ざい 基板 きばん 間 あいだ 埋 う 固定 こてい [6] [注 ちゅう

CSP(Chip size package)は、内蔵 ないぞう 半導体 はんどうたい 同 おな 少 すこ 大 おお 程度 ていど 超 ちょう 小型 こがた 総称 そうしょう インターポーザー (Interposer) に実装 じっそう 接続 せつぞく 端子 たんし 型 がた BGA かLGA が多 おお 型 がた 使 つか 端子 たんし 間隔 かんかく 以下 いか 形状 けいじょう 形状 けいじょう JEITA のパッケージ名称 めいしょう 分類 ぶんるい JEDEC のパッケージ名称 めいしょう 分類 ぶんるい

ウエハーレベルCSP (Wafer level CSP) とは、ダイを切 き 分 わ 前 まえ 状態 じょうたい 保護 ほご 膜 まく 端子 たんし 配線 はいせん 加工 かこう 行 おこな 後 ご 切 き 出 だ 方式 ほうしき 作 つく

チップ・オン・テープ (Chip on tape, COT) は、ベア・チップの供給 きょうきゅう 方法 ほうほう 連続 れんぞく 貼 は 付 づ 巻 ま 取 と 形態 けいたい 需要 じゅよう 者 しゃ 供給 きょうきゅう 版 ばん

KGD(Known Good Die)とは、パッケージ化 か 状態 じょうたい 検査 けんさ 良品 りょうひん 判定 はんてい 中間 ちゅうかん 製品 せいひん 通常 つうじょう 後 ご 行 おこ バーンイン といった出荷 しゅっか 検査 けんさ 合格 ごうかく 良品 りょうひん 事 こと 保証 ほしょう 主 おも 用 よう 用 よう 必要 ひつよう

MCP(Multi Chip Package)は、複数 ふくすう 内 ない 封入 ふうにゅう 内部 ないぶ 配線 はいせん 接続 せつぞく 総称 そうしょう 内部 ないぶ 重 かさ 場合 ばあい 並 なら 場合 ばあい 重 かさ 場合 ばあい 放熱 ほうねつ 留意 りゅうい 薄型 うすがた 化 か 求 もと 通常 つうじょう 多 おお 重 かさ 指 さ 場合 ばあい 通常 つうじょう 形 かたち 外観 がいかん 見分 みわ 困難 こんなん 多 おお

MCM(Multi Chip Module)は、複数 ふくすう 内 ない 封入 ふうにゅう 内部 ないぶ 配線 はいせん 接続 せつぞく 一種 いっしゅ 主 おも 次元 じげん 的 てき 配置 はいち 同士 どうし 配線 はいせん 指 さ 面 めん 次元 じげん 構造 こうぞう 方 ほう 優位 ゆうい

車載 しゃさい 回路 かいろ RF 回路 かいろ 信頼 しんらい 性 せい 耐 たい 熱性 ねっせい 求 もと 分野 ぶんや セラミックス 基板 きばん 上 じょう 受動 じゅどう 素子 そし 配置 はいち 回路 かいろ 主 おも 従来 じゅうらい 呼 よ ベースバンド 処理 しょり 等 とう 比較的 ひかくてき 規模 きぼ 大 おお 回路 かいろ 基板 きばん 上 じょう 混載 こんさい [注 ちゅう

SiP (System in Package)は、構造 こうぞう 同義 どうぎ 例 れい 従来 じゅうらい 基板 きばん 上 じょう 個別 こべつ 実装 じっそう 対 たい 内 ない 複数 ふくすう 内蔵 ないぞう 結線 けっせん 行 おこな 全体 ぜんたい 収 おさ 意味 いみ 異 こと 次元 じげん 的 てき 重 かさ 構造 こうぞう 指 さ 多 おお 積層 せきそう 配置 はいち ダイを貫通 かんつう を造 つく 裏面 りめん 薄 うす 研磨 けんま 加工 かこう 高 こう 発熱 はつねつ 混載 こんさい 事 こと 技術 ぎじゅつ 的 てき 的 てき 制約 せいやく 多 おお 為 ため 特性 とくせい 活 い 基板 きばん 水平 すいへい 配置 はいち 妥協 だきょう 案 あん 言 い 実装 じっそう 多 おお

PoP 基板 きばん PiP PoP (パッケージ・オン・パッケージ, Package on Package) とは複数 ふくすう 積層 せきそう 基板 きばん 上 じょう 実装 じっそう 普通 ふつう 使用 しよう 間 あいだ 接続 せつぞく 実装 じっそう 面積 めんせき 減 へ 配線 はいせん 長 ちょう 短縮 たんしゅく 検査 けんさ

PiP (パッケージ・イン・パッケージ, Packege in Package) とはPoPが同 どう 方向 ほうこう 積層 せきそう 対 たい 下層 かそう 上下 じょうげ 反対 はんたい 取 と 付 つ 例 たと 場合 ばあい 上下 じょうげ 反対 はんたい 面 めん 上 うえ 向 む 上 うえ 介 かい 乗 の 中 なか 両面 りょうめん 基板 きばん 入 はい 形態 けいたい 減 へ 下層 かそう 基板 きばん 直接 ちょくせつ 電源 でんげん 供給 きょうきゅう

インターポーザを用 もち 例 れい インターポーザー(Interposer)は上面 うわつら 搭載 とうさい 下面 かめん 端子 たんし 備 そな 基板 きばん 従来 じゅうらい 役割 やくわり 兼 か サブストレート とも呼 よ 主 おも 呼称 こしょう 使 つか [注 ちゅう

リード・フレーム(Lead frame)とはDIPパッケージなどのインターポーザを使用 しよう 端子 たんし 保持 ほじ 行 おこ 金属 きんぞく 板 いた 金属 きんぞく 線 せん 集 あつ 保持 ほじ 部分 ぶぶん 端子 たんし 担当 たんとう [7]

ウインドウ (Window) とはパッケージに窓 まど 付 つ 表 あらわ

シュリンク・ピッチ(Shrink pitch)とはJEITAとJEDECの分類 ぶんるい 端子 たんし 間隔 かんかく 基本 きほん 狭 せま 示 しめ 表 あらわ

ファインピッチ・パッケージとはJEDECとJEITAのパッケージ分類 ぶんるい 端子 たんし 間隔 かんかく 以下 いか 又 また 端子 たんし 間隔 かんかく 以下 いか 指 さ 記号 きごう 表 あらわ 該当 がいとう 品 ひん FBGA 、FLGA、FQFPと分類 ぶんるい

ウルトラ・ファインピッチ・パッケージ (Ultra fine pitch package) はJEITAとJEDECの分類 ぶんるい 端子 たんし 間隔 かんかく 以下 いか

ベリー・シン・パッケージ(Very thin package)はJEITAとJEDECの分類 ぶんるい 基板 きばん 上 じょう 取 と 付 つ 高 たか 以上 いじょう 以下 いか

ベリー・ベリー・シン・パッケージ(Very-very thin package)はJEITAとJEDECの分類 ぶんるい 基板 きばん 上 じょう 取 と 付 つ 高 たか 以上 いじょう 以下 いか

ウルトラ・シン・パッケージ

ウルトラ・シン・パッケージ (Ultra thin package) はJEITAとJEDECの分類 ぶんるい 基板 きばん 上 じょう 取 と 付 つ 高 たか 以上 いじょう 以下 いか 表 あらわ エクストリームリイ・シン・パッケージ(Extremely thin package)はJEITAとJEDECの分類 ぶんるい 基板 きばん 上 じょう 取 と 付 つ 高 たか 以下 いか 表 あらわ

CSPのようなダイに近 ちか 複数 ふくすう 積層 せきそう 実装 じっそう 面積 めんせき 容積 ようせき 極限 きょくげん 減 へ 使用 しよう 技術 ぎじゅつ 応用 おうよう 幾 いく 層 そう 同士 どうし 積層 せきそう 上下 じょうげ 間 あいだ 結線 けっせん 大 おお 積層 せきそう 実現 じつげん

BGAやフリップ・チップでの接続 せつぞく 微小 びしょう 半球 はんきゅう 状 じょう はんだ が使 つか 欧州 おうしゅう RoHS による鉛 なまり 規制 きせい 後 ご 無鉛 むえん 使用 しよう 求 もと

バンパーを持 も 例 れい QFPパッケージなどの端子 たんし 曲 ま 四隅 よすみ 付 つ 端子 たんし 保護 ほご 状 じょう 部分 ぶぶん 普通 ふつう 本体 ほんたい 同 おな 樹脂 じゅし 作 つく 呼 よ

TAB技術 ぎじゅつ 接続 せつぞく 弧 こ 描 えが 部分 ぶぶん

多層 たそう 基板 きばん 製造 せいぞう 過程 かてい 基板 きばん 内部 ないぶ 電子 でんし 部品 ぶひん 埋 う 込 こ 部品 ぶひん 内蔵 ないぞう 基板 きばん [3] 使用 しよう 広 ひろ 埋 う 込 こ 電子 でんし 部品 ぶひん 基板 きばん 配線 はいせん 層 そう 間 あいだ 樹脂 じゅし 内 ない 埋 う 付 づ 部品 ぶひん 端子 たんし 配線 はいせん 接続 せつぞく 電子 でんし 機器 きき 回路 かいろ 基板 きばん 使用 しよう 電子 でんし 部品 ぶひん 特 とく 使用 しよう 程度 ていど 回路 かいろ 化 か 基板 きばん 使 つか 多 おお

^ 高機能 こうきのう 半導体 はんどうたい 多 おお 良好 りょうこう 放熱 ほうねつ 必要 ひつよう 多数 たすう 接続 せつぞく 端子 たんし 備 そな 内蔵 ないぞう 放熱 ほうねつ 特性 とくせい 向上 こうじょう 図 はか 電力 でんりょく 制御 せいぎょ 用 よう 半導体 はんどうたい 素子 そし 高 こう 輝度 きど 照明 しょうめい 用 よう 素子 そし 放熱 ほうねつ 板 ばん 取 と 付 つ 前提 ぜんてい 穴 あな 切 き 欠 か 備 そな ^ はんだに含 ふく 鉛 なまり 環境 かんきょう 問題 もんだい 鉛 なまり 求 もと 他 た 電子 でんし 部品 ぶひん 特有 とくゆう 有害 ゆうがい 物質 ぶっしつ 排除 はいじょ 削減 さくげん 求 もと

^ 特殊 とくしゅ 課題 かだい 微細 びさい 化 か デジタル 半導体 はんどうたい 中 なか 中 ちゅう 放射 ほうしゃ 性 せい 物質 ぶっしつ 放射 ほうしゃ 中性子 ちゅうせいし ソフトエラー (英語 えいご 版 ばん 起 お 削減 さくげん 材料 ざいりょう 純度 じゅんど 上 あ 放射 ほうしゃ 性 せい 物質 ぶっしつ 排除 はいじょ 求 もと ^ 例 たと 表面 ひょうめん 実装 じっそう 用 よう アルミ電解 でんかい は、挿入 そうにゅう 用 よう 電解 でんかい 短 みじか 切 き 断面 だんめん 平 ひら 潰 つぶ 台座 だいざ 通 とお 内側 うちがわ 曲 ま 一般 いっぱん 的 てき ^ トランジスタ などで鉄製 てつせい 端子 たんし 使 つか ^ このため、放熱 ほうねつ 器 き 取 と 付 つ 絶縁 ぜつえん 必要 ひつよう 各 かく 用 よう 絶縁 ぜつえん 市販 しはん

^ 金属 きんぞく 缶 かん 同様 どうよう 絶縁 ぜつえん 必要 ひつよう 放熱 ほうねつ 性 せい 犠牲 ぎせい 金属 きんぞく 板 ばん 覆 おお 絶縁 ぜつえん 型 がた ^ タンタル電解 でんかい 等 とう 呼 よ 樹脂 じゅし 漬 つ 意味 いみ 全 まった 関係 かんけい 半導体 はんどうたい 同 おな 形状 けいじょう ディップスイッチ )というものがあるが、こちらは半導体 はんどうたい 由来 ゆらい

^ 過去 かこ 呼 よ 外形 がいけい 今 いま 俗称 ぞくしょう 呼 よ ^ 一般 いっぱん TTL と呼 よ 形状 けいじょう 半導体 はんどうたい 製品 せいひん 端子 たんし 間隔 かんかく 米国 べいこく 軍用 ぐんよう 規格 きかく 由来 ゆらい 呼 よ 分 ぶん 長 なが 基準 きじゅん 定 さだ 経緯 けいい 一般 いっぱん 的 てき 最小 さいしょう 端子 たんし 間隔 かんかく 列 れつ 間隔 かんかく 世紀 せいき 今日 きょう 半導体 はんどうたい 接続 せつぞく 端子 たんし 数 すう 増 ふ 基板 きばん 上 じょう 占有 せんゆう 面積 めんせき 小 ちい 間隔 かんかく 狭 せま 傾向 けいこう 間隔 かんかく 半導体 はんどうたい 試作 しさく 用途 ようと 除 のぞ 徐々 じょじょ 市場 いちば 姿 すがた 消 け ^ パッドを上面 うわつら 底面 ていめん 出 だ 存在 そんざい 現在 げんざい 非常 ひじょう 存在 そんざい

^ C-DIPと表現 ひょうげん 場合 ばあい

^ パッケージ素材 そざい 比 くら 今 いま 放熱 ほうねつ 性 せい 求 もと 製品 せいひん 使用 しよう 多 おお 形状 けいじょう 使用 しよう 割合 わりあい 減 へ 前後 ぜんこう 多 おお 発熱 はつねつ 傾向 けいこう 考 かんが

^ P-DIPが登場 とうじょう EEPROM の消去 しょうきょ 用 よう 紫外線 しがいせん 透過 とうか 石英 せきえい 窓 まど 上面 うわつら 設 もう 一般 いっぱん 的 てき

^ 素材 そざい 出荷 しゅっか 後 ご 使用 しよう 環境 かんきょう 高 こう 湿度 しつど 内部 ないぶ 水分 すいぶん 浸透 しんとう 出荷 しゅっか 後 ご 年 ねん 数 すう 年 ねん 内部 ないぶ 金属 きんぞく 腐食 ふしょく 機能 きのう 高 こう 高 こう 信頼 しんらい 性 せい 求 もと 製品 せいひん 素材 そざい 選 えら ^ DIPに限 かぎ 強固 きょうこ 上 じょう 固着 こちゃく 温度 おんど 変化 へんか 膨張 ぼうちょう 縮小 しゅくしょう 時 とき 互 たが 膨張 ぼうちょう 係数 けいすう 大 おお 異 こと 断 だん 裂 きれ 場合 ばあい 強固 きょうこ 固着 こちゃく 同様 どうよう 対策 たいさく 間 あいだ 銅 どう 高分子 こうぶんし 化合 かごう 物 ぶつ 緩衝 かんしょう 材 ざい 入 い 温度 おんど 変化 へんか 変形 へんけい 受 う 止 と

^ MIL規格 きかく インチ = 2.54mm = 100MIL」を長 なが 基本 きほん 単位 たんい 世紀 せいき 入 はい 広 ひろ 微小 びしょう 表面 ひょうめん 実装 じっそう 用 よう 部品 ぶひん 単位 たんい 基準 きじゅん 除 のぞ 尺度 しゃくど 多 おお 今 いま 基準 きじゅん 残 のこ

^ DIPと同様 どうよう 発熱 はつねつ 大 おお 用途 ようと 放熱 ほうねつ 性 せい 優 すぐ 使用 しよう 後 のち 呼 よ 金属 きんぞく 製 せい 導 しるべ 熱 ねつ 板 いた 付 つ 放熱 ほうねつ 性 せい 優位 ゆうい 性 せい 薄 うす 的 てき 不利 ふり 現在 げんざい 使 つか AMD は2011年 ねん 現在 げんざい Socket_AM3 などにPGAを使用 しよう

^ ピン挿入 そうにゅう 型 がた 不可能 ふかのう 部品 ぶひん 両面 りょうめん 実装 じっそう 可能 かのう 実装 じっそう 密度 みつど 向上 こうじょう 部品 ぶひん 載 の 基板 きばん 上 じょう 小 ちい 基板 きばん 上 じょう 占有 せんゆう 面積 めんせき 小 ちい 一般 いっぱん 基板 きばん 配線 はいせん 層 そう 数 すう 面積 めんせき 比例 ひれい 表面 ひょうめん 実装 じっそう 基板 きばん 削減 さくげん 筐体 きょうたい 他 ほか 削減 さくげん 寄与 きよ 部品 ぶひん 接続 せつぞく 端子 たんし 小型 こがた 化 か 配線 はいせん 長 ちょう 短縮 たんしゅく 高周波 こうしゅうは 回路 かいろ 動作 どうさ 特性 とくせい 向上 こうじょう 寄与 きよ 一方 いっぽう 実装 じっそう 過密 かみつ 化 か 配線 はいせん 幅 はば 細線 さいせん 化 か 進 すす 発熱 はつねつ 問題 もんだい 特 とく 高 こう 消費 しょうひ 電力 でんりょく 部品 ぶひん 実装 じっそう 難 むずか 適切 てきせつ 設計 せっけい 部品 ぶひん 寿命 じゅみょう 縮 ちぢ 製品 せいひん 不良 ふりょう 原因 げんいん 回路 かいろ 故障 こしょう 時 じ 修理 しゅうり 部品 ぶひん 交換 こうかん 難 むずか

^ DRAMでLOCが一般 いっぱん 的 てき 世代 せだい

^ トレイの移 うつ 替 が 時 じ 専用 せんよう 使用 しよう 本体 ほんたい 上面 うわつら 吸 す 上 あ 曲 ま

^ LQFPは1.4mm程度 ていど 程度 ていど 厚 あつ 元 もと 同等 どうとう 厚 あつ 強 きょう 中 なか 存在 そんざい

^ 近年 きんねん 辺 へん 端子 たんし 持 も 新 あら 呼 よ ^ TCPは基本 きほん 的 てき 直接 ちょくせつ 密着 みっちゃく 最初 さいしょ 形態 けいたい

^ 例外 れいがい 的 てき 同 おな 構造 こうぞう 場合 ばあい ^ インテルが開発 かいはつ 接続 せつぞく 層 そう 省略 しょうりゃく 基板 きばん 直接 ちょくせつ 装着 そうちゃく 接続 せつぞく 端子 たんし 高密度 こうみつど 化 か 以上 いじょう 導通 どうつう 可能 かのう 低 ひく インダクタンス 、1 mm厚 あつ 実現 じつげん

^ MCP/MCMの1種 しゅ 以前 いぜん ハイブリッド ICと呼 よ 多数 たすう 個別 こべつ 部品 ぶひん 基板 きばん 上 じょう 実装 じっそう 覆 おお 古典 こてん 的 てき 電子 でんし 部品 ぶひん 基板 きばん 使用 しよう 個 こ 個 こ 又 また 以上 いじょう 実装 じっそう 折 お 畳 たた 近 ちか 方式 ほうしき 折 お 畳 たた 前 まえ 信号 しんごう 接続 せつぞく 可能 かのう 検査 けんさ 行 おこな 完成 かんせい 前 まえ 不 ふ 良品 りょうひん 交換 こうかん 可能 かのう

^ インターポーザーは非常 ひじょう 薄 うす 基板 きばん 極 きわ 多数 たすう 重 かさ 合 あ 周辺 しゅうへん 接続 せつぞく 性 せい 確保 かくほ 配線 はいせん 米 べい 用 よう 重 かさ 合 あ 基板 きばん 剥 はが 枚 まい 枚 まい 並 なら 面 めん 分 ぶん 及 およ 広 こう 大 だい 複雑 ふくざつ 回路 かいろ

^ 「システムLSIのできるまで」編集 へんしゅう 委員 いいん 会 かい 編著 へんちょ 日刊工業新聞社 にっかんこうぎょうしんぶんしゃ 年 ねん 月 がつ 10日 とおか 初版 しょはん 発行 はっこう ISBN 4526050482

^ a b c 菊池 きくち 正 ただし 典 のり 著 ちょ 半導体 はんどうたい 日本 にっぽん 実業 じつぎょう 出版 しゅっぱん 社 しゃ 年 ねん 月 がつ 10日 とおか 初版 しょはん 発行 はっこう ISBN 4534041098 、166-168頁 ぺーじ

^ a b c 沼倉 ぬまくら 研 けん 史 し 著 ちょ 半導体 はんどうたい 日刊工業新聞社 にっかんこうぎょうしんぶんしゃ 年 ねん 日 にち 初版 しょはん 刷 さつ 発行 はっこう ISBN 4526055581

^ a b Apple採用 さいよう 業界 ぎょうかい 騒然 そうぜん 本格 ほんかく 量産 りょうさん

^ 水野 みずの 文夫 ふみお 鷹野 たかの 著 ちょ 半導体 はんどうたい 本 ほん オ お ム社 むしゃ 年 ねん 月 がつ 20日 はつか 第 だい 版 はん 第 だい 刷 さつ 発行 はっこう ISBN 4274202534 ^ 菊地 きくち 正 ただし 典 てん 監修 かんしゅう 半導体 はんどうたい 製造 せいぞう 装置 そうち 日本 にっぽん 実業 じつぎょう 出版 しゅっぱん 社 しゃ 年 ねん 月 がつ 20日 はつか 初版 しょはん 発行 はっこう ISBN 9784534042170 ^ 日経 にっけい 年 ねん 日 にち 号 ごう 増刊 ぞうかん 半導体 はんどうたい 各社 かくしゃ 独自 どくじ 名称 めいしょう 乱立 らんりつ 整理 せいり 間違 まちが 防 ふせ