组合逻辑电路

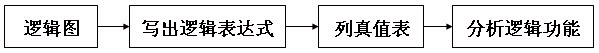

组合电路的 分析 [编辑]

组合电路

组合电路的 设计[编辑]

逻辑设计

组合逻辑

表示 [编辑]

组合逻辑

| A | B | C | 输出 | 逻辑 |

|---|---|---|---|---|

| F | F | F | F | |

| F | F | T | F | |

| F | T | F | F | |

| F | T | T | F | |

| T | F | F | T | |

| T | F | T | F | |

| T | T | F | F | |

| T | T | T | T |

运用

逻辑公式 最小 化 [编辑]

组合逻辑

| |||||||||||||||||

- ^ Lewin, Douglas. Logical Design of Switching Circuits 2nd. Thomas Nelson and Sons. 1974: 162–3. ISBN 017-771044-6.