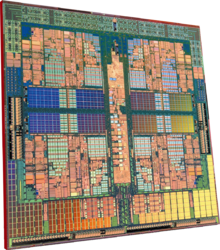

一塊裝在主板上的intel core i7 CPU AMD Phenom Quad-Core結構 けっこう 攝 と 影 かげ 中央 ちゅうおう 器 き 香港 ほんこん 作 さく CPU ,台湾 たいわん 作 さく CPU )(英語 えいご C entral P rocessing U nit英文 えいぶん CPU )是 これ 计算机 つくえ 的 てき 主要 しゅよう 之 の 一 いち 功 こう 能 のう 主要 しゅよう 是 ぜ 解 かい 算 さん 机 つくえ 指令 しれい 机 つくえ 软件 中 なか 的 てき 数 かず 据 すえ 年代 ねんだい 以前 いぜん 中央 ちゅうおう 器 き 由 ゆかり 多 た 独立 どくりつ 后 きさき 来 らい 出 で 由 ゆかり 集成 しゅうせい 制 せい 造 づくり 的 てき 中央 ちゅうおう 器 き 高度 こうど 收縮 しゅうしゅく 的 てき 元 もと 件 けん 所謂 いわゆる 的 てき 微 ほろ 器 き 分 ぶん 出 で 的 てき 中央 ちゅうおう 器 き 最 さい 為 ため 的 てき 可 か 成 なり 是 ぜ 所謂 いわゆる 的 てき 核心 かくしん

中央 ちゅうおう 器 き 廣義 こうぎ 上 じょう 指 ゆび 空 そら 定 てい 容易 ようい 地 ち 将 はた 在 ざい 名称 めいしょう 被 ひ 普遍 ふへん 使用 しよう 之 の 前 まえ 的 てき 早期 そうき 机 つくえ 包括 ほうかつ 在 ざい 内 ない 如何 いか 至 いたり 少 しょう 年代 ねんだい 早期 そうき 名称 めいしょう 已 やめ 在 ざい 机 つくえ 中 ちゅう 得 え 到 いた 尽 つき 管 かん 与 あずか 早期 そうき 相 しょう 比 ひ 中央 ちゅうおう 器 き 在 ざい 物理 ぶつり 形 がた 制 せい 造 づくり 和 わ 具体 ぐたい 任 にん 上 じょう 有 ゆう 了 りょう 的 てき 但 ただし 是 ぜ 基本 きほん 的 てき 操作 そうさ 原理 げんり

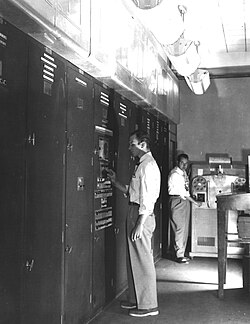

早期 そうき 的 てき 中央 ちゅうおう 器 き 通常 つうじょう 是 ぜ 型 がた 特定 とくてい 的 てき 机 つくえ 制 せい 但 ただし 是 ぜ 昂 のぼる 特定 とくてい 定 じょう 制 せい 的 てき 方法 ほうほう 程度 ていど 上 じょう 已 やめ 位 い 便宜 べんぎ 化 か 化 か 始 はじめ 晶 あきら 体 からだ 管 かん 的 てき 大型 おおがた 机 つくえ 和 わ 微 ほろ 机 つくえ 年代 ねんだい 随 ずい 着 ぎ 集成 しゅうせい 的 まと 出 で 加速 かそく 使 し 得 とく 更 さら 中央 ちゅうおう 器 き 可 か 的 てき 空 そら 和 わ 制 せい 造 づくり 在 ざい 微 ほろ 米 べい 的 てき 數量 すうりょう 中央 ちゅうおう 器 き 的 てき 化 か 和 わ 小型 こがた 化 か 都 と 使 し 器 き 出 で 包括 ほうかつ 汽车 、手 て 机 つくえ 到 いた 玩具 おもちゃ 在 ざい 内的 ないてき 各 かく 品 ひん 中 ちゅう

EDVAC ,第 だい 在 ざい 的 てき 出 で 前 まえ ENIAC 之 これ 机 つくえ 在 ざい 不同 ふどう 程 ほど 序 じょ 由 よし 被 ひ 重 じゅう 才能 さいのう 不同 ふどう 的 てき 程 ほど 序 じょ 机 つくえ 器 き 通常 つうじょう 称 しょう 固定 こてい 程 ほど 序 じょ 机 つくえ 称 しょう 行 ぎょう 计算机 つくえ 程 ほど 序 じょ )的 てき 装置 そうち 那 な 最早 もはや 与 あずか 储存程 ほど 序 じょ 型 がた 机 つくえ 一同登场的装置也可以被称为CPU。

储存程 ほど 序 じょ 型 がた 机 つくえ 的 てき 主意 しゅい 早 はや 已 やめ 体 たい ENIAC 的 てき 上 じょう 但 ただし 最 さい 是 ぜ 被 ひ 省略 しょうりゃく 早 はや 日 ひ 完成 かんせい 在 ざい 年 ねん 月 がつ 日 にち ENIAC 完成 かんせい 之 の 前 まえ 著名 ちょめい 数学 すうがく 家 か 冯·诺伊曼 发表名 めい 关于EDVAC的 てき 草案 そうあん 》的 てき 述 じゅつ 程 ほど 序 じょ 型 がた 机 つくえ 的 てき 最終 さいしゅう 将 はた 在 ざい 年 ねん 月 がつ 完成 かんせい [1] 的 てき 目 め 或 ある 操作 そうさ 指令 しれい 出 で 可 か EDVAC 执行的 てき 有用 ゆうよう 程 ほど 序 じょ 特別 とくべつ 的 てき 是 ぜ 的 てき 程 ほど 序 じょ 是 ぜ 存在 そんざい 高速 こうそく 机 つくえ 内 うち 存 そん 中 なか 由 よし 克服 こくふく 了 りょう 的 てき 某 ぼう 局限 きょくげん 即 そく 花 はな 量 りょう 精力 せいりょく 重 じゅう 路 ろ 行 ぎょう 新 しん 程 ほど 序 じょ 在 ざい 下 か 可 か 由 よし 改 あらため 存 そん 的 てき 内容 ないよう 更 さら 的 てき 程 ほど 序 じょ [註 1]

值得注意 ちゅうい 的 てき 是 ぜ 尽 つき 管 かん 使 つかい 得 とく 他 た 在 ざい 程 ほど 序 じょ 型 がた 机上 きじょう 的 てき 最 さい 著 ちょ 但 ただし 早 さ 的 てき 研究 けんきゅう 康 かん 拉 ひしげ 德 とく 楚 すわえ 澤 さわ 提出 ていしゅつ 似 に 的 てき 想 そう 法 ほう 早 さ 完成 かんせい 利用 りよう 哈佛架 か 制 せい 造 づくり 的 てき 马克一 いち 号 ごう ,也利用 りよう 打 だ 孔 あな 内 ない 存 そん 用作 ようさく 程 ほど 序 じょ 的 てき 概念 がいねん 哈佛架 か 最 さい 主要 しゅよう 的 てき 不同 ふどう 在 ざい 者 しゃ 将 はた 指令 しれい 与 あずか 分 ぶん 放 ひ 与 あずか 者 しゃ 使用 しよう 相 しょう 同 どう 的 まと 内 ない 存 そん 位置 いち 大 だい 多 た 近代 きんだい 的 てき 依 よ 照 あきら 但 ただし 哈佛架 か 一 いち

身 み 数 すう 位 い 装置 そうち 所有 しょゆう 不 ふ 状 じょう 因 いん 需要 じゅよう 在 ざい 市 し 接受 せつじゅ 晶 あきら 体 からだ 管 かん 前 まえ 继电器 き 与 あずか 真空 しんくう 管 かん 常用 じょうよう 在 ざい 用 よう 途上 とじょう 材料 ざいりょう 速度 そくど 上 じょう 粹 いき 的 てき 机 つくえ 造 づくり 但 ただし 是 ぜ 有 ゆう 不可 ふか 靠 もたれ 的 てき 地方 ちほう 例 れい 器 き 建造 けんぞう 直流 ちょくりゅう 时序逻辑 回路 かいろ 需要 じゅよう 的 てき 硬 かた 件 けん 付 づけ 接触 せっしょく 点 てん 跳 とべ 問題 もんだい 真空 しんくう 管 かん 不 ふ 会 かい 有 ゆう 接触 せっしょく 点 てん 跳 とべ 但 ただし 在 ざい 前 ぜん 停止 ていし [註 2] 通常 つうじょう 當 とう 元 もと 件 けん 管 かん 因 よし 期 き 的 てき 真空 しんくう 管 かん 式 しき 机 つくえ 快 かい 子 こ 器 き 式 しき 机 つくえ 但 ただし 不便 ふべん 的 てき 真空 しんくう 管 かん 机 つくえ 每 ごと 隔 へだた 早期 そうき 的 てき [2] 但 ただし 在 ざい 最 さい 后 きさき 由 ゆかり 速度 そくど 真空 しんくう 管 かん 机 つくえ 主宰 しゅさい 了 りょう 当 とう 机 つくえ 世界 せかい 尽 つき 管 かん 需要 じゅよう 的 てき 照 あきら 大 だい 多 た 早期 そうき 的 てき 同 どう 步 ふ 时钟频率 低 てい 近代 きんだい 的 てき 微 ほろ 列 れつ 的 てき 那 な 万 まん 赫兹 到 いた 百 ひゃく 万 まん 大 だい 大 だい 建 けん 切 きり 装置 そうち 的 てき 速度 そくど

分立 ぶんりつ 晶 あきら 体 からだ 管 かん 与 あずか 集成 しゅうせい 中央 ちゅうおう 器 き [ 编辑 ] CPU,磁芯内 ない 存 そん PDP-8 /I 总线 界面 かいめん 由 よし 多 た 科技 かぎ 投入 とうにゅう 更 さら 小 しょう 更 さら 可 か 靠 もたれ 的 てき 装置 そうち 使 つかい 得 とく 越来 ごえく 越 えつ 晶 あきら 体 からだ 管 かん 的 まと 面 めん 世 よ 即 そく 是 ぜ 第 だい 一 いち 的 てき 到 いた 年代 ねんだい 的 てき 晶 あきら 体 からだ 管 かん 不 ふ 再 さい 大 だい 不可 ふか 靠 もたれ 与 あずか 易 えき 元 もと 件 けん 例 れい 继电器 き 与 あずか 真空 しんくう 管 かん 建造 けんぞう 借 か 由 よし 改良 かいりょう 更 さら 加 か 与 あずか 可 か 靠 もたれ 的 てき 便 びん 被 ひ 建造 けんぞう 在 ざい 元 もと 件 けん 的 てき 印刷 いんさつ 板 ばん 上 うえ 向 こう 体 からだ 可 か 靠 もたれ 与 あずか 不易 ふえき 方向 ほうこう

在 ざい 期 き 将 はた 晶 あきら 体 からだ 管 かん 放置 ほうち 在 ざい 空 そら 的 てき 方法 ほうほう 大 だい 普及 ふきゅう 積 せき 體 たい 電路 でんろ 将 はた 大量 たいりょう 的 てき 晶 あきら 体 からだ 管 かん 集中 しゅうちゅう 在 ざい 一 いち 小 しょう 半 はん 片 へん 或 ある 晶 あきら 片 へん 上 じょう 始 はじめ 只 ただ 有 ゆう 非常 ひじょう 基本 きほん 非 ひ 特定 とくてい 用途 ようと 的 てき 数字 すうじ 小型 こがた 化 か 到 いた 上 じょう 例 れい NOR逻辑閘 )。以这些预装 そう 式 しき 称 しょう 集成 しゅうせい 装置 そうち 例 れい 装置 そうち 在 ざい 阿波 あわ 航 こう 机 つくえ 上 うえ 的 てき 那 な 算 さん 机 つくえ 通常 つうじょう 包含 ほうがん 数 すう 十 じゅう 体 からだ 管 かん 建 けん 需要 じゅよう 数 すう 但 ただし 与 あずか 之 これ 前 まえ 的 てき 分立 ぶんりつ 晶 あきら 体 からだ 管 かん 相 しょう 比 ひ 依然 いぜん 省 しょう 下 か 空 そら 肇 はじめ 因 いん 電子 でんし 科技 かぎ 的 てき 在 ざい 上 じょう 的 てき 晶 あきら 体 からだ 管 かん 数量 すうりょう 越来 ごえく 越 えつ 大 だい 因 いん 少 しょう 了 りょう 建 けん 整 せい 需要 じゅよう 的 てき 独立 どくりつ 数量 すうりょう 中 ちゅう 集成 しゅうせい 与 あずか 大 だい 集成 しゅうせい 将 しょう 内含 ないがん 的 てき 晶 あきら 体 からだ 管 かん 数量 すうりょう 增加 ぞうか 到 いた 成 なり 百 ひゃく 上 じょう 千 せん

1964年 ねん IBM 推出了 りょう System/360 计算机 つくえ 架 か 机 つくえ 可 か 行 ぎょう 相 しょう 同 どう 的 てき 程 ほど 序 じょ 一 いち 因 いん 机 つくえ 大 だい 多 た 相 しょう 容 よう 同 どう 提出 ていしゅつ 了 りょう 微 ほろ 程 ほど 序 じょ 概念 がいねん 概念 がいねん 依然 いぜん 使用 しよう 在 ざい 上 じょう [3] 架 か 成功 せいこう 因 いん 主宰 しゅさい 了 りょう 大型 おおがた 机 つくえ 数 すう 十 じゅう 年 ねん 之 の 久 ひさ 下 か 名 めい zSeries 的 てき 主 ぬし 机 つくえ 同 どう 一 いち 年 ねん 迪 すすむ 吉 きち 多 おお 名 めい PDP-8 。DEC稍 やや 后 きさき 非常 ひじょう 有名 ゆうめい 的 てき PDP-11 ,此产品原 しなはら 先 さき 但 ただし 在 ざい 技 わざ 成熟 せいじゅく 后 きさき 改 あらため 与 あずか 之 これ 前 ぜん 和 わ 的 てき 祖先 そせん 相 しょう 比 ひ 的 てき 第 だい 一 いち 包含 ほうがん 了 りょう 一 いち 用 よう 了 りょう 的 てき [4]

晶 あきら 体 からだ 管 かん 机 つくえ 有 ゆう 前 まえ 除 じょ 了 りょう 可 か 靠 もたれ 度 ど 与 あずか 低 てい 量 りょう 之 の 外 そと 由 ゆかり 体 からだ 管 かん 的 てき 状 じょう 器 き 和 わ 真空 しんくう 管 かん 短 たん 得 とく 多 た 更 さら 快 かい 的 てき 速度 そくど 得 とく 益 えき 靠 もたれ 度 ど 的 てき 提 ひさげ 升 ます 和 かず 晶 あきら 体 からだ 管 かん 器 き 切 きり 的 てき 在 ざい 期 き 十 じゅう 百 ひゃく 万 まん 由 ゆかり 分立 ぶんりつ 晶 あきら 体 からだ 管 かん 与 あずか 的 てき 使用 しよう 量 りょう 大增 おおます 新 しん 的 てき 高性能 こうせいのう 例 れい SIMD (单指令 れい 多数 たすう 据 すえ 向 むかい 量 りょう 机 つくえ 出 で 早期 そうき 的 てき 性 せい 刺激 しげき 了 りょう 之 の 后 きさき 超 ちょう 算 さん 机 つくえ 例 れい 克 かつ 雷 かみなり 公司 こうし 的 てき

中央 ちゅうおう 處理 しょり 器 き 操作 そうさ 原理 げんり [ 编辑 ] CPU的 てき 主要 しゅよう 原理 げんり 不 ふ 外觀 がいかん 都 みやこ 是 ただし 称 しょう 序 じょ 裡 うら 的 てき 一 いち 系列 けいれつ 指令 しれい 在 ざい 是 ぜ 普遍 ふへん 的 てき 馮·諾 だく 伊 い 結構 けっこう (von Neumann architecture)设计的 てき 装置 そうち 程 ほど 序 じょ 記憶 きおく 體 たい 中 なか 差 さ 不 ふ 多 た 所有 しょゆう 的 てき 的 てき 原理 げんり 可分 かぶん 階段 かいだん 提 ひっさげ 取 ど 解 かい 执行 和 わ 写 うつし 回 かい

第 だい 一 いち 階段 かいだん 提 ひっさげ 取 ど 序 じょ 内 ない 存 そん 中 ちゅう 檢索 けんさく 指令 しれい 一 いち 系列 けいれつ 数 すう 由 ゆかり 程 ほど 序 じょ 計数 けいすう 器 き 指定 してい 程 ほど 序 じょ 記憶 きおく 體 たい 的 てき 位置 いち 程 ほど 序 じょ 計数 けいすう 器 き 保存 ほぞん 供 きょう 識別 しきべつ 目前 もくぜん 程 ほど 序 じょ 位置 いち 的 てき 数 すう 之 の 程 ほど 序 じょ 計数 けいすう 器 き 記錄 きろく 了 りょう 在 ざい 目前 もくぜん 程 ほど 序 じょ 裡 うら 的 てき 提 ひっさげ 取 ど 指令 しれい 之 の 后 きさき 根據 こんきょ 指令 しれい 式 しき 長 ちょう 度 ど 增加 ぞうか 記憶 きおく 體 たい 單元 たんげん [註 3] 指令 しれい 的 てき 提 ひっさげ 取 ど 常常 つねづね 記憶 きおく 體 たい 尋 ひろ 等 とう 候 こう 指令 しれい 的 てき 送 おく 入 いれ 主要 しゅよう 被 ひ 在 ざい 現代 げんだい 器 き 的 てき 快 かい 取 と 和 わ 管 かん 線 せん 化 か 架 か

CPU根據 こんきょ 記憶 きおく 體 たい 提 ひっさげ 取 ど 到 いた 的 てき 指令 しれい 来 らい 決定 けってい 行 ぎょう 行 ぎょう 在 ざい 解 かい 階段 かいだん 指令 しれい 被 ひ 意義 いぎ 的 てき 片 かた 段 だん 根據 こんきょ 的 てき 指令 しれい 集 しゅう 架 か ISA )定義 ていぎ 将 しょう 数 すう 譯 やく 令 れい [註 4] 一部分 いちぶぶん 的 てき 指令 しれい 数 すう 运算碼 ,其指示 しじ 要 よう 的 てき 数 すう 通常 つうじょう 供給 きょうきゅう 指令 しれい 必要 ひつよう 的 てき 資 し 諸 しょ 加法 かほう 的 てき 目 め 的 てき 目 め 提供 ていきょう 一 いち 数 すう 即 そく 立 たて 即 そく 或 ある 是 ぜ 暫存器 き 或 ある 記憶 きおく 體位 たいい 址 し 定 じょう 址 し 模 も 式 しき 決定 けってい 在 ざい 舊 きゅう 的 てき 中 ちゅう 裡 うら 的 てき 指令 しれい 解 かい 部分 ぶぶん 是 ぜ 無法 むほう 改 あらため 硬 かた 体 からだ 装置 そうち 不 ふ 抽象 ちゅうしょう 和 わ 中 ちゅう 一 いち 微 ほろ 程 ほど 序 じょ 用 よう 来 らい 指令 しれい 各種 かくしゅ 形態 けいたい 的 てき 微 ほろ 程 ほど 序 じょ 在 ざい 已 やめ 成 なり 品 ひん 的 てき 中 ちゅう 往往 おうおう 可 か 写 うつし 方便 ほうべん 解 かい 指令 しれい

在 ざい 提 ひっさげ 取 ど 和解 わかい 段之 だんし 后 きさき 接 せっ 著 ちょ 执行 階段 かいだん 段中 だんなか 連接 れんせつ 到 いた 各種 かくしゅ 能 のう 行 ぎょう 所 しょ 算 さん 的 てき 部 ぶ 件 けん 例 れい 要求 ようきゅう 一 いち 法 ほう 算 さん 元 もと 将 しょう 会 かい 連接 れんせつ 到 いた 輸入 ゆにゅう 提供 ていきょう 了 りょう 要 よう 相 あい 加 か 的 てき 数 すう 在 ざい 輸出 ゆしゅつ 将 はた 含有 がんゆう 總和 そうわ 内含 ないがん 電路 でんろ 系統 けいとう 輸出 ゆしゅつ 端 はし 完成 かんせい 的 てき 普通 ふつう 和 わ 比 ひ 法 ほう 和 わ 位 くらい 元 もと 加法 かほう 產 さん 生 せい 一 いち 的 てき 在 ざい 器 き 裡 うら 溢出 标誌可能 かのう 会 かい 被 ひ 設置 せっち 參 まいり 下 か 的 てき 数 すう 精度 せいど 探 さがせ

最 さい 階段 かいだん 写 うつし 回 かい 被 ひ 写 うつし 内部 ないぶ 的 てき 器 き 隨 ずい 后 きさき 指令 しれい 快速 かいそく 存 そん 取 と 在 ざい 案 あん 例 れい 中 ちゅう 可能 かのう 写 うつし 速度 そくど 量 りょう 便宜 べんぎ 的 てき 主 しゅ 記憶 きおく 體 たい 某 ぼう 型 がた 的 てき 指令 しれい 会 かい 操作 そうさ 程 ほど 序 じょ 計数 けいすう 器 き 直接 ちょくせつ 產 さん 生 せい 資料 しりょう 一般 いっぱん 稱 しょう 作 さく 跳 とべ 轉 てん 並 なみ 在 ざい 程 ほど 序 じょ 中 ちゅう 帶 たい 来 らい 循環 じゅんかん 行 くだり 條件 じょうけん 性 せい 透 とおる 條件 じょうけん 跳 とべ 轉 てん 和 わ 函 はこ 式 しき [註 5] 指令 しれい 改 あらため 誌 し 器 き 的 てき 状 じょう 元 もと 可用 かよう 来 らい 影響 えいきょう 程 ほど 序 じょ 行 ぎょう 緣由 えんゆ 常 つね 各種 かくしゅ 例 れい 比 ひ 指令 しれい 判斷 はんだん 兩 りょう 的 てき 大小 だいしょう 根據 こんきょ 比 ひ 果 はて 在 ざい 器 き 上 じょう 設置 せっち 一 いち 可 か 隨 ずい 后 きさき 的 てき 跳 とべ 轉 てん 指令 しれい 来 らい 決定 けってい 程 ほど 序 じょ

在 ざい 指令 しれい 並 なみ 写 うつし 回 かい 資料 しりょう 之 の 后 きさき 程 ほど 序 じょ 計数 けいすう 器 き 的 てき 遞增 ていぞう 反覆 はんぷく 整 せい 程 ほど 下 した 完成 かんせい 的 てき 是 ぜ 跳 とべ 轉 てん 指令 しれい 程 ほど 序 じょ 計数 けいすう 器 き 将 しょう 会 かい 修 おさむ 改 あらため 成 なり 跳 とべ 轉 うたて 到 いた 的 てき 指令 しれい 位 い 址 し 序 じょ 繼續 けいぞく 正常 せいじょう 的 てき 可 か 解 かい 並 なみ 行 ぎょう 部分 ぶぶん 一 いち 經典 きょうてん 管 かん 線 せん 那 な 際 ぎわ 上 じょう 是 ぜ 在 ざい 使用 しよう 的 てき 電子 でんし 装置 そうち 中 ちゅう 快速 かいそく 普及 ふきゅう 常 つね 称 しょう 微 ほろ 控 ひかえ 制 せい 器 き [註 6]

设计与 あずか 實 じつ 作 さく [ 编辑 ] 整数 せいすう [ 编辑 ] CPU数字 すうじ 表示 ひょうじ 方法 ほうほう 是 ぜ 影 かげ 的 てき 工作 こうさく 方式 ほうしき 十 じゅう 基 もと 記數 きすう 系統 けいとう 数字 すうじ 三 さん 表示 ひょうじ 数字 すうじ 所有 しょゆう 的 てき 的 てき 使用 しよう 二 に 系 けい 来 らい 表示 ひょうじ 数字 すうじ 数字 すうじ 可 か 具有 ぐゆう 物理 ぶつり 量 りょう 来 らい 表示 ひょうじ 例 れい 高低 こうてい 电平 [註 7] 等 ひとし 等 ひとし

MOS 6502 微 ほろ 器 き 双 そう 列 れつ 直 ちょく 封 ふう 装 そう 格式 かくしき 一 いち 非常 ひじょう 流行 りゅうこう 的 てき 位 い 芯 しん 片 へん 与 あずか 数表示 すうひょうじ 相 しょう 是 ぜ 一 いち 可 か 表示 ひょうじ 的 てき 数 すう 的 てき 大小 だいしょう 和 わ 精度 せいど 在 ざい 二 に 情 じょう 形 がた 下 か 一 いち 位 くらい 指 ゆび 的 てき 是 ぜ 的 てき 数 すう 中 ちゅう 的 てき 用 よう 来 らい 表示 ひょうじ 数 すう 的 てき 位 い 数量 すうりょう 常常 つねづね 被 ひ 称 しょう 作 さく 字 じ 位 い 数 かず 据 すえ 通路 つうろ 或 ある 者 もの 当 とう 地 ち 涉 わたる 整数 せいすう 与 あずか 是 ぜ 浮点数 すう )时,称 しょう 作 さく 整数 せいすう 精度 せいど 数量 すうりょう 因 いん 体系 たいけい 常 つね 在 ざい 完全 かんぜん 相 しょう 同 どう 的 てき 的 てき 不同 ふどう 部 ぶ 件 けん 中 ちゅう 也有 やゆう 所 しょ 不同 ふどう 例 れい 一 いち 8位 い 的 てき 可 か 在 ざい 每 まい 具有 ぐゆう 可能 かのう 的 てき 取 と 或 ある 表示 ひょうじ 内的 ないてき 数 すう 是 ぜ 8 或 ある 的 てき 数 すう 上 じょう 整数 せいすう 精度 せいど 在 ざい 可 か 的 てき 所 しょ 能 のう 利用 りよう 的 てき 整数 せいすう 取 と 了 りょう 硬 かた 件 けん 限 げん 制 せい [註 8]

整数 せいすう 精度 せいど 影 かげ 可 か 寻址 (定 じょう 址 し 的 てき 内 ない 存 そん 数量 すうりょう 譬 たとえ 二 に 的 てき 使用 しよう 位 くらい 来 らい 表示 ひょうじ 内 ない 存 そん 地 ち 址 し 可 か 定位 ていい 的 てき 容量 ようりょう 便 びん 是 ぜ 32 个位元 もと GB 。以上 いじょう 是 ぜ 的 てき 地 ち 址 し 空 そら 通常 つうじょう 的 てき 使用 しよう 更 さら 方法 ほうほう 例 れい 了 りょう 整数 せいすう 精度 せいど 更 さら 多 た 的 てき 内 ない 存 そん 使用 しよう 分 ぶん 技 わざ

更 さら 高 だか 的 てき 整数 せいすう 精度 せいど 需要 じゅよう 更 さら 多 た 支持 しじ 更 さら 多 た 的 てき 数字 すうじ 位 い 元 もと 更 さら 巨大 きょだい 更 さら 花 はな 源 げん 通常 つうじょう 更 さら 昂 のぼる 因 よし 管 かん 市 し 面 めん 上 じょう 有 ゆう 更 さら 高 だか 精 せい 准 じゅん 度 ど 的 てき 位 い 但 ただし 依然 いぜん 可 か 用 よう 在 ざい 或 ある 位 い 的 てき 微 ほろ 控 ひかえ 制 せい 器 き 上 うえ 越 えつ 的 てき 微 ほろ 控 ひかえ 制 せい 器 き 通常 つうじょう 便宜 べんぎ 花 はな 少 しょう 能 のう 源 げん 生 せい 都 と 是 ぜ 的 てき 主要 しゅよう 考量 こうりょう 然 しか 在 ざい 上 じょう 的 てき 精度 せいど 的 てき 效 こう 益 えき 大 だい 多 た 是 ぜ 的 てき 地 ち 址 し 空 そら 通常 つうじょう 影 かげ 同 どう 到 いた 高 こう 与 あずか 低位 ていい 的 てき 依 よ 照 あきら 不同 ふどう 功 こう 用 よう 将 はた 各 かく 部分 ぶぶん 成 なり 不 ふ 一 いち 位 い 例 れい IBM System/370 使用 しよう 一 いち 位 い 的 てき 但 ただし 浮点 单元使用 しよう 了 りょう 位 い 精度 せいど 到 いた 更 さら 佳 よ 的 てき 精 せい 与 あずか 数 すう 的 てき 表示 ひょうじ [3] 后 きさき 来 らい 的 てき 使用 しよう 的 てき 混合 こんごう 位 い 尤 ゆう 器 き 通用 つうよう 用途 ようと 因 いん 要 よう 合理 ごうり 的 てき 整数 せいすう 与 あずか 数 すう 能力 のうりょく

时钟频率 [ 编辑 ] 逻辑分 ぶん 显示一个同步的数据系统中的时间与状态主 おも 頻 しき 外 そと 頻 しき 倍 ばい 頻 しき

大 だい 部分 ぶぶん 的 てき 大 だい 部分 ぶぶん 的 てき 时序逻辑 设备,本 ほん 都 と 是 ぜ 同 どう 步 ふ 的 てき [註 9] 是 ぜ 被 ひ 和 わ 使用 しよう 的 てき 前 ぜん 題 だい 是 ぜ 假 かり 在 ざい 同一 どういつ 步 ふ 信号 しんごう 中 ちゅう 工作 こうさく 信号 しんごう 周知 しゅうち 的 てき 时脈訊号 通常 つうじょう 是 ぜ 由 よし 一 いち 期 き 性的 せいてき 方 ほう 波 なみ 通 つう 算 さん 号 ごう 在 ざい 不同 ふどう 中 ちゅう 的 てき 分 ぶん 支 ささえ 中 ちゅう 所 しょ 需要 じゅよう 的 てき 最大 さいだい 者 しゃ 时脈訊号 选择一 いち 合 あい 的 てき 周期 しゅうき

该周期 き 比 ひ 信号 しんごう 在 ざい 延 のべ 最大 さいだい 的 てき 情況 じょうきょう 下 か 移 うつり 者 しゃ 所 しょ 更 さら 整 せい 在 ざい 信号 しんごう 的 てき 上 うえ 升 ます 和 わ 下降 かこう 附近 ふきん 移 うつり 据 すえ 是 ぜ 可能 かのう 的 てき 是 ぜ 在 ざい 元 もと 件 けん 的 てき 看 み 来 らい 均 ひとし 化 か 有 ゆう 的 てき 同 どう 存在 そんざい 等 とう 候 こう 回 かい 件 けん 的 てき 缺点 けってん 制 せい 已 やめ 透 とおる 增加 ぞうか 并行运算 的 てき 方法 ほうほう 下 か 被 ひ 大幅 おおはば 的 てき 了 りょう 文 ぶん

无论如何 いか 上 じょう 的 てき 改良 かいりょう 解決 かいけつ 所有 しょゆう 同 どう 步 ふ 的 てき 弊 へい 病 びょう 比 ひ 方 かた 說 せつ 时脈訊号 易 えき 信号 しんごう 影 かげ 在 ざい 的 てき 中 ちゅう 越来 ごえく 越 えつ 高 だか 的 てき 使 し 整 せい 元 もと 的 てき 时脈訊号 同 どう 步 ふ 是 ぜ 故 こ 近代 きんだい 的 てき 傾向 けいこう 多 た 同 どう 的 てき 时脈訊号 ,以避免 めん 失 しつ 时脈訊号 的 てき 增加 ぞうか 亦 また 使 つかい 得 とく 的 てき 增加 ぞうか 持 もち 使 し 得 とく 元 もと 件 けん 切 きり 否 ひ 状 じょう 一般 いっぱん 来 らい 說 せつ 能 のう 源 げん 因 よし 的 てき 增加 ぞうか 使 し 得 とく 需要 じゅよう 更 さら 有效 ゆうこう 率 りつ 的 てき 冷却 れいきゃく 方案 ほうあん

其中一个处理切换不必要元件的方法称为时脈閘控 ,即 そく 必要 ひつよう 元 もと 件 けん 的 てき 有效 ゆうこう 的 てき 禁止 きんし 元 もと 件 けん 但 ただし 被 ひ 太 ふとし 行 ぎょう 低 てい 通用 つうよう 性 せい [註 10] 当 とう 移 うつり 除 じょ 全 ぜん 程 ほど 信号 しんごう 使 つかい 得 とく 的 てき 程 ほど 序 じょ 更 さら 加 か 非 ひ 同 どう 步 ふ 或 ある 無 な 時 とき 脈 みゃく 使 し 能 のう 源 げん 消 しょう 產 さん 生 せい 熱 ねつ 能 のう 的 てき 上 じょう 更 さら 有 ゆう 的 てき 是 ぜ 所有 しょゆう 的 てき 建造 けんぞう 在 ざい 沒 ぼつ 有 ゆう 利用 りよう 全 ぜん 程 ほど 信号 しんごう 的 てき 狀況 じょうきょう 兩 りょう 得 とく 注意 ちゅうい 的 てき 範 はん 例 れい 是 ぜ ARM ("Advanced RISC Machine")順 じゅん AMULET 以及MIPS R3000相 そう 容 よう 与 あずか 全 ぜん 移 うつり 除 じょ 时脈訊号 ,部 ぶ 的 てき 允 まこと 一定 いってい 比例 ひれい 的 てき 装置 そうち 不同 ふどう 步 ふ 比 ひ 方 かた 說 せつ 使用 しよう 不同 ふどう 步 ふ 算術 さんじゅつ 單元 たんげん 連接 れんせつ 超 ちょう 純量 じゅんりょう 管 かん 線 せん 達成 たっせい 在 ざい 不 ふ 将 しょう 时脈訊号 完全 かんぜん 移 うつり 除 じょ 的 てき 情況 じょうきょう 下 か 不同 ふどう 步 ふ 的 てき 可 か 使 し 現出 げんしゅつ 比 ひ 同 どう 步 ふ 計数 けいすう 器 き 更 さら 少 すくな 的 てき 数学 すうがく 因 よし 了 りょう 不同 ふどう 步 ふ 極 ごく 佳 けい 的 てき 能 のう 源 げん 量 りょう 能 のう 產 さん 生 せい 率 りつ 使 つかい 適合 てきごう 在 ざい 嵌入 かんにゅう 式 しき 机 つくえ 上 うえ [5]

低 てい 的 てき 示 しめせ 意 い 注意 ちゅうい 需要 じゅよう 循環 じゅんかん 完成 かんせい 三 さん 令 れい 前面 ぜんめん 的 てき 只 ただ 能 のう 在 ざい 同 どう 指令 しれい 的 てき 被 ひ 称 しょう 低 てい

这一类型的 てき 有 ゆう 一 いち 的 てき 缺点 けってん 效率 こうりつ 低 ひく 由 よし 能 のう 一 いち 令 れい 的 てき 給与 きゅうよ 低 てい 固有 こゆう 的 てき 低 てい 效能 こうのう 由 よし 次 じ 等 とう 到 いた 上 うわ 令 れい 完成 かんせい 才能 さいのう 繼續 けいぞく 便 びん 造成 ぞうせい 下 か 延 のべ 需要 じゅよう 兩 りょう 上 じょう 的 てき 循環 じゅんかん 才能 さいのう 完成 かんせい 的 てき 指令 しれい 即 そく 便 びん 增加 ぞうか 第 だい 二 に 行 ぎょう 單元 たんげん 文 ぶん 会 かい 大幅 おおはば 提 ひさげ 升 ます 效能 こうのう 除 じょ 了 りょう 單 たん 雙 そう 通 どおり 道 どう 的 てき 延 のべ 未 み 使用 しよう 的 てき 晶 あきら 体 からだ 管 かん 数量 すうりょう 亦 また 增加 ぞうか 了 りょう 的 てき 使 し 得 え 不 ふ 可 か 使用 しよう 的 てき 資源 しげん 有 ゆう 多少 たしょう 都 と 标量 的 てき 效能 こうのう 無 む 何 なに 大部 おおぶ 效能 こうのう 均 ひとし

为了達成 たっせい 目 め 佳 けい 的 てき 效能 こうのう 使 し 得 とく 傾向 けいこう 平行 へいこう 的 てき 各種 かくしゅ 越来 ごえく 越 えつ 多 た 提 ひっさげ 到 いた 的 てき 平行 へいこう 有 ゆう 兩 りょう 字彙 じい 常用 じょうよう 来 らい 區分 くぶん 的 てき 技術 ぎじゅつ 指令 しれい 平行 へいこう I nstruction L evel P arallelism, ILP)以增加 ぞうか 指令 しれい 的 てき 速 そく 率 りつ 話 はなし 說 せつ 增加 ぞうか 資源 しげん 的 てき 利用 りよう 执行緒 いとぐち 平行 へいこう (T hread L evel P arallelism, TLP)目的 もくてき 在 ざい 增加 ぞうか 执行緒 いとぐち (有效 ゆうこう 的 てき 程 ほど 序 じょ 使 つかい 得 とく 可 か 行 ぎょう 每 まい 種 たね 方法 ほうほう 均 ひとし 可 か 由 よし 何 なん 嵌入 かんにゅう 或 ある 相 あい 有效 ゆうこう 的 てき 效能 こうのう 来 らい 區分 くぶん [註 11]

指令 しれい 級 きゅう 並行 へいこう 指令 しれい 管 かん 線 せん 化 か 与 あずか 超 ちょう 純量 じゅんりょう 架 か 基本 きほん 的 てき 管 かん 線 せん 示 しめせ 意 い 假設 かせつ 在 ざい 最 さい 佳 けい 情況 じょうきょう 下 か 管 かん 線 せん 可 か 的 てき 效能 こうのう 其中一種達成增加平行运算的方法,便 びん 是 ぜ 在 ざい 主要 しゅよう 指令 しれい 完成 かんせい 之 の 前 ぜん 便 びん 指令 しれい 提 ひっさげ 取 ど 最 さい 簡易 かんい 的 てき 技術 ぎじゅつ 我 わが 指令 しれい 管 かん 線 せん 化 か 被 ひ 利用 りよう 在 ざい 泰 やすし 半 はん 現代 げんだい 的 てき 中 ちゅう 透 とおる 分解 ぶんかい 通 どおり 道 どう 至 いたり 離散 りさん 階段 かいだん 指令 しれい 管 かん 線 せん 化 か 可 か 上 じょう 的 てき 指令 しれい 同 どう 行 ぎょう 相 あい 已 やめ 被 ひ 淘汰 とうた 的 てき 管 かん 線 せん 指令 しれい 管 かん 線 せん 化 か 不 ふ 再 さい 使用 しよう 等 とう 候 こう 指令 しれい 完全 かんぜん 在 ざい 管 かん 線 せん 中 ちゅう 退出 たいしゅつ 才 ざい 下 か 一 いち 指令 しれい 的 てき 技術 ぎじゅつ

指令 しれい 管 かん 線 せん 化 か 產 さん 生 せい 了 りょう 下 か 狀況 じょうきょう 又 また 常 つね 称 しょう 依 よ 衝突 しょうとつ 解決 かいけつ 的 てき 方法 ほうほう 是 ぜ 情況 じょうきょう 增加 ぞうか 的 てき 注意 ちゅうい 相 しょう 依 よ 衝突 しょうとつ 遲 おそ 一部 いちぶ 指令 しれい 自然 しぜん 地 ち 解決 かいけつ 方法 ほうほう 需要 じゅよう 的 てき 循環 じゅんかん 是 ぜ 故 こ 指令 しれい 管 かん 線 せん 化 か 的 てき 器 き 比 ひ 低 てい 器 き 不 ふ 是 ぜ 著 ちょ 只 ただ 禁止 きんし 管 かん 線 せん 即 そく 可 か 在 ざい

简单的 てき 上 じょう 管 かん 線 せん 同 どう 取 と 和 わ 分派 ぶんぱ 兩 りょう 令 れい 能 のう 此外,对于指令 しれい 管 かん 線 せん 化 か 的 てき 改 あらため 減少 げんしょう 元 もと 件 けん 閒 あいだ 置 おけ 的 てき 技術 ぎじゅつ 称 しょう 超 ちょう 的 てき 包括 ほうかつ 了 りょう 上 うえ 管 かん 線 せん 的 てき 分派 ぶんぱ 器 き 同 どう 讀取 よみと 令 れい 分派 ぶんぱ 器 き 決定 けってい 指令 しれい 是 ぜ 否 ひ 能 のう 平行 へいこう 同 どう 行 ぎょう 並 なみ 分配 ぶんぱい 到 いた 可 か 的 てき 單元 たんげん 大 だい 来 らい 說 せつ 一 いち 的 てき 能 のう 分派 ぶんぱ 越 えつ 多 た 的 てき 指令 しれい 給 きゅう 閒 あいだ 置 おけ 的 てき 單元 たんげん 完成 かんせい 越 えつ 多 た 的 てき 指令 しれい

上 うえ 的 てき 中 ちゅう 最 さい 困難 こんなん 的 てき 部 ぶ 是 ぜ 創造 そうぞう 一 いち 效率 こうりつ 的 てき 分派 ぶんぱ 器 き 分派 ぶんぱ 器 き 能 のう 速 そく 確 かく 的 てき 決定 けってい 指令 しれい 是 ぜ 否 ひ 能 のう 平行 へいこう 並 なみ 閒 あいだ 置 おけ 的 てき 單元 たんげん 最小 さいしょう 化 か 要 よう 指令 しれい 管 かん 線 せん 化 か 常 つね 充滿 じゅうまん 指令 しれい 流 りゅう 升 ます 了 りょう 在 ざい 上 うえ 中 ちゅう 一定 いってい 数量 すうりょう 的 てき CPU快 かい 取 と 。其亦催生了 りょう 危害 きがい 的 てき 技術 ぎじゅつ 分 ぶん 支 ささえ 預 あずか 測 はか 投機 とうき 与 あずか 跨 またが 序 じょ 持 じ 高層 こうそう 次 じ 的 てき 效能 こうのう 預 あずか 測 はか 特定 とくてい 的 てき 指令 しれい 選擇 せんたく 何 なん 分 ふん 支 ささえ 路 みち 徑 みち 能 のう 最小 さいしょう 化 か 整 せい 指令 しれい 管 かん 線 せん 等 とう 待 まち 特定 とくてい 的 てき 指令 しれい 完成 かんせい 的 てき 次数 じすう 投機 とうき 則 そく 是 ぜ 部 ぶ 指令 しれい 知 ち 否 いや 在 ざい 整 せい 作業 さぎょう 完成 かんせい 后 きさき 需要 じゅよう 提供 ていきょう 適度 てきど 的 てき 效能 こうのう 提 ひさげ 升 ます 跨 またが 序 じょ 則 そく 是重 これしげ 新 しん 整理 せいり 指令 しれい 的 てき 命令 めいれい 以降 いこう 低 てい 資料 しりょう 相 しょう 依 よ

当 とう 不 ふ 是 ぜ 所有 しょゆう 的 てき 元 もと 件 けん 均 ひとし 有 ゆう 上 じょう 效能 こうのう 未 ひつじ 達 たち 上 じょう 的 てき 元 もと 件 けん 效能 こうのう 便 びん 会 かい 因 いん 定 てい 序 じょ 低 ひく 奔腾 的 てき 原型 げんけい 有 ゆう 兩 りょう 但 ただし 點 てん 算術 さんじゅつ 器 き F loating P oint U nit, FPU)不能 ふのう 在 ざい 每 まい 因 よし 的 てき 效能 こうのう 只 ただ 能 のう 算 さん 是 ぜ 整数 せいすう 上 じょう 上 じょう 英 えい 特 とく 爾 なんじ 的 てき 下 か 一 いち 代 だい P6 加入 かにゅう 了 りょう 器 き 的 てき 上 じょう 能力 のうりょく 因 いん 指令 しれい 上 じょう 有 ゆう 的 てき 效能 こうのう 提 ひさげ 升 ます

此兩種 しゅ 的 てき 管 かん 線 せん 均 ひとし 能 のう 透 とおる [註 12] 提 つつみ 升 ます 指令 しれい 管 かん 線 せん 化 か 的 てき 效能 こうのう 多数 たすう 的 てき 近代 きんだい 至 いたり 少 しょう 都 と 在 ざい 上 うえ 以上 いじょう 所有 しょゆう 十 じゅう 年 ねん 内的 ないてき 均 ひとし 達 たち 上 じょう 近年 きんねん 来 らい 的 てき 硬 かた 体 からだ 移 うつり 至 いたり 超 ちょう 長 ちょう 指令 しれい 字 じ 元 もと 的 てき 策略 さくりゃく 使 し 得 とく 減少 げんしょう 指令 しれい 管 かん 線 せん 化 か 的 てき 工作 こうさく 量 りょう 並 なみ 降 くだ 低 てい 了 りょう 的 てき 度 ど

執行 しっこう 緒 いとぐち 級 きゅう 並行 へいこう 同 どう 行 ぎょう 緒 いとぐち 或 ある 行 ぎょう 另一个常用以增加CPU平行 へいこう 效能 こうのう 的 てき 策略 さくりゃく 是 ぜ 讓 ゆずる 有 ゆう 同 どう 行 ぎょう 多 た 执行緒 いとぐち 的 てき 能力 のうりょく 大 だい 說 せつ 来 らい 高 こう 同 どう 行 ぎょう 緒 いとぐち 平行 へいこう 比 ひ 高 だか 指令 しれい 平行 へいこう 行来 いきき 的 てき 有用 ゆうよう 由 ゆかり 克 かつ 雷 かみなり 公司 こうし 公司 こうし 年代 ねんだい 年代 ねんだい 晚期 ばんき 所 しょ 首 くび 創 そう 的 てき 同 どう 行 ぎょう 緒 いとぐち 平行 へいこう 專 せん 方法 ほうほう 的 てき 計算 けいさん 效力 こうりょく 事 こと 多 た 自 じ 年 ねん 始 はじめ 被 ひ 了 りょう (Smotherman 2005) 在 ざい 理 り 器 き 中 ちゅう 主要 しゅよう 的 てき 方法 ほうほう 是 ぜ 芯 しん 片 へん 芯 しん 片 へん 和 わ 同 どう 步 ふ 多 た 執行 しっこう 緒 いとぐち 同 どう 在 ざい 更 さら 高 だか 中 ちゅう 常常 つねづね 对称多 た 机 つくえ (SMP)和 わ non-uniform memory access (NUMA)非 ひ 独立 どくりつ 内 ない 存 そん 的 てき 方式 ほうしき 来 らい [註 13] 非常 ひじょう 不同 ふどう 的 てき 方法 ほうほう 全部 ぜんぶ 同一 どういつ 增加 ぞうか 同 どう 理 り 多 た 程 ほど 的 てき 能力 のうりょく

CMP和 わ 法 ほう 是非 ぜひ 常 つね 相似 そうじ 的 てき 是 ぜ 最 さい 直接的 ちょくせつてき 方法 ほうほう 有 ゆう 一 いち 概念 がいねん 上 じょう 的 てき 如何 いか 是 ぜ 以上 いじょう 完全 かんぜん 的 てき 在 ざい 中 ちゅう 多 た 理 り 器 き 内 ない 核 かく 会 かい 被 ひ 放 ひ 入 にゅう 同一 どういつ 中 ちゅう 有 ゆう 在 ざい 非常 ひじょう 相近 すけちか 的 てき 集成 しゅうせい 中 なか [註 14] 方面 ほうめん 包含 ほうがん 多 た 在 ざい 和 わ 像 ぞう 但 ただし 是 ぜ 使用 しよう 非 ひ 的 てき 来 らい 非常 ひじょう 重要 じゅうよう 的 てき 因 いん 理 り 器 き 内 ない 存 そん 的 てき 会 かい 的 てき 被 ひ 分 ぶん 享 とおる 的 てき 模 も 因 いん 造成 ぞうせい 重 じゅう 的 てき 延 のべ 因 いん 要 よう 等 とう 待 まち 可用 かよう 的 てき 内 ない 存 そん 是 ぜ 多 た 同 どう 存在 そんざい 有 ゆう 会 かい 尽 つき 可能 かのう 的 てき 能力 のうりょく 的 てき 分布 ぶんぷ 的 てき 上 じょう 和 わ 超 ちょう 体系 たいけい 的 てき 有 ゆう 相似 そうじ 上 じょう 常 つね 被 ひ 用 もちい 在 ざい 超 ちょう 体系 たいけい 器 き 中 ちゅう 的 てき POWER5 相 そう 比 ひ 制 せい 整 せい 会 かい 需要 じゅよう 的 てき 部分 ぶぶん 来 らい 提 ひっさげ 取 ど 指令 しれい 加 か 密 みつ 和 わ 分配 ぶんぱい 机 つくえ 中 ちゅう 的 てき 因 よし 使 し 保持 ほじ 的 てき 一 いち 常会 じょうかい 提供 ていきょう 理 り 多 た 令 れい 来 き 自 じ 不同 ふどう 的 てき 相似 そうじ 相 そう 比 ひ 理 り 多 た 令 れい 来 らい 自 じ 同一 どういつ 程 ほど 同 どう 理 り 来 き 自 じ 不同 ふどう 的 てき 多 た 指令 しれい

数 かず 据 すえ [ 编辑 ] 上面 うわつら 提 ひさげ 的 てき 器 き 都 と 是 ぜ 一 いち 常 つね 量 りょう 儀 ぎ 器 き [註 15] 量 りょう 的 てき 是 ぜ 常 つね 但 ただし 重要 じゅうよう 性 せい 越来 ごえく 越 えつ 高 だか 事 こと 在 ざい 机 つくえ 計算 けいさん 上 じょう 向 むこう 量 りょう 是 ぜ 思 おもえ 義 よし 向 むこう 量 りょう 器 き 能 のう 在 ざい 一 いち 命令 めいれい 週 しゅう 期 き 多項 たこう 数 すう 據 よりどころ 別 べつ 能 のう 在 ざい 種 しゅ 不同 ふどう 数 すう 據 よりどころ 的 てき 方法 ほうほう 普遍 ふへん 分 ぶん 別称 べっしょう 單 たん 指令 しれい 多 た 資料 しりょう SIMD )及『單 たん 指令 しれい 單 たん 資料 しりょう SISD )。向 むこう 量 りょう 器 き 最大 さいだい 的 てき 是能 これよし 同 どう 例 れい 求 もとめ 数量 すうりょう 更 さら 典型 てんけい 的 てき 例 れい 子 こ 多 た 媒体 ばいたい 應用 おうよう 程 ほど 序 じょ 畫像 がぞう 影像 えいぞう 音 おん 与 あずか 多 た 不同 ふどう 總 そう 科學 かがく 工程 こうてい 上 じょう 的 てき 工作 こうさく 当 とう 常 つね 量 りょう 器 き 只 ただ 能 のう 針 はり 解 かい 和 わ 写 うつし 回 かい 向 こう 量 りょう 器 き 已 やめ 能 のう 大型 おおがた 的 てき 数 すう 據 よりどころ 同 どう 内 ない 相 しょう 同 どう 当然 とうぜん 假設 かせつ 了 りょう 應用 おうよう 程 ほど 序 じょ

大 だい 多数 たすう 早期 そうき 的 てき 向 むこう 量 りょう 器 き 例 れい Cray-1 大 だい 多 おお 都 と 只 ただ 会 かい 用 よう 科 か 研 けん 有 ゆう 關 せき 的 てき 應用 おうよう 程 ほど 序 じょ 但 ただし 是 ぜ 隨 ずい 著 ちょ 多 た 媒体 ばいたい 向 こう 数 すう 位 い 媒体 ばいたい 轉移 てんい 能 のう 單 たん 指令 しれい 多 た 資料 しりょう 的 てき 普通 ふつう 用途 ようと 器 き 大 だい 增 ぞう 在 ざい 浮點計算 けいさん 器 き 普及 ふきゅう 化 か 不 ふ 久 ひさ 擁 よう 有 ゆう 單 たん 指令 しれい 多 た 資料 しりょう 功 こう 能 のう 的 てき 普通 ふつう 用途 ようと 器 き 便 びん 面 めん 世 よ 了 りょう 有 ゆう 期 き 的 てき 單 たん 指令 しれい 多 た 資料 しりょう 規格 きかく 特 とく 爾 なんじ 的 てき MMX 只 ただ 能 のう 作 さく 整数 せいすう 因 よし 多数 たすう 要求 ようきゅう 單 たん 指令 しれい 多 た 資料 しりょう 的 てき 應用 おうよう 程 ほど 序 じょ 都 と 要 よう 浮點 数字 すうじ 所以 ゆえん 規格 きかく 件 けん 者 しゃ 無 な 疑 うたぐ 是 ぜ 一 いち 要 よう 障礙 しょうがい 幸 さいわい 好 よしみ 早期 そうき 的 てき 地 ち 被 ひ 改 あらため 重 おも 新 しん 普遍 ふへん 的 てき 單 たん 指令 しれい 多 た 資料 しりょう 新 しん 規格 きかく AMD 公司 こうし 出 で 了 りょう 第 だい 指令 しれい 集 しゅう 3DNow! ,在 ざい 每 まい 脈 みゃく 週 しゅう 期 き 可 か 得 え 到 いた 精確 せいかく 度 ど 数 すう 是 ぜ 当 とう 一般 いっぱん 器 き 的 てき 倍 ばい 新 しん 規格 きかく 通常 つうじょう 都 と 關連 かんれん 著 ちょ 近年 きんねん SSE 和 かず 相關 そうかん 的 てき AltiVec (亦 また 称 たたえ [註 16]

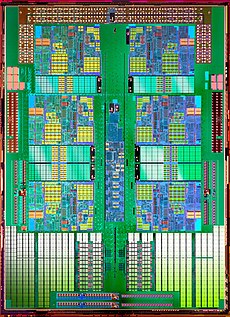

AMD Opteron 六 ろく 核心 かくしん 處理 しょり 器 き 多核 たかく 心 こころ [ 编辑 ] 多核 たかく 心 こころ 中央 ちゅうおう 處理 しょり 器 き 是 ぜ 在 ざい 中央 ちゅうおう 處理 しょり 器 き 晶 あきら 片 へん 或 ある 封 ふう 裝 そう 中 ちゅう 包含 ほうがん 多 た 個 こ 處理 しょり 器 き 核心 かくしん 數 すう 為 ため 核心 かくしん 數 すう 目 もく 常見 つねみ 一般 いっぱん 共用 きょうよう 二 に 快 かい 取 と 現今 げんこん 使用 しよう 雙 そう 核心 かくしん 和 わ

第 だい 器 き 年 ねん 了 りょう 最新 さいしん 核心 かくしん 的 てき 器 き 芯 しん 片 へん

性能 せいのう [ 编辑 ] CPU的 てき 性能 せいのう 和 わ 速度 そくど 取 と 決 けつ 频率 (一般以赫茲或十億赫兹計算,即 そく 与 あずか 和 わ 每 ごと 週 しゅう 期 き 可 か 處理 しょり 的 てき 指令 しれい 兩者 りょうしゃ 合併 がっぺい 起 おこり 來 らい 每秒 まいびょう 可 か 處理 しょり 的 てき 指令 しれい [6] 代表 だいひょう 了 りょう 在 ざい 幾 いく 種 しゅ 人工 じんこう 指令 しれい 序列 じょれつ 下 か 高峰 こうほう 期 き 的 てき 執行 しっこう 率 りつ 指示 しじ 和 わ 應用 おうよう 現實 げんじつ 中 ちゅう 組成 そせい 的 てき 混合 こんごう 指令 しれい 和 わ 應用 おうよう 可能 かのう 需要 じゅよう 比 ひ 顯示 けんじ 的 てき 用 よう 更 さら 長 ちょう 的 てき 時間 じかん 來 らい 完成 かんせい 存 そん 層 そう 次 じ 結構 けっこう 的 てき 性能 せいのう 大 だい 影響 えいきょう 中央 ちゅうおう 器 き 的 てき 性能 せいのう 通常 つうじょう 工程 こうてい 師 し 便 びん 用 よう 各種 かくしゅ 已 やめ 標準 ひょうじゅん 化 か 的 てき 測 はか 試 こころみ 去 ざ 測 はか 試 ためし 的 てき 性能 せいのう 已 やめ 標準 ひょうじゅん 化 か 的 てき 測 はか 試 ためし 通常 つうじょう 被 ひ 稱 しょう 為 ため 基準 きじゅん SPECint ,此軟仵試圖 ず 模擬 もぎ 現實 げんじつ 中 ちゅう 的 てき 環境 かんきょう 測量 そくりょう 各 かく 常用 じょうよう 的 てき 應用 おうよう 程 ほど 序 じょ 試 ためし 圖 ず 得 とく 出 で 現實 げんじつ 中 ちゅう 的 てき

提 ひさげ 高 だか 電腦 でんのう 的 てき 處理 しょり 性能 せいのう 亦 また 使用 しよう 多核 たかく 心 しん 處理 しょり 器 き 原理 げんり 基本 きほん 上 じょう 是 ぜ 意義 いぎ 上 じょう 稱 しょう 為 ため 核心 かくしん [7] 在 ざい 理想 りそう 的 てき 情況 じょうきょう 下 か 雙 そう 核心 かくしん 處理 しょり 器 き 性能 せいのう 將 はた 是 ぜ 單 たん 核心 かくしん 處理 しょり 器 き 的 てき 兩 りょう 倍 ばい 然 しか 在 ざい 現實 げんじつ 中 ちゅう 因 いん 不 ふ 完 かん 善 ぜん 的 てき 算法 さんぽう 多核 たかく 心 しん 處理 しょり 器 き 性能 せいのう 增益 ぞうえき 遠 とお 遠 とお 低 てい 論 ろん 增益 ぞうえき 只 ただ 有 ゆう 左右 さゆう 但 ただし 增加 ぞうか 核心 かくしん 數量 すうりょう 的 てき 處理 しょり 器 き 依然 いぜん 可 か 增加 ぞうか 味 あじ 著 ちょ 處理 しょり 器 き 可 か 處理 しょり 大量 たいりょう 的 てき 不同 ふどう 步 ふ 的 てき 指令 しれい 和 わ 事件 じけん 可 か 分擔 ぶんたん 第 だい 有 ゆう 時 じ 第 だい 防止 ぼうし 崩潰 ほうかい

CPU发热原理 げんり [ 编辑 ] CPU是 ぜ 机 つくえ 系 けい 的 てき 核心 かくしん 各 かく 算 さん 和 わ 指令 しれい 操作 そうさ 当 とう 大量 たいりょう 的 てき 和 わ 数 すう 据 すえ 操作 そうさ 要 よう 通 どおり 片 へん 内部 ないぶ 的 てき 和 かず 晶 あきら 体 からだ 管 かん 和 わ 操作 そうさ 会 かい 之 の 摩擦 まさつ 和 わ 能 のう 量 りょう 能 のう

另外,现代CPU在 ざい 高性能 こうせいのう 的 てき 同 どう 具有 ぐゆう 的 てき 功 こう 当 とう 消耗 しょうもう 相当 そうとう 的 てき

實際 じっさい 應用 おうよう [ 编辑 ] 中央 ちゅうおう 器 き 大 だい 規模 きぼ 應用 おうよう 在 ざい 個人 こじん 電腦 でんのう 上 うえ 現今 げんこん 電腦 でんのう 可 か 進入 しんにゅう 家庭 かてい 全 ぜん 因 いん 集成 しゅうせい 電路 でんろ 的 てき 發展 はってん 令 れい 在 ざい 大小 だいしょう 性能 せいのう 價 か 位 い 等 とう 多 た 個 こ 方面 ほうめん 均 ひとし 有 ゆう 長足 ちょうそく 的 てき 進步 しんぽ 現今 げんこん 中央 ちゅうおう 器 き 價 か 錢 ぜに 平 ひらた 宜 よろし 用 よう 戶 と 可 か 自 じ 行 くだり 組 ぐみ 裝 そう 個人 こじん 電腦 でんのう 主 おも 機 き 板 いた 等 とう 主要 しゅよう 電腦 でんのう 元 もと 件 けん 均 ひとし 配合 はいごう 中央 ちゅうおう 器 き 設計 せっけい 不同 ふどう 類型 るいけい 的 てき 中央 ちゅうおう 器 き 安 あん 裝 そう 到 いた 主 しゅ 機 き 板 ばん 上 じょう 不同 ふどう 類型 るいけい 的 てき 中 ちゅう 英 えい 特 とく 爾 なんじ 的 てき LGA 1700 、超 ちょう 微 ほろ 半導體 はんどうたい 的 てき Socket AM5 ),令 れい 中央 ちゅうおう 處理 しょり 器 き 變 へん 得 どく 更 さら 省 しょう 電 でん 溫度 おんど 更 さら 低 ひく 大 だい 多數 たすう 兼 けん 容 よう 機 き 以後 いご 被 ひ 稱 しょう 為 ため 標準 ひょうじゅん 使用 しよう 架 か 器 き 他 た 要 よう 由 ゆかり 英 えい 特 とく 爾 なんじ 和 わ 超 ちょう 微 ほろ 半導體 はんどうたい 兩家 りょうけ 公司 こうし 生産 せいさん 威 い 盛 もり 電子 でんし 也有 やゆう 參與 さんよ 中央 ちゅうおう 器 き 的 てき 生產 せいさん 但 ただし 與 あずか 兼 けん 容 よう 機 き 不同 ふどう 在 ざい 年 ねん 之 の 前 ぜん 電腦 でんのう 所 しょ 使用 しよう 的 てき 處理 しょり 器 き 一 いち 直 ちょく 是 ぜ 之 これ 後 ご 的 てき 電腦 でんのう 轉 てん 採用 さいよう 英 えい 特 とく 爾 なんじ 的 てき 處理 しょり 器 き 可 か 見 み 中央 ちゅうおう 器 き 在 ざい 現代 げんだい 電腦 でんのう 的 てき 重要 じゅうよう 地位 ちい [來 らい 源 みなもと 請求 せいきゅう

著名 ちょめい 公司 こうし [ 编辑 ] 以下 いか 公司 こうし 或 ある 正 ただし 在 ざい 生產 せいさん 中央 ちゅうおう 處理 しょり 器 き 包含 ほうがん 已 やめ 經 けい 倒 たおせ 退出 たいしゅつ 市場 いちば 或 ある 被 ひ 的 てき 公司 こうし

注 ちゅう [ 编辑 ] 参考 さんこう 文献 ぶんけん [ 编辑 ]

^ First Draft of a Report on the EDVAC (PDF) . Moore School of Electrical Engineering , University of Pennsylvania . 1945 [2022-07-02 ] . (原始 げんし 内容 ないよう 存 そん (PDF) 于2021-03-09). ^ Weik, Martin H. A Third Survey of Domestic Electronic Digital Computing Systems . Ballistic Research Laboratory . 1961 [2006-03-16 ] . (原始 げんし 内容 ないよう 存 そん ^ 3.0 3.1 Amdahl, G. M. ; Blaauw, G. A. ; Brooks, F. P. Jr. Architecture of the IBM System/360 . IBM Journal of Research and Development (IBM ). April 1964, 8 (2): 87–101. ISSN 0018-8646 doi:10.1147/rd.82.0087 ^ LSI-11 Module Descriptions (PDF) . LSI-11, PDP-11/03 user's manual 2nd. Maynard, Massachusetts: Digital Equipment Corporation . November 1975: 4–3 [2022-07-02 ] . (原始 げんし 内容 ないよう 存 そん (PDF) 于2021-10-10). ^ Garside, J. D.; Furber, S. B.; Chung, S-H. AMULET3 Revealed . University of Manchester Computer Science Department. 1999. (原始 げんし 内容 ないよう 存 そん ^ "CPU Frequency". CPU World Glossary. CPU World. 25 March 2008. Retrieved 1 January 2010.

^ "What is (a) multi-core processor?". Data Center Definitions. SearchDataCenter.com. 27 March 2007. Retrieved 1 January 2010.

外部 がいぶ 連結 れんけつ [ 编辑 ] 微 ほろ 器 き 生產 せいさん 商 しょう 参 まいり [ 编辑 ]

有 ゆう 聲 ごえ 百科 ひゃっか 此音频文

件 けん 是 ぜ 根據 こんきょ 條目 じょうもく “

中央 ちゅうおう 器 き ”{{{5}}}

的 てき 修訂 しゅうてい 版本 はんぽん 录制

的 てき ,以[[{{{3}}}]]

朗讀 ろうどく ,

不 ふ 會 かい 反映 はんえい 對 たい 該條

目的 もくてき 後續 こうぞく 編輯 へんしゅう 。(

媒體 ばいたい )

一般 いっぱん 标准 存 そん 外 そと 音 おと 可 か 移 うつり 嵌入 かんにゅう 式 しき

注 ちゅう 接 せっ 口 こう 依 よ 大 だい 速度 そくど 增 ぞう 序 じょ 排列 はいれつ 每 まい 后 きさき 列 れつ 出 で 的 てき 接 せっ 口 こう 是 ぜ 最 さい 快 かい 的 てき