集積 しゅうせき 回路 かいろ 例 れい 写真 しゃしん 中央 ちゅうおう 黒色 こくしょく 正方形 せいほうけい 集積 しゅうせき 回路 かいろ 外観 がいかん 集積 しゅうせき 回路 かいろ ダイ (回路 かいろ 形成 けいせい 半導体 はんどうたい 四角 しかく 切 き 出 だ 通常 つうじょう 封入 ふうにゅう 見 み 555 タイマー ICのもの。集積 しゅうせき 回路 かいろ 英 えい integrated circuit, IC )は、半導体 はんどうたい 表面 ひょうめん 微細 びさい 複雑 ふくざつ 電子 でんし 回路 かいろ 形成 けいせい 上 うえ 封入 ふうにゅう 電子 でんし 部品 ぶひん

集積 しゅうせき 回路 かいろ シリコン 単 たん 結晶 けっしょう 代表 だいひょう 半導体 はんどうたい [ 注釈 ちゅうしゃく ] 表面 ひょうめん 不純物 ふじゅんぶつ 拡散 かくさん トランジスタ ・コンデンサ ・抵抗 ていこう 器 き 動作 どうさ 構造 こうぞう 形成 けいせい 蒸着 じょうちゃく エッチング によって配線 はいせん 形成 けいせい 電子 でんし 回路 かいろ 作 つく 込 こ 電子 でんし 部品 ぶひん [ 注釈 ちゅうしゃく ]

多 おお 場合 ばあい 複数 ふくすう 端子 たんし 持 も 比較的 ひかくてき 小型 こがた [ 注釈 ちゅうしゃく ] パッケージ に封入 ふうにゅう 内部 ないぶ 端子 たんし 配線 はいせん 状態 じょうたい 出荷 しゅっか 半導体 はんどうたい 部品 ぶひん 電子 でんし 部品 ぶひん 流通 りゅうつう

1940年代 ねんだい 末 まつ トランジスタ の発明 はつめい 次 つ 年代 ねんだい 考案 こうあん 製造 せいぞう 技術 ぎじゅつ 微細 びさい 化 か 技術 ぎじゅつ 進歩 しんぽ 内蔵 ないぞう 部品 ぶひん 数 すう ムーアの法則 ほうそく で増 ふ 続 つづ 性能 せいのう 向上 こうじょう 続 つづ #歴史 れきし )

製造 せいぞう 工程 こうてい フォトリソグラフィ という光学 こうがく 技術 ぎじゅつ 利用 りよう 微細 びさい 素子 そし 配線 はいせん 組 く 立 た 大量 たいりょう 生産 せいさん #製造 せいぞう 工程 こうてい )、現在 げんざい コンピュータ や電子 でんし 機器 きき 支 ささ 主要 しゅよう 技術 ぎじゅつ 一 ひと

実際 じっさい 集積 しゅうせき 回路 かいろ 考案 こうあん レーダー 科学 かがく 者 しゃ ジェフリー・ダマー (1909年 ねん 生 う 彼 かれ イギリス国防省 こくぼうしょう の王立 おうりつ 施設 しせつ 働 はたら 年 ねん 月 がつ 日 にち 公表 こうひょう 年 ねん 回路 かいろ 作 つく 失敗 しっぱい 各 かく 企業 きぎょう 集積 しゅうせき 回路 かいろ 実現 じつげん 目指 めざ RCA のマイクロモジュール、ウェスティングハウス・エレクトリック のモレキュラーエレクトロニクス、テキサス・インスツルメンツ のソリッドステートサーキットが開発 かいはつ [ 1]

初期 しょき 集積 しゅうせき 回路 かいろ 概念 がいねん 後 のち 近 ちか 概念 がいねん 基板 きばん 真空 しんくう 蒸着 じょうちゃく 抵抗 ていこう 素子 そし コンデンサ を形成 けいせい トランジスタ と組 く 合 あ 薄膜 うすまく 集積 しゅうせき 回路 かいろ 現在 げんざい プリンテッドエレクトロニクス に相当 そうとう 印刷 いんさつ 技術 ぎじゅつ 抵抗 ていこう 配線 はいせん 枚 まい 基板 きばん 上 じょう 集積 しゅうせき 厚 あつし 膜 まく 集積 しゅうせき 回路 かいろ 開発 かいはつ [ 1]

また、1958年 ねん ウェスティングハウス から「Molectronics」という名称 めいしょう 集積 しゅうせき 回路 かいろ 概念 がいねん 発表 はっぴょう [ 2] 年 ねん 月 がつ 誌 し 掲載 けいさい 記事 きじ 触発 しょくはつ 電気 でんき 試験 しけん 所 しょ 同年 どうねん 月 がつ 見方 みかた 次第 しだい 構造 こうぞう 個 こ 約 やく cm 角 かく 樹脂 じゅし 容器 ようき 平行 へいこう 配列 はいれつ 集積 しゅうせき 回路 かいろ 試作 しさく 成功 せいこう [ 3] [ 4]

1961年 ねん 月 がつ 技術 ぎじゅつ 提携 ていけい 三菱電機 みつびしでんき 種類 しゅるい 発表 はっぴょう [ 1] 日本 にっぽん 最初 さいしょ 集積 しゅうせき 回路 かいろ 東京大学 とうきょうだいがく 日本電気 にほんでんき 共同 きょうどう 開発 かいはつ [ 5]

著名 ちょめい 集積 しゅうせき 回路 かいろ 特許 とっきょ アメリカ合衆国 あめりかがっしゅうこく 別々 べつべつ 企業 きぎょう 2人 ふたり 研究 けんきゅう 者 しゃ 異 こと 発明 はつめい 発行 はっこう テキサス・インスツルメンツ のジャック・キルビー の特許 とっきょ 年 ねん 月 がつ 出願 しゅつがん 年 ねん 月 がつ 特許 とっきょ アメリカ合衆国 あめりかがっしゅうこく 特許 とっきょ 第 だい 号 ごう フェアチャイルドセミコンダクター のロバート・ノイス の特許 とっきょ 年 ねん 月 がつ 出願 しゅつがん 年 ねん 月 がつ 特許 とっきょ アメリカ合衆国 あめりかがっしゅうこく 特許 とっきょ 第 だい 号 ごう キルビー特許 とっきょ 紛争 ふんそう 呼 よ 特許 とっきょ 対 たい 特許 とっきょ 特許 とっきょ 呼 よ 多 おお 議論 ぎろん 発生 はっせい

技術 ぎじゅつ 的 てき 内容 ないよう 無関係 むかんけい 業界 ぎょうかい 権益 けんえき 争 あらそ 特許 とっきょ 優先 ゆうせん 権 けん 委員 いいん 会 かい 特許 とっきょ 集積 しゅうせき 回路 かいろ 特許 とっきょ 有効 ゆうこう 法的 ほうてき 認定 にんてい 争 あらそ 勃発 ぼっぱつ 技術 ぎじゅつ 的 てき 判断 はんだん 目的 もくてき 法的 ほうてき 有効 ゆうこう 認 みと 目的 もくてき 特許 とっきょ 出願 しゅつがん 年 ねん 月 げつ 経 へ 決着 けっちゃく 勝利 しょうり 確定 かくてい 法的 ほうてき 勝利 しょうり 実際 じっさい 意味 いみ

ライセンスビジネス的 てき 年 ねん テキサス・インスツルメンツ とフェアチャイルドセミコンダクター を含 ふく 十 じゅう 数 すう 社 しゃ 企業 きぎょう 集積 しゅうせき 回路 かいろ 供与 きょうよ 合意 ごうい 達 たっ 技術 ぎじゅつ 法律 ほうりつ 教訓 きょうくん 的 てき 事例 じれい 日本 にっぽん 年 ねん 紆余曲折 うよきょくせつ 経 へ 年 ねん 特許 とっきょ 莫大 ばくだい 額 がく 請求 せいきゅう 等 とう 伴 ともな 紛争 ふんそう サブマリン特許 とっきょ 制度 せいど 」のタチの悪 わる 際立 きわだ 役割 やくわり 担 にな 結果 けっか

キルビーとノイスは後 のち アメリカ国家 こっか 技術 ぎじゅつ 賞 しょう を受 う 全米 ぜんべい 発明 はつめい 家 か 殿堂 でんどう 入 い

SSI, MSI, LSI というのは、集積 しゅうせき 素子 そし 数 かず 分類 ぶんるい 定義 ていぎ [ 6] 言 い 今日 きょう 使 つか 比較的 ひかくてき 小規模 しょうきぼ 単 たん 比較的 ひかくてき 大 だい 規模 きぼ 単 たん 現在 げんざい 同義 どうぎ 語 ご 使 つか 多 おお

初期 しょき 集積 しゅうせき 回路 かいろ 集積 しゅうせき 後 のち 語 かたり 同時 どうじ 作 つく 思 おも レトロニム であろう。航空 こうくう 宇宙 うちゅう 分野 ぶんや 珍重 ちんちょう 発展 はってん ミニットマンミサイル とアポロ計画 けいかく は慣性 かんせい 航法 こうほう 用 よう 計算 けいさん 機 き 軽量 けいりょう 必要 ひつよう アポロ誘導 ゆうどう は集積 しゅうせき 回路 かいろ 技術 ぎじゅつ 進化 しんか 寄与 きよ 量産 りょうさん 化 か 技術 ぎじゅつ 向上 こうじょう 寄与 きよ 計画 けいかく 年 ねん 年 ねん 生産 せいさん 全 すべ 買 か 取 と 製造 せいぞう 技術 ぎじゅつ 向上 こうじょう 製品 せいひん 価格 かかく 分 ぶん 以外 いがい 需要 じゅよう 生 う

民生 みんせい 品 ひん 大量 たいりょう 需要 じゅよう 発生 はっせい 電卓 でんたく メインフレーム )でのICの採用 さいよう System/360 では単体 たんたい 集積 しゅうせき 集積 しゅうせき 回路 かいろ 呼 よ 集積 しゅうせき 回路 かいろ 採用 さいよう System/370 からであった。

1960年代 ねんだい 最初 さいしょ 製品 せいひん 汎用 はんよう 多 た 品種 ひんしゅ 大量 たいりょう 作 つく 大量 たいりょう 使用 しよう 製品 せいひん 家電 かでん 大量 たいりょう 生産 せいさん 機器 きき 使 つか 年代 ねんだい マイクロプロセッサ が現 あらわ

集積 しゅうせき 度 ど 高 たか 普通 ふつう 生産 せいさん 分類 ぶんるい 曖昧 あいまい 比較的 ひかくてき 複雑 ふくざつ 汎用 はんよう 比較的 ひかくてき 単純 たんじゅん 大雑把 おおざっぱ 呼 よ 分 わ 程度 ていど 分類 ぶんるい

もとの分類 ぶんるい 全 すべ 入 はい 年代 ねんだい 開発 かいはつ 始 はじ 大 だい 規模 きぼ 集積 しゅうせき 回路 かいろ 多数 たすう 作 つく 匹敵 ひってき 規模 きぼ マイクロプロセッサ が製作 せいさく 年 ねん 最初 さいしょ Mbit RAM が登場 とうじょう 万 まん 集積 しゅうせき 年 ねん 最初 さいしょ Pentium には約 やく 万 まん 個 こ 集積 しゅうせき 設計 せっけい 化 か 以前 いぜん 比較 ひかく 設計 せっけい 容易 ようい

また、カーバー・ミード とリン・コンウェイ の『超 ちょう 入門 にゅうもん [ 7] 設計 せっけい 手法 しゅほう 提案 ていあん en:Mead & Conway revolution )と呼 よ 影響 えいきょう 年代 ねんだい 大学 だいがく 最先端 さいせんたん 実際 じっさい 建造 けんぞう 年 ねん 頃 ごろ 以降 いこう 点 てん 現実 げんじつ 的 てき CAD きゃど 等 とう 助 たす 設計 せっけい 化 か 手法 しゅほう 大学 だいがく 最先端 さいせんたん 実際 じっさい 研究 けんきゅう 可能 かのう 変化 へんか 齎 もたら 一 いち 例 れい 初期 しょき RISC として、IBM 801 、バークレイRISC(SPARC への影響 えいきょう 大 おお 系 けい MIPS がまず挙 あ 後者 こうしゃ 影響 えいきょう

VLSIに続 つづ 新 あら 語 かたり 作 つく 集積 しゅうせき 素子 そし 数 すう 万 まん 以上 いじょう 万 まん 以上 いじょう 集積 しゅうせき 度 ど 集積 しゅうせき 回路 かいろ 今日 きょう 普通 ふつう

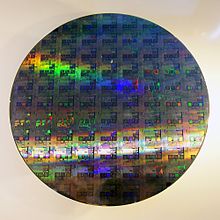

WSI (Wafer-Scale Integration) は、複数 ふくすう 等 とう 全体 ぜんたい 上 じょう 作 つく 込 こ 個別 こべつ 切 き 離 はな 大 おお 使用 しよう 構想 こうそう [ 注釈 ちゅうしゃく ] 現状 げんじょう 品 ひん 非常 ひじょう 高額 こうがく 良 よ 特殊 とくしゅ 用途 ようと 特殊 とくしゅ 要求 ようきゅう 基 もと 生産 せいさん 装置 そうち 採用 さいよう 人工 じんこう 衛星 えいせい 天体 てんたい 観測 かんそく 望遠鏡 ぼうえんきょう 光学 こうがく 受像 じゅぞう 素子 そし 合 あ 作 つく 歪 ゆが 隙間 すきま 生 しょう 枚 まい 全面 ぜんめん 使用 しよう 物 もの 作 つく

System-on-a-chip (SoC) は、従来 じゅうらい 別々 べつべつ 構成 こうせい 統合 とうごう 独立 どくりつ 動作 どうさ 全体 ぜんたい 集積 しゅうせき 回路 かいろ 上 じょう 実現 じつげん 例 たと 周辺 しゅうへん 機器 きき 集積 しゅうせき

集積 しゅうせき 回路 かいろ 技術 ぎじゅつ 進歩 しんぽ 一 いち 例 れい 以前 いぜん 撮像 さつぞう 管 かん 呼 よ 真空 しんくう 管 かん 映像 えいぞう 撮影 さつえい 撮像 さつぞう 素子 そし 電荷 でんか 結合 けつごう 素子 そし 技術 ぎじゅつ 開発 かいはつ 進 すす 固体 こたい 撮像 さつぞう 素子 そし CCDイメージセンサ が作 つく 家庭 かてい 用 よう 大幅 おおはば 小型 こがた 化 か 貢献 こうけん 続 つづ CMOSイメージセンサ も作 つく 静止 せいし 写真 しゃしん 用 よう 十分 じゅうぶん 解像度 かいぞうど 持 も デジタルカメラ が銀 ぎん 塩 しお 一掃 いっそう

伸縮 しんしゅく 折 お 畳 たた 可能 かのう 集積 しゅうせき 回路 かいろ [ 編集 へんしゅう ] このシステムは、単 たん 結晶 けっしょう 硅素 けいそ 無機 むき 整列 せいれつ 含 ふく 無機 むき 電子 でんし 材料 ざいりょう 極 きょく 薄 うす 基板 きばん 統合 とうごう [ 8]

半導体 はんどうたい 製造 せいぞう ウェハー 上 うえ 回路 かいろ 形成 けいせい 前 ぜん 工程 こうてい 作 つく 切断 せつだん 搭載 とうさい 後 のち 最終 さいしゅう 検査 けんさ 行 おこな 後 のち 工程 こうてい 大 おお 二分 にぶん 工程 こうてい 一般 いっぱん 複数 ふくすう 工程 こうてい 専門 せんもん 企業 きぎょう 工場 こうじょう 順次 じゅんじ 行 い 社 しゃ 工程 こうてい 行 おこな 非常 ひじょう 稀 まれ

一般 いっぱん 的 てき 設計 せっけい 製造 せいぞう 表面 ひょうめん 処理 しょり 回路 かいろ 形成 けいせい 基 もと 材 ざい 製造 せいぞう 各 かく 工程 こうてい 専業 せんぎょう 企業 きぎょう 存在 そんざい 切 き 出 だ 検査 けんさ 前記 ぜんき 分 わ 専業 せんぎょう 化 か 場合 ばあい 加 くわ 各 かく 工程 こうてい 使用 しよう 材料 ざいりょう 加工 かこう 専業 せんぎょう 存在 そんざい 一 ひと 集積 しゅうせき 回路 かいろ 出来上 できあ 関 かか 数 かず 少 すく 多 おお 社 しゃ 言 い

集積 しゅうせき 回路 かいろ 母 はは 材 ざい 原材料 げんざいりょう 半導体 はんどうたい 性質 せいしつ 持 も 物質 ぶっしつ 一般 いっぱん 的 てき 集積 しゅうせき 回路 かいろ シリコン であるが、高周波 こうしゅうは 回路 かいろ 超 ちょう 高速 こうそく 可能 かのう ヒ化 か 、低 てい 電圧 でんあつ 高速 こうそく 回路 かいろ 作 つく ゲルマニウム も利用 りよう

集積 しゅうせき 回路 かいろ 歩留 ぶど 原材料 げんざいりょう 単 たん 結晶 けっしょう 純度 じゅんど 高 たか 結晶 けっしょう 欠陥 けっかん 数 かず 直径 ちょっけい 大 おお 左右 さゆう 年 ねん 末 まつ 現在 げんざい 直径 ちょっけい 達 たっ 引 ひ 上 あ 従来 じゅうらい 技術 ぎじゅつ 欠陥 けっかん 低 ひく 難 むずか 多 おお 揃 そろ 壁 かべ 突 つ 当 あ 時期 じき 単 たん 結晶 けっしょう 引 ひ 上 あ 装置 そうち 超 ちょう 伝導 でんどう 磁石 じしゃく 囲 かこ 溶融 ようゆう 対流 たいりゅう 強力 きょうりょく 磁場 じば 止 と 欠陥 けっかん 少 すく 単 たん 結晶 けっしょう 製造 せいぞう 可能 かのう

前 ぜん 工程 こうてい 回路 かいろ 出来上 できあ 前 ぜん 工程 こうてい 設計 せっけい 者 しゃ 作 つく 回路 かいろ 従 したが 上 じょう 集積 しゅうせき 回路 かいろ 作 つく 込 こ 工程 こうてい 光学 こうがく 技術 ぎじゅつ 精密 せいみつ 加工 かこう 技術 ぎじゅつ 真空 しんくう 技術 ぎじゅつ 統計 とうけい 工学 こうがく 工学 こうがく 無人 むじん 化 か 技術 ぎじゅつ 微細 びさい 繊維 せんい 工学 こうがく 高分子 こうぶんし 化学 かがく 環境 かんきょう 工学 こうがく 多岐 たき 技術 ぎじゅつ 構成 こうせい

集積 しゅうせき 回路 かいろ 半導体 はんどうたい 表面 ひょうめん 各種 かくしゅ 表面 ひょうめん 処理 しょり 複数 ふくすう 実施 じっし 製造 せいぞう 注入 ちゅうにゅう 物質 ぶっしつ 打 う 込 こ 不純物 ふじゅんぶつ 濃度 のうど 高 たか 措置 そち 行 おこな 最初 さいしょ 作 つく 層 そう 集積 しゅうせき 回路 かいろ 中枢 ちゅうすう SOI ではウェハーに絶縁 ぜつえん 層 そう 焼 や 張 は 合 あ 漏 も 電流 でんりゅう 押 お 込 こ 処置 しょち 行 おこな 膜 まく 塗布 とふ 露光 ろこう 現像 げんぞう 処理 しょり 処理 しょり 複数 ふくすう 行 おこな 間 あいだ 回路 かいろ 構造 こうぞう 物 ぶつ 母体 ぼたい 堆積 たいせき イオン注入 ちゅうにゅう によるドープ物質 ぶっしつ 注入 ちゅうにゅう 配線 はいせん 土台 どだい 絶縁 ぜつえん 膜 まく 生成 せいせい 金属 きんぞく 配線 はいせん 不要 ふよう 部分 ぶぶん 除去 じょきょ 行 おこな フォトリソグラフィ )。集積 しゅうせき 回路 かいろ 立体 りったい 的 てき 複雑 ふくざつ 配線 はいせん 層 そう 枚数 まいすう 数 かぞ 層 そう 層 そう 等 とう 表現 ひょうげん 表面 ひょうめん 処理 しょり 技術 ぎじゅつ 現在進行形 げんざいしんこうけい 年 ねん 現在 げんざい High-K絶縁 ぜつえん 膜 まく 、添加 てんか 物 ぶつ 打 う 込 こ 窒化物 ぶつ 半導体 はんどうたい 素子 そし 新 あら 技術 ぎじゅつ 導入 どうにゅう 新 あたら 技術 ぎじゅつ 微細 びさい 化 か 共 とも 世 よ 出 で 言 い

半導体 はんどうたい 工場 こうじょう 生産 せいさん 自体 じたい 巨大 きょだい クリーンルーム となっている。生物 せいぶつ 学 がく 的 てき 半導体 はんどうたい 製造 せいぞう 現場 げんば 遥 はる 清浄 せいじょう 度 ど 高 たか 上 じょう 細菌 さいきん 細胞 さいぼう 個 こ 近 ちか 覆 おお 隠 かく 年 ねん 先端 せんたん nm は、ウイルス 以下 いか 大 おお 製造 せいぞう 中 ちゅう 半導体 はんどうたい 人間 にんげん 環境 かんきょう ナトリウム に大変 たいへん 弱 よわ 絶縁 ぜつえん 膜 まく 浸透 しんとう 特 とく CMOS トランジスタには致命 ちめい 的 てき 欠陥 けっかん

半導体 はんどうたい 工場 こうじょう 内 ない 導入 どうにゅう 空気 くうき 部屋 へや 場所 ばしょ 設定 せってい 度 ど 応 おう 何 なん 度 ど HEPAフィルター やULPAフィルター で、空中 くうちゅう 微粒子 びりゅうし 濾 こ 使 つか 水 みず イオン交換 こうかん 樹脂 じゅし とフィルターによって、空気 くうき 同様 どうよう 水中 すいちゅう 微粒子 びりゅうし 徹底的 てっていてき 除去 じょきょ 超 ちょう 純 じゅん 水 みず 使用 しよう

大量 たいりょう 含 ふく 皮膚 ひふ 大量 たいりょう 角質 かくしつ 細胞 さいぼう 破片 はへん 落下 らっか 振動 しんどう ヒト は、半導体 はんどうたい 害 がい 以外 いがい 何 なに 物 ぶつ 宇宙 うちゅう 服 ふく 着 き 製造 せいぞう 汚染 おせん 工場 こうじょう 高度 こうど 自動 じどう 化 か 人間 にんげん 製造 せいぞう 出向 でむ 機械 きかい 故障 こしょう 時 とき

ウェハー上 じょう 回路 かいろ 形成 けいせい 完了 かんりょう 半導体 はんどうたい 試験 しけん 装置 そうち 用 もち 回路 かいろ 正常 せいじょう 機能 きのう 確認 かくにん 行 おこな 半導体 はんどうたい 動作 どうさ 特性 とくせい 温度 おんど 左右 さゆう 常温 じょうおん 加 くわ 高温 こうおん 低温 ていおん 下 か 試験 しけん 行 おこな

ウェハーテストの結果 けっか 後述 こうじゅつ 後 のち 工程 こうてい 良品 りょうひん 組 く 立 た 対象 たいしょう

ダイ面積 めんせき 大 おお 超 ちょう 大 だい 規模 きぼ 集積 しゅうせき 回路 かいろ 上 じょう 一 ひと 欠陥 けっかん 完璧 かんぺき 製品 せいひん 作 つく 非常 ひじょう 難 むずか 設計 せっけい 段階 だんかい 予備 よび 回路 かいろ 前 まえ 追加 ついか 不良 ふりょう 検出 けんしゅつ 予備 よび 回路 かいろ 補 おぎな 歩留 ぶど 上 あ 救済 きゅうさい 行 おこな 回路 かいろ 切 き 替 か 回路 かいろ 上 じょう 形成 けいせい 中 ちゅう 電流 でんりゅう 流 なが 切断 せつだん 実現 じつげん

DRAM やフラッシュメモリ では、製品 せいひん 決 き 容量 ようりょう 加 くわ 予備 よび 領域 りょういき 用意 ようい 不良 ふりょう 箇所 かしょ 見 み 時点 じてん 配線 はいせん 切 き 予備 よび 領域 りょういき 切 き 替 か 一般 いっぱん 的 てき 行 おこな 各 かく 内部 ないぶ 不良 ふりょう 場合 ばあい 切 き 離 はな 中 ちゅう 低 てい 製品 せいひん 最初 さいしょ 全 すべ 機能 きのう 期待 きたい 手法 しゅほう 例 たと Cell プロセッサはSynergistic Processor Element ( シナジスティック・プロセッサー・エレメント ) 個 こ 用意 ようい 機 き PlayStation 3 では、使用 しよう 可能 かのう 個 こ 設定 せってい 不良 ふりょう 一 ひと 発生 はっせい 利用 りよう 可能 かのう

ダイシング工程 こうてい 切 き 出 だ 前 ぜん 工程 こうてい 良品 りょうひん 回路 かいろ 切 き 出 だ 貼 は 付 づ 搭載 とうさい 端子 たんし 配線 はいせん 樹脂 じゅし 封 ふう 止 よ 最終 さいしゅう 製品 せいひん 形 かたち 後 ご 初期 しょき 不良 ふりょう 出 だ 試験 しけん 製品 せいひん 機能 きのう 確認 かくにん 経 へ 出荷 しゅっか

ダイシング工程 こうてい 前 ぜん 工程 こうてい 製造 せいぞう 形 かたち 切 き 離 はな 薄 うす 砥石 といし 用 もち 切断 せつだん 方法 ほうほう 用 もち 方法 ほうほう 主流 しゅりゅう

ワイヤーボンディングの図 ず 端子 たんし 端子 たんし 接続 せつぞく フリップチップボンディングの図 ず 上 うえ 浮 う 丸 まる 突起 とっき 下 した 取 と 付 つ 基板 きばん 並 なら 四角 よつかど 部分 ぶぶん 接合 せつごう 面 めん チップをパッケージ基板 きばん 搭載 とうさい 側 がわ 端子 たんし 端子 たんし 接続 せつぞく 工程 こうてい 呼 よ 主 おも 手法 しゅほう 下 した 示 しめ

チップ上 じょう 接続 せつぞく 端子 たんし 端子 たんし 細 ほそ 金属 きんぞく 線 せん 接続 せつぞく 方法 ほうほう 加工 かこう 容易 たやす 電気 でんき 抵抗 ていこう 低 ひく 材質 ざいしつ 金 きむ アルミニウム がよく用 もち チップ上 じょう 呼 よ 接続 せつぞく 用 よう 突起 とっき 載 の 面 めん 基板 きばん 合 あ 接続 せつぞく 方法 ほうほう 全面 ぜんめん 接続 せつぞく 使 つか 端子 たんし 数 すう 多 おお 面積 めんせき 小 ちい 集積 しゅうせき 回路 かいろ 利用 りよう ボンディングによる配線 はいせん 完了 かんりょう 外部 がいぶ 衝撃 しょうげき 水分 すいぶん 集積 しゅうせき 回路 かいろ 保護 ほご 封 ふう 止 とめ 行 おこな 一般 いっぱん 的 てき 集積 しゅうせき 回路 かいろ モールド剤 ざい でチップやボンディングワイヤーを保護 ほご 注入 ちゅうにゅう 成形 せいけい 行 おこな 集積 しゅうせき 回路 かいろ 黒 くろ 外見 がいけん 樹脂 じゅし 樹脂 じゅし 固 かた 後 のち 毎 ごと 切 き 離 はな 集積 しゅうせき 回路 かいろ 完成 かんせい 近年 きんねん CPU やGPU 、液晶 えきしょう 超 ちょう 精密 せいみつ 集積 しゅうせき 回路 かいろ 剤 ざい 用 もち アンダーフィル と呼 よ 一 いち 液 えき 硬化 こうか 樹脂 じゅし 用 もち 後 のち 基 もと 材 ざい 間 あいだ 注入 ちゅうにゅう 行 おこな 炉 ろ 呼 よ 装置 そうち 硬化 こうか

バスタブカーブのグラフ。不良 ふりょう 発生 はっせい 示 しめ 青 あお 初期 しょき 不良 ふりょう 期間 きかん 高 こう 故障 こしょう 率 りつ 経 へ 偶発 ぐうはつ 故障 こしょう 期間 きかん 移行 いこう 様子 ようす 示 しめ 集積 しゅうせき 回路 かいろ 故障 こしょう 率 りつ 一般 いっぱん 的 てき バスタブカーブ と呼 よ 確 かく 率 りつ 分布 ぶんぷ 従 したが 使用 しよう 開始 かいし 直後 ちょくご 高 たか 不良 ふりょう 率 りつ 示 しめ 初期 しょき 不良 ふりょう 期間 きかん 経 へ 低 ひく 不良 ふりょう 率 りつ 維持 いじ 偶発 ぐうはつ 故障 こしょう 期間 きかん 移行 いこう 劣化 れっか 加速 かそく 条件下 じょうけんか 短時間 たんじかん 集積 しゅうせき 回路 かいろ 動作 どうさ 初期 しょき 不良 ふりょう 出 だ 工程 こうてい 焼入 やきい エイジング とも)である。バーンインであぶり出 だ 初期 しょき 不良 ふりょう 次 つぎ 品質 ひんしつ 検査 けんさ 取 と 除 のぞ

具体 ぐたい 的 てき 高温 こうおん 下 か 一定 いってい 時間 じかん 集積 しゅうせき 回路 かいろ 電流 でんりゅう 流 なが 劣化 れっか 加速 かそく 劣化 れっか 化学 かがく 反応 はんのう 捉 とら 場合 ばあい 劣化 れっか 速度 そくど 温度 おんど アレニウスの式 しき の関係 かんけい 従 したが 考 かんが 方 かた

最後 さいご 集積 しゅうせき 回路 かいろ 製品 せいひん 正常 せいじょう 機能 きのう 確認 かくにん 検査 けんさ 行 おこな 封 ふう 止 とめ 樹脂 じゅし 欠 か BGAパッケージ のボール端子 たんし 異常 いじょう 無 な 確認 かくにん 外観 がいかん 検査 けんさ 電気 でんき 接続 せつぞく 確実 かくじつ 行 おこな 完全 かんぜん 動作 どうさ 半導体 はんどうたい 検査 けんさ 装置 そうち 確認 かくにん 電気 でんき 検査 けんさ 行 おこな

EEPROM やフラッシュメモリ などの記憶 きおく 素子 そし 混載 こんさい 製品 せいひん 書 か 込 こ 作業 さぎょう 行 おこな 内容 ないよう 切 き 替 か 同一 どういつ 異 こと 入出 いりで 端子 たんし 異 こと 集積 しゅうせき 回路 かいろ 作 つく 出 だ 等 とう 製品 せいひん 実際 じっさい 動作 どうさ 可能 かのう 最高 さいこう 速度 そくど 応 おう 倍率 ばいりつ 後処理 あとしょり 設定 せってい 異 こと 製品 せいひん 同 どう 一 いち 生産 せいさん 製造 せいぞう

プロセス・ルールとは、集積 しゅうせき 回路 かいろ 製造 せいぞう 条件 じょうけん 最小 さいしょう 加工 かこう 寸法 すんぽう 用 もち 表 あらわ 回路 かいろ 設計 せっけい 素子 そし 配線 はいせん 寸法 すんぽう 規定 きてい 決 き

通常 つうじょう 最小 さいしょう 加工 かこう 寸法 すんぽう 配線 はいせん 幅 はば 間隔 かんかく 配線 はいせん 幅 はば 狭 せま 金属 きんぞく 酸化 さんか 物 ぶつ 電界 でんかい 効果 こうか 長 ちょう 短 みじか 間隔 かんかく 短 みじか 抵抗 ていこう 小 ちい 駆動 くどう 電流 でんりゅう 大 おお 高速 こうそく 動作 どうさ 期待 きたい 高速 こうそく 化 か 期待 きたい ゲート長 ちょう のことを指 さ 場合 ばあい 特 とく 長 ちょう 配線 はいせん 最小 さいしょう 寸法 すんぽう 使 つか 場合 ばあい 拡散 かくさん 層 そう 層 そう 導通 どうつう 径 みち 最小 さいしょう 加工 かこう 寸法 すんぽう 場合 ばあい 製造 せいぞう 上 じょう 技術 ぎじゅつ 的 てき 高度 こうど 困難 こんなん 示 しめ 指標 しひょう 言 い

プロセス・ルールが半分 はんぶん 外部 がいぶ 配線 はいせん 部 ぶ 除 のぞ 同 おな 面積 めんせき 倍 ばい 配線 はいせん 配置 はいち 同 おな 数 すう -1 倍 ばい 分 ぶん 面積 めんせき 面積 めんせき 分 ぶん 縮小 しゅくしょう 枚 まい 取 と 倍 ばい 歩留 ぶど 改善 かいぜん 多 おお 取 と 素子 そし 小 ちい 長 ちょう 短 みじか 電圧 でんあつ 下 さ 低 てい 電圧 でんあつ 高速 こうそく 動作 どうさ 可能 かのう リーク電流 でんりゅう の問題 もんだい 考 かんが 消費 しょうひ 電力 でんりょく 下 さ 性能 せいのう 向上 こうじょう

伝播 でんぱ 遅延 ちえん

τ たう

{\displaystyle \tau }

次 つぎ 式 しき 表 あらわ 関係 かんけい 従 したが

τ たう =

C

l

o

a

d

V

d

d

T

o

x

L

W

μ みゅー ϵ

(

V

d

d

−

V

t

)

2

{\displaystyle \tau ={\frac {C_{load}V_{dd}T_{ox}L}{W\mu \epsilon (V_{dd}-V_{t})^{2}}}}

τ たう

{\displaystyle \tau }

伝播 でんぱ 遅延 ちえん

C

l

o

a

d

{\displaystyle C_{load}}

負荷 ふか 容量 ようりょう

V

d

d

{\displaystyle V_{dd}}

電源 でんげん 電圧 でんあつ

T

o

x

{\displaystyle T_{ox}}

酸化 さんか 膜 まく 厚 あつ L : ゲート長 ちょう

W : ゲート幅 はば

μ みゅー

{\displaystyle \mu }

移動 いどう 度 ど

ϵ

{\displaystyle \epsilon }

酸化 さんか 膜 まく 誘電 ゆうでん 率 りつ

V

t

{\displaystyle V_{t}}

値 ち 電圧 でんあつ [ 9] プロセス・ルールは、フォトマスク からウェハーに回路 かいろ 転写 てんしゃ 半導体 はんどうたい 露光 ろこう 装置 そうち 光学 こうがく 分解能 ぶんかいのう 工程 こうてい 寸法 すんぽう 変換 へんかん 差 さ 改善 かいぜん 更新 こうしん 将来 しょうらい 予測 よそく ムーアの法則 ほうそく を引用 いんよう 多 おお

半導体 はんどうたい 露光 ろこう 装置 そうち 非常 ひじょう 高 たか 工作 こうさく 精度 せいど 要求 ようきゅう 製造 せいぞう 大 だい 部分 ぶぶん 人間 にんげん 手作業 てさぎょう 行 おこな 載 の 高 たか 水平 すいへい 度 ど 実現 じつげん 非常 ひじょう 細 こま 砥石 といし 職人 しょくにん 磨 みが 上 うえ 乗 の 微細 びさい 上 じょう 転写 てんしゃ 光学 こうがく 系 けい 原子 げんし 単位 たんい 表面 ひょうめん 曲 きょく 率 りつ 修正 しゅうせい 超 ちょう 高 こう 精度 せいど 用 もち

半導体 はんどうたい 露光 ろこう 装置 そうち 社 しゃ 社 しゃ 最先端 さいせんたん 半導体 はんどうたい 共同 きょうどう 次 つぎ 世代 せだい 次々 つぎつぎ 世代 せだい 半導体 はんどうたい 露光 ろこう 装置 そうち 開発 かいはつ 半導体 はんどうたい 向 む 製造 せいぞう 開発 かいはつ 生 う 出 だ 装置 そうち 年 ねん 程度 ていど 後 ご 最先端 さいせんたん 続 つづ 半導体 はんどうたい 量産 りょうさん 購入 こうにゅう 頃 ころ 最先端 さいせんたん 半導体 はんどうたい 先 さき 世代 せだい 試験 しけん 運用 うんよう 循環 じゅんかん 演算 えんざん 飛 ひ 値 ち 普通 ふつう 最先端 さいせんたん 年 ねん 時点 じてん 達 たっ [ 10] 微細 びさい 化 か 進 すす 行 い 予想 よそう [ 11] [ 12] [ 13] 一方 いっぽう フラッシュメモリ のような記憶 きおく 用 よう 半導体 はんどうたい 小刻 こきざ 縮小 しゅくしょう 一般 いっぱん 的 てき 年 ねん 年 ねん 縮小 しゅくしょう 行 おこな 年 ねん 想定 そうてい 製品 せいひん 急激 きゅうげき 低 てい 価格 かかく 化 か 各 かく 新規 しんき 投資 とうし 控 ひか 既存 きそん 設備 せつび 改善 かいぜん 生産 せいさん 性 せい 向上 こうじょう 狙 ねら [ 14] 最先端 さいせんたん 微細 びさい 化 か 要求 ようきゅう 携帯 けいたい 端末 たんまつ 向 む 年 ねん 時点 じてん 製品 せいひん 年 ねん 時点 じてん 製品 せいひん 投入 とうにゅう [ 15]

2015年 ねん 年 ねん 第 だい 世代 せだい 第 だい 世代 せだい 製造 せいぞう 年 ねん 中 ちゅう 実用 じつよう 化 か 実際 じっさい 年 ねん [ 16] 年 ねん 実際 じっさい 年 ねん 予定 よてい [ 17] [ 18]

2015年 ねん 月 がつ 試作 しさく 品 ひん 発表 はっぴょう [ 19] 一 いち 桁 けた 時代 じだい 迎 むか

2016年 ねん 月 がつ 発売 はつばい [ 20]

2016年 ねん 月 がつ 出荷 しゅっか

2020年 ねん 月 がつ TSMC の5 nmプロセスによるApple A14 が出荷 しゅっか [ 21] 微細 びさい 化 か 使 つか 光源 こうげん 波長 はちょう 短 みじか 光 ひかり 回折 かいせつ 干渉 かんしょう 形 かたち 上 じょう 作 つく 像 ぞう 食 く 違 ちが 大 おお 設計 せっけい 通 どお 回路 かいろ 形成 けいせい 問題 もんだい 解決 かいけつ 回路 かいろ 設計 せっけい 光学 こうがく 効果 こうか 織 お 込 こ 光学 こうがく 近接 きんせつ 効果 こうか 補正 ほせい 以下 いか 行 おこな 光学 こうがく 近接 きんせつ 効果 こうか 補正 ほせい EDA による自動 じどう 化 か 普及 ふきゅう

2020年 ねん 頃 ごろ 到達 とうたつ 使 つか 微細 びさい 化 か 限界 げんかい 訪 おとず 推測 すいそく 新 あたら 素材 そざい 構造 こうぞう 研究 けんきゅう 微細 びさい 化 か 頼 たよ 手段 しゅだん 集積 しゅうせき 度 ど 向上 こうじょう 模索 もさく [ 22]

また携帯 けいたい 電話 でんわ 小型 こがた 撮像 さつぞう 素子 そし 都合 つごう 上 じょう 非常 ひじょう 微細 びさい 化 か 使 つか 画素 がそ 密度 みつど 可視 かし 光 こう 波長 はちょう 従来 じゅうらい 方式 ほうしき 役 やく 層 そう 光 ひかり 回折 かいせつ 分光 ぶんこう 行 おこな 物 ぶつ 半導体 はんどうたい 素子 そし 使 つか 分光 ぶんこう 遥 はる 長 なが 可視 かし 光 こう 導 みちび 万 まん 画素 がそ 超 こ 同様 どうよう [ 23]

歩留 ぶど 取 と 全 すべ 対 たい 良品 りょうひん 割合 わりあい 指 さ 呼 よ 用 よう 同 おな 生産 せいさん 同 おな 製造 せいぞう 工程 こうてい 経 へ 製品 せいひん 完成 かんせい 製品 せいひん 後 ご 動作 どうさ 周波数 しゅうはすう 割 わ 振 ふ 下 さ 低 てい 動作 どうさ 良品 りょうひん 見 み 歩留 ぶど 上 あ 結果 けっか

半導体 はんどうたい 故障 こしょう 解析 かいせき 極 きわ 多 おお 素子 そし 集合 しゅうごう 体 たい 集積 しゅうせき 回路 かいろ 於 お 何処 どこ 様 よう 壊 こわ 解析 かいせき 技術 ぎじゅつ 半導体 はんどうたい 試験 しけん 装置 そうち 不 ふ 良品 りょうひん 分 わ 回路 かいろ 何処 どこ 異常 いじょう 分 わ 数 かず 千 せん 万 まん 集積 しゅうせき 回路 かいろ 於 お 一 ひと 一 ひと 試験 しけん 現実 げんじつ 的 てき 以上 いじょう 配線 はいせん 不良 ふりょう 得 え 従 したが 集積 しゅうせき 回路 かいろ 登場 とうじょう 当初 とうしょ 集積 しゅうせき 度 ど 向上 こうじょう 伴 ともな 故障 こしょう 解析 かいせき 技術 ぎじゅつ 進歩 しんぽ

CAN形 がた 内部 ないぶ モノリシック集積 しゅうせき 回路 かいろ 片 へん 抵抗 ていこう 器 き 回路 かいろ 素子 そし 形成 けいせい 素子 そし 間 あいだ アルミニウム などの蒸着 じょうちゃく 配線 はいせん 後 のち 数 かず 十 じゅう 数 すう 角 かく 小片 しょうへん 切 き 出 だ 組 く 立 た 工数 こうすう 少 すく 安価 あんか

シリコン (Si、珪素 けいそ 単 たん 結晶 けっしょう 基板 きばん 上 じょう 平面 へいめん 状 じょう 構成 こうせい 型 がた 発展 はってん 年代 ねんだい 発展 はってん 始 はじ 年代 ねんだい 製造 せいぞう 進歩 しんぽ 高度 こうど 混在 こんざい 回路 かいろ 見 み

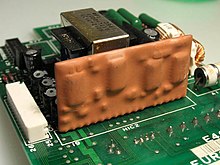

ハイブリッド集積 しゅうせき 回路 かいろ マルチチップモジュール 比較的 ひかくてき 小 ちい 基板 きばん 多数 たすう 個別 こべつ 部品 ぶひん 複数 ふくすう マルチチップモジュール )などを直接 ちょくせつ 高密度 こうみつど 立体 りったい 的 てき 実装 じっそう 配線 はいせん 一体 いったい 部品 ぶひん

制御 せいぎょ 回路 かいろ 一体化 いったいか 大 だい 電力 でんりょく 増幅 ぞうふく 回路 かいろ 回路 かいろ 高密度 こうみつど 実装 じっそう 要求 ようきゅう 携帯 けいたい 機器 きき 自動車 じどうしゃ 航空機 こうくうき 軍事 ぐんじ 用 よう 集積 しゅうせき 回路 かいろ 同士 どうし 距離 きょり 演算 えんざん 速度 そくど 影響 えいきょう 与 あた スーパー・コンピュータ やメインフレーム・コンピュータなどに用 もち 使 つか 層 そう 超 こ 基板 きばん 焼 しょう 結 ゆい 生成 せいせい 非常 ひじょう 高度 こうど 立体 りったい 回路 かいろ 構成 こうせい 基板 きばん 呼 よ 複数 ふくすう 多層 たそう 基板 きばん 貼 は 合 あ 回路 かいろ 構成 こうせい 技術 ぎじゅつ 開発 かいはつ 集積 しゅうせき 回路 かいろ 多層 たそう 化 か 製品 せいひん 基板 きばん 多層 たそう 化 か 製品 せいひん 境目 さかいめ 無 な

IBMのSystem/360 で使 つか 称 しょう 集積 しゅうせき 回路 かいろ 特定 とくてい 用途 ようと 向 む [ 編集 へんしゅう ]

コンピューターに耐 たい 性能 せいのう 与 あた I/Oポート と電源 でんげん 端子 たんし 備 そな 全 すべ 収納 しゅうのう 鍵 かぎ 管理 かんり 鍵 かぎ 登録 とうろく 払 はら 出 だ Worm 機能 きのう 盛 も 込 こ 中 ちゅう 間 あいだ 者 しゃ 攻撃 こうげき サイドチャネル攻撃 こうげき からコンピューターシステムを防御 ぼうぎょ 世界 せかい 最 もっと 多 おお 使 つか ICカード である。システム防衛 ぼうえい 要 よう 使 つか 通常 つうじょう 動作 どうさ 物 もの 無 な バックエンド システムにデータベース を備 そな 鍵 かぎ 格納 かくのう 過去 かこ 実 じつ 格納 かくのう 耐 たい 性 せい 悪 わる B-CAS カード等 とう 限定 げんてい 受信 じゅしん 以外 いがい 撤退 てったい 日本 にっぽん 解析 かいせき 改 かい 限定 げんてい 受信 じゅしん 崩壊 ほうかい おサイフケータイ ・Suica などで知 し 電子 でんし 電子 でんし 発券 はっけん ソニー が開発 かいはつ Felica が主流 しゅりゅう NFC としてISO で標準 ひょうじゅん 化 か 携帯 けいたい 電話 でんわ Microsoft Windows はWindows Vista から、セキュリティチップの本格 ほんかく 採用 さいよう 始 はじ 電子 でんし 証明 しょうめい 書 しょ 格納 かくのう 暗号 あんごう 化 か 以前 いぜん 電子 でんし 署名 しょめい EFS を搭載 とうさい 消滅 しょうめつ 証明 しょうめい 書 しょ 喪失 そうしつ 損失 そんしつ 事故 じこ 全体 ぜんたい 暗号 あんごう 化 か インテル はvPro としてWindows NT にセキュリティチップをオプションで採用 さいよう 暗号 あんごう 化 か 提供 ていきょう 一般 いっぱん 利用 りよう 主 おも 運用 うんよう 大 だい 規模 きぼ

耐 たい 性 せい 技術 ぎじゅつ 日々 ひび 進歩 しんぽ 長 なが 鍵 かぎ 処理 しょり 高性能 こうせいのう 搭載 とうさい 光 ひかり 消去 しょうきょ 取 と 出 だ 困難 こんなん 化 か 光 ひかり 当 あ フローティングゲート から電荷 でんか 流出 りゅうしゅつ 消滅 しょうめつ 改良 かいりょう 重 かさ

^ 専門 せんもん 的 てき 呼 よ ^ 個別 こべつ 部品 ぶひん 集積 しゅうせき 集積 しゅうせき 回路 かいろ 含 ふく 場合 ばあい 言及 げんきゅう 割愛 かつあい ^ 多 おお 場合 ばあい 端子 たんし 数 かず 間隔 かんかく 要因 よういん ^ 1980年代 ねんだい 商用 しょうよう 化 か 例 れい 歩 ふ 留 とめ 制約 せいやく 越 こ 失敗 しっぱい 実用 じつよう 化 か 優先 ゆうせん 度 ど 高 たか トリロジー・システムズ (英語 えいご 版 ばん 記事 きじ 見 み

^ a b c 1960年代 ねんだい 初 はつ 国産 こくさん , http://www.shmj.or.jp/museum2010/exhibi719.htm

^ 城 じょう 阪 ばん 俊吉 しゅんきち 私 わたし 出会 であ 戦後 せんご 年 ねん 年 ねん 巻 かん 号 ごう doi :10.5104/jiep1985.4.2 ^ 米 べい 誌 し 触発 しょくはつ 電 でん 試 ためし , http://www.shmj.or.jp/shimura/ssis_shimura2_06.htm ^ 固体 こたい 回路 かいろ 一 いち 試作 しさく 昭和 しょうわ 年 ねん 月 がつ 日 にち 電気 でんき 四 よん 学会 がっかい 連合 れんごう 大会 たいかい , http://www.shmj.or.jp/shimura/shimura_J_L/shimura2_06_3L.jpg ^ 東大 とうだい 固 かた 態 たい 型 がた 論理 ろんり 回路 かいろ , http://www.shmj.or.jp:80/shimura/ssis_shimura2_07.htm 半導体 はんどうたい 産業 さんぎょう 人 じん 協会 きょうかい 日本 にっぽん 半導体 はんどうたい 歴史 れきし 館 かん 志村 しむら 資料 しりょう 室 しつ 第 だい 部 ぶ ^ The Bipolar Digital Integrated Circuits Data Book , 日本 にほん ^ 原題 げんだい Introduction to VLSI Systems ^ Kim, Dae-Hyeong; Ahn, Jong-Hyun; Choi, Won Mook; Kim, Hoon-Sik; Kim, Tae-Ho; Song, Jizhou; Huang, Yonggang Y.; Liu, Zhuangjian et al. (2008-04-25). “Stretchable and Foldable Silicon Integrated Circuits” (英語 えいご Science 320 (5875): 507–511. doi :10.1126/science.1154367 . ISSN 0036-8075 . https://www.science.org/doi/10.1126/science.1154367 . ^ 福田 ふくだ 哲生 てつお 著 ちょ 半導体 はんどうたい 工業 こうぎょう 調査 ちょうさ 会 かい 年 ねん 月 がつ 日 にち 初版 しょはん 第 だい 刷 さつ 発行 はっこう ISBN 4769312547 ^ 株式会社 かぶしきがいしゃ 年 ねん 月 がつ 日 にち TSMC、5nmプロセス「N5」を2020年 ねん 上半期 かみはんき 立 た 上 あ 予定 よてい 通 どお 年内 ねんない 量産 りょうさん 開始 かいし 見込 みこ ”. PC Watch . 2021年 ねん 月 がつ 日 にち 閲覧 えつらん ^ 株式会社 かぶしきがいしゃ 年 ねん 月 がつ 日 にち TSMC、3 nmプロセスのリスク生産 せいさん 年 ねん 内 ない 開始 かいし ”. PC Watch . 2021年 ねん 月 がつ 日 にち 閲覧 えつらん ^ 株式会社 かぶしきがいしゃ 年 ねん 月 がつ 日 にち Samsung、3 nmプロセスで独自 どくじ 構造 こうぞう 採用 さいよう 年内 ねんない 年 ねん 量産 りょうさん 開始 かいし ”. PC Watch . 2021年 ねん 月 がつ 日 にち 閲覧 えつらん ^ 株式会社 かぶしきがいしゃ 年 ねん 月 がつ 日 にち 【福田 ふくだ 昭 あきら 業界 ぎょうかい 最前線 さいぜんせん 年 ねん 半導体 はんどうたい 前編 ぜんぺん ”. PC Watch . 2021年 ねん 月 がつ 日 にち 閲覧 えつらん ^ 日経 にっけい 年 ねん 日 にち 号 ごう 激 げき 安 やす 活 い ^ 株式会社 かぶしきがいしゃ 年 ねん 月 がつ 日 にち Samsung、業界 ぎょうかい 初 はつ 採用 さいよう 出荷 しゅっか 開始 かいし ”. PC Watch . 2021年 ねん 月 がつ 日 にち 閲覧 えつらん ^ “笠原 かさはら 一輝 いっき 情報 じょうほう 局 きょく 第 だい 世代 せだい 発表 はっぴょう 倍 ばい 倍増 ばいぞう 2021年 ねん 月 がつ 日 にち 閲覧 えつらん 初期 しょき 計画 けいかく 年 ねん 末 まつ 出荷 しゅっか 微細 びさい 化 か 製品 せいひん 計画 けいかく 同 おな 採用 さいよう 立 た 上 あ 結果 けっか 的 てき 事実 じじつ 上 じょう 実際 じっさい 版 ばん 細々 こまごま 出荷 しゅっか 年 ねん 込 こ ^ “笠原 かさはら 一輝 いっき 情報 じょうほう 局 きょく 年 ねん 製品 せいひん 計画 けいかく 延期 えんき 氏 し 新 しん 体制 たいせい 強 つよ 回帰 かいき 閲覧 えつらん 次 つぎ 製造 せいぞう 技術 ぎじゅつ 同 どう 程度 ていど 性能 せいのう 持 も 製造 せいぞう 計画 けいかく 年 ねん 開始 かいし 量産 りょうさん 年 ねん 見 み ^ インテルCPUロードマップ 2016年 ねん 中 ちゅう 量産 りょうさん 年 ねん ASCIIデジタル2016年 ねん 月 がつ 日 にち ^ ついに“ひと桁 けた 開発 かいはつ 加速 かそく EE Times Japan Weekly 2016年 ねん 月 がつ 日 にち ^ “Broadwell-EP”こと「Xeon E5-2600 v4」が販売 はんばい 開始 かいし ASCII 2016年 ねん 月 がつ 日 にち ^ ASCII. “アップル異例 いれい 順番 じゅんばん 入 い 替 か 自前 じまえ 開発 かいはつ 強 つよ 見 み ”. ASCII.jp . 2021年 ねん 月 がつ 日 にち 閲覧 えつらん ^ New nano logic devices for the 2020 time frames ^ マイクロ分光 ぶんこう 素子 そし 用 もち 高 こう 感度 かんど 化 か 技術 ぎじゅつ 開発 かいはつ Panasonic Newsroom プレスリリース 2013年 ねん 月 がつ 日 にち